I1

Изобретение относится к устройст-- вам для управления производственными процессами и может быть использовано Б дискретных системах управления, например, в угольной и горнорудной промьшшенности (управление гидротранспортом шахты, шахтным рельсовым транспортом, водоотливными установками и т.д.),

Цель изобретения - упрощение конструкции устройства, что приведет к повышению его надежности.

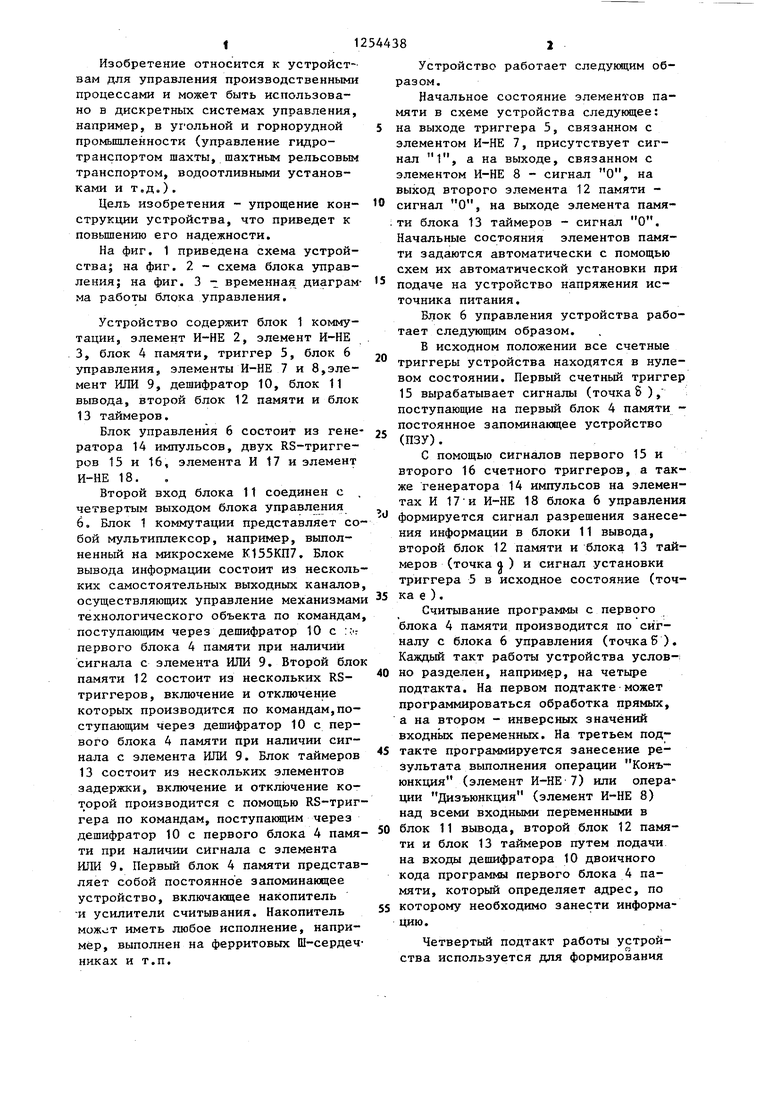

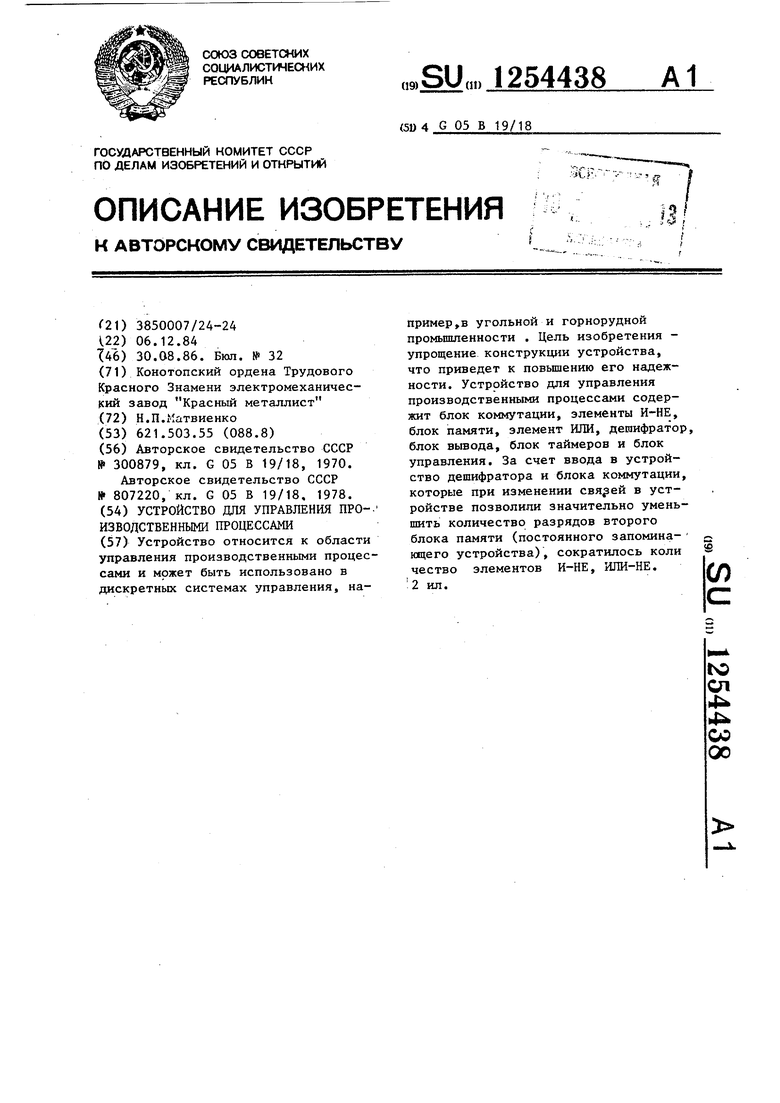

На фиг, 1 приведена схема устрой

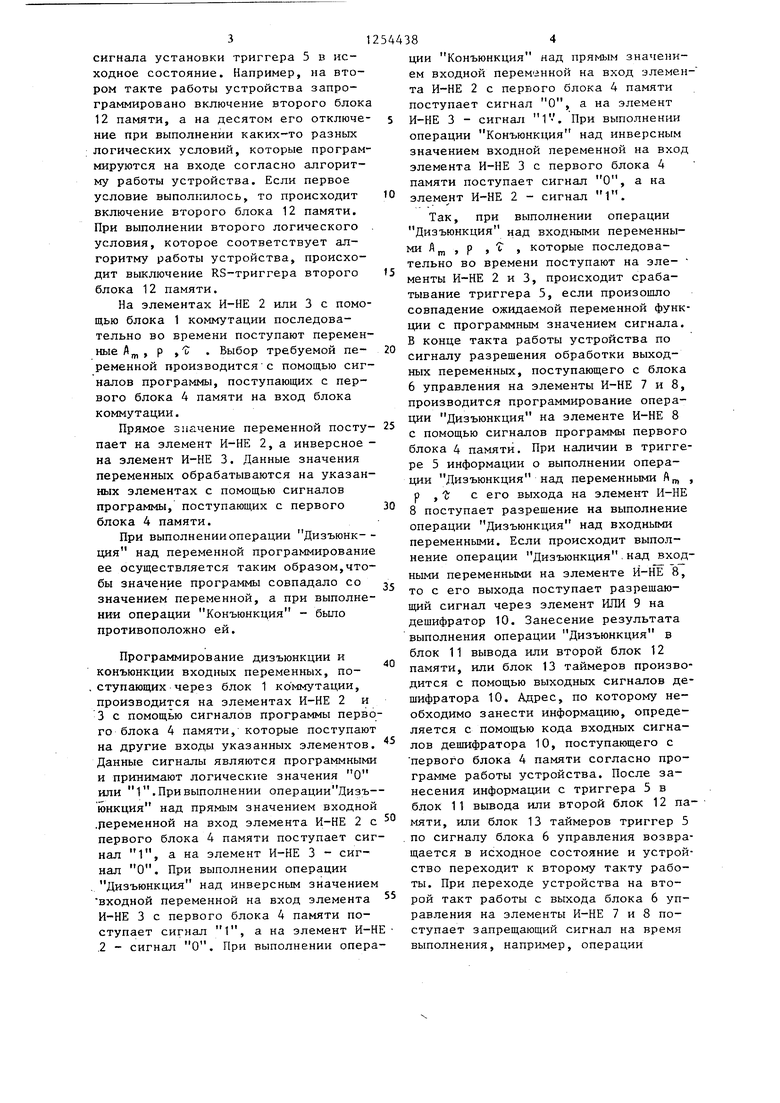

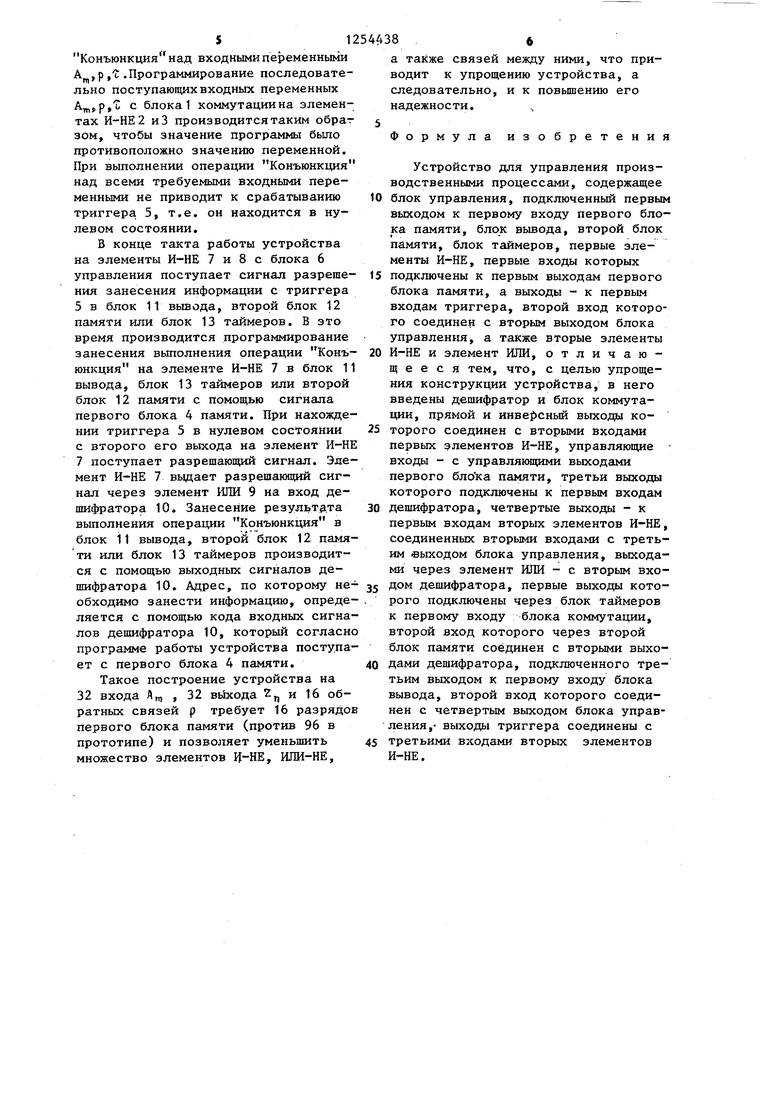

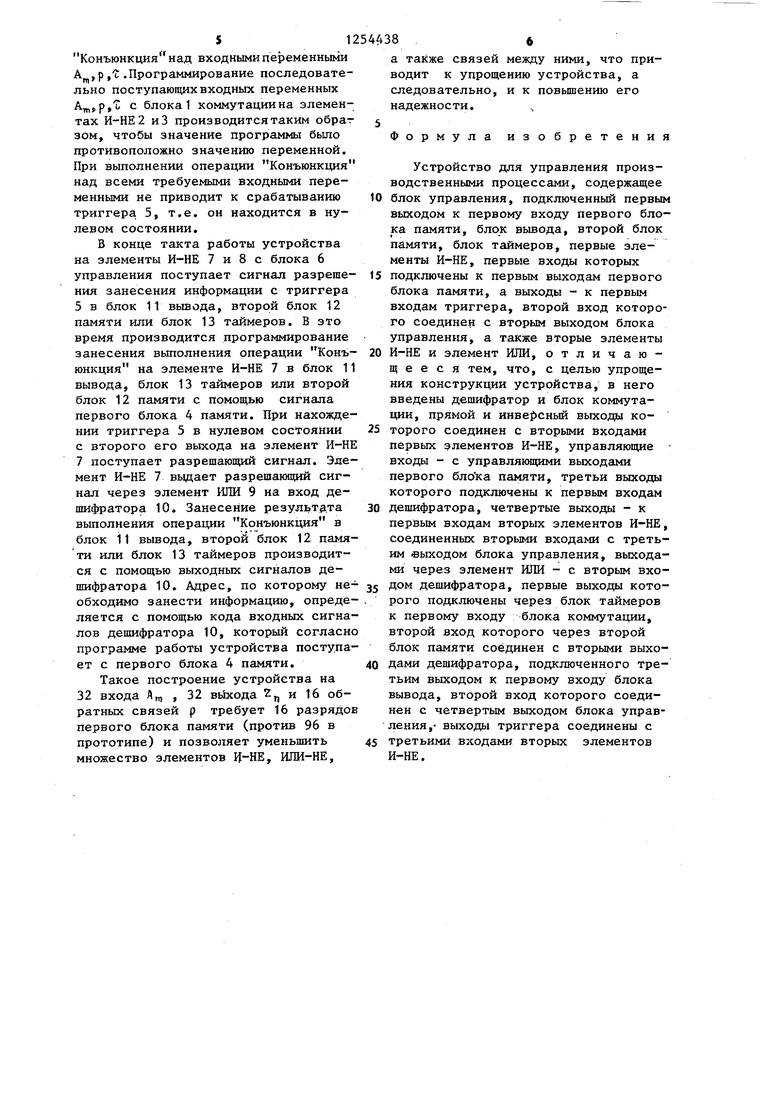

ства; на фиг. 2 - схема блока управления; на фиг. 3 - временная диаграм- 15 ма работы блока управления.

Устройство содержит блок 1 коммутации, элемент И-НЕ 2, элемент И-НЕ 3, блок 4 памяти, триггер 5, блок 6 управления, элементы И-НЕ 7 и 8,элемент ИЛИ 9, дешифратор 10, блок 11 вьгоода, второй блок 12 памяти и блок 13 таймеров.

Блок управления 6 состоит из генератора 14 импульсов, двух RS-тригге- ров 15 и 16, элемента И 17 и элемент И-НЕ 18.

Второй вход блока 11 соединен с . четвертым выходом блока управления 6. Блок 1 коммутации представляет собой мультиплексор, например, выполненный на микросхеме K155KII7. Блок вывода информации состоит из нескольких самостоятельных выходных каналов, осуществляющих управление механизмами технологического объекта по командам, поступающим через дешифратор 10 с :;: первого блока 4 памяти при наличии сигнала с элемента ИЛИ 9. Второй блок памяти 12 состоит из нескольких RS- триггеров, включение и отключение которых производится по командам,поступающим через дешифратор 10 с первого блока 4 памяти при наличии сигнала с элемента ИЛИ 9. Блок таймеров 13 состоит из нескольких элементов

задержки, включение и отключение которой производится с помощью RS-триг- гера по командам, поступакяцим через дешифратор 10 с первого блока 4 памяти при наличии сигнала с элемента ИЛИ 9. Первый блок 4 памяти представляет собой постоянное запоминающее устройство, включающее накопитель -и усилители считывания. Накопитель иметь любое исполнение, напри- мёр, выполнен на ферритовых Ш-сердеч- никах и т.п.

0

5

5

Устройство работает следукщим образом.

Начальное состояние элементов памяти в схеме устройства следукицее: на выходе триггера 5, связанном с элементом И-НЕ 7, присутствует сигнал 1, а на выходе, связанном с элементом И-НЕ 8 - сигнал О, на выход второго элемента 12 памяти - сигнал О, на выходе элемента памяти блока 13 таймеров - сигнал О. Начальные состояния элементов памяти задаются автоматически с помощью схем их автоматической установки при подаче на устройство напряжения источника питания.

Блок 6 управления устройства работает следующим образом.

В исходном положении все счетные триггеры устройства находятся в нулевом состоянии. Первый счетный триггер 15 вырабатывает сигналы (точка 8 ), поступающие на первый блок 4 памяти - постоянное запоминающее устройство (ПЗУ).

С помощью сигналов первого 15 и второго 16 счетного триггеров, а также генератора 14 импульсов на элементах И 17и И-НЕ 18 блока 6 управления формируется сигнал разрешения занесения информации в блоки 11 вывода, второй блок 12 памяти и блока 13 таймеров (точка О и сигнал установки триггера 5 в исходное состояние (точка е ).

Считывание программы с первого блока 4 памяти производится по сигналу с блока 6 управления (точкаб ). Каждый такт работы устройства услов-: но разделен, например, на четыре подтакта. На первом подтакте может программироваться обработка прямых, а на втором - инверсных значений входньк переменных. На третьем под- такте программируется занесение результата выполнения операции Конъюнкция (элемент И-НЕ 7) или операции Дизъюнкция (элемент И-НЕ 8) над всеми входными переменными в 0 блок 11 вывода, второй блок 12 памяти и блок 13 таймеров путем подачи на входы дешифратора 10 двоичного кода программы первого блока 4 памяти, который определяет адрес, по 5 которому необходимо занести информацию.

Четвертый подтакт работы устройства используется для формирования

5

0

5

сигнала установки триггера 5 в исходное состояние. Например, на втором такте работы устройства запрограммировано включение второго блока 12 памяти, а на десятом его отключе- ние при выполнении каких-то разных логических условий, которые программируются на входе согласно алгоритму работы устройства. Если первое условие выполнилось, то происходит включение второго блока 12 памяти. При выполнении второго логического условия, которое соответствует алгоритму работы устройства, происходит выключение RS-триггера второго блока 12 памяти.

На элементах И-НЕ 2 или 3 с помощью блока 1 коммутации последовательно во времени поступают переменные А , f f t . Выбор требуемой пе- ременной производится с помощью сигналов программы, поступающих с первого блока 4 памяти на вход блока коммутации.

Прямое значение переменной посту- пает на элемент И-НЕ 2, а инверсное - на элемент И-НЕ 3. Данные значения переменных обрабатываются на указанных элементах с помощью сигналов программы, поступающих с первого блока 4 памяти.

При выполненииоперации Дизъюнк- ция над переменной программирование ее осуществляется таким образом,чтобы значение программы совпадало со значением переменной, а при выполнении операции Конъюнкция - было противоположно ей.

40

45

Программирование дизъюнкции и конъюнкции входных переменных, поступающих через блок 1 коммутации, производится на элементах И-НЕ 2 и 3 с помощью сигналов программы первого блока 4 памяти, которые поступают на другие входы указанных элементов. Данные сигналы являются программными и принимают логические значения О или 1.При выполнении операции Дизъ- юнкция над прямым значением входной .переменной на вход элемента И-НЕ 2 с первого блока 4 памяти поступает сигнал 1, а на элемент И-НЕ 3 - сиг- нал О. При выполнении операции Дизъюнкция над инверсным значением входной переменной на вход элемента И-НЕ 3 с первого блока 4 памяти поступает сигнал 1, а на элемент И-НЕ .2 - сигнал О. При выполнении операции Конъюнкция над прямым значением входной переменной на вход элемента И-НЕ 2 с первого блока 4 памяти поступает сигнал О, а на элемент И-НЕ 3 - сигнал 1. При выполнении операции Конъюнкция над инверсным значением входной переменной на вход элемента И-НЕ 3 с первого блока 4 памяти поступает сигнал О, а на элеме нт И-НЕ 2 - сигнал 1.

Так, при выполнении операции Дизъюнкция над входными переменными А,

р , V , которые последова

тельно во времени поступают на эле- менты И-НЕ 2 и 3, происходит срабатывание триггера 5, если произошло совпадение ожидаемой переменной функции с программным значением сигнала. В конце такта работы устройства по сигналу разрешения обработки выходных переменных, поступающего с блока 6 управления на элементы И-НЕ 7 и 8, производится программирование операции Дизъюнкция на элементе И-НЕ 8 с помощью сигналов программы первого блока 4 памяти. При наличии в триггере 5 информации о выполнении операции Дизъюнкция над переменными Ар, , р , & с его выхода на элемент И-НЕ 8 поступает разрешение на выполнение операции Дизъюнкция над входными переменными. Если происходит выполнение операции Дизъюнкция,над входными переменными на элементе И-НЕ 8, то с его выхода поступает разрешающий сигнал через элемент ИЛИ 9 на дешифратор 10. Занесение результата выполнения операции Дизъюнкция в блок 11 вывода или второй блок 12 памяти, или блок 13 таймеров производится с помощью выходных сигналов дешифратора 10. Адрес, по которому необходимо занести информацию, определяется с помощью кода входных сигналов дешифратора 10, поступающего с первого блока 4 памяти согласно программе работы устройства. После занесения информации с триггера 5 в блок 11 вывода или второй блок 12 памяти, или блок 13 таймеров триггер 5 по сигналу блока 6 управления возвращается в исходное состояние и устройство переходит к второму такту работы. При переходе устройства на второй такт работы с выхода блока 6 управления на элементы И-НЕ 7 и 8 поступает запрещающий сигнал на время выполнения, например, операции

Конъюнкция над входными переменными А,р , с .Программирование последовательно поступающих входных переменных , i; с блока коммутации на элементах И-НЕ2 иЗ производится таким обраг зон, чтобы значение программы было противоположно значению переменной. При выполнении операции Конъюнкция над всеми требуемыми входными переменными не приводит к срабатыванию триггера. 5, т.е. он находится в нулевом состоянии.

В конце такта работы устройства на элементы И-НЕ 7 и 8 с блока 6 управления поступает сигнал разрешения занесения информации с триггера 5 в блок 11 вьшода, второй блок 12 памяти или блок 13 таймеров. В это время производится программирование занесения выполнения операции Конъюнкция на элементе И-НЕ 7 в блок 11 вывода, блок 13 таймеров или второй блок 12 памяти с помощью сигнала первого блока 4 памяти. При нахождении триггера 5 в нулевом состоянии с второго его выхода на элемент И-НЕ 7 поступает разрешающий сигнал. Элемент И-НЕ 7 выдает разрешающий сигнал через элемент ИЛИ 9 на вход дешифратора 10. Занесение результата вьшолнения операции Конъюнкция в блок 11 вьшода, второй блок 12 памяти или блок 13 таймеров производится с помощью выходных сигналов дешифратора 10. Адрес, по которому необходимо занести информацию, определяется с помощью кода входных сигналов дешифратора 10, который согласно программе работы устройства поступает с первого блока 4 памяти.

Такое построение устройства на 32 входа АП, , 32 выхода 2„ и 16 обратных связей р требует 16 разрядов первого блока памяти (против 96 в прототипе) и позволяет уменьшить множество элементов , ИЛИ-НЕ,

а также связей между ними, что приводит к упрощению устройства, а следовательно, и к повьшгению его надежности.

5

Формула изобретения

Устройство для управления производственными процессами, содержащее 0 блок управления, подключенный первым выходом к первому входу первого блока памяти, блок вьшода, второй блок памяти, блок таймеров, первые элементы И-НЕ, первые входы которых 5 подключены к первым выходам первого блока памяти, а выходы - к первым входам триггера, второй вход которого соединен с вторым выходом блока управления, а также вторые элементы

0 И-НЕ и элемент ИЛИ, отличающееся тем, что, с целью упрощения конструкции устройства, в него введены дешифратор и блок коммутации, прямой и выходы ко5 торого соединен с вторыми входами первых элементов И-НЕ, управляющие входы - с управляющими выходами первого бло ка памяти, третьи выходы которого подключены к первым входам

0 дешифратора, четвертые выходы - к первым входам вторых элементов И-НЕ, соединенных вторыми входами с третьим выходом блока управления, выходами через элемент ИЛИ - с вторым вхо5 дом дешифратора, первые выходы которого подключены через блок таймеров к первому входу : блока коммутации, второй вход которого через второй блок памяти соединен с вторыми выхо0 дами дешифратора, подключенного третьим выходом к первому входу блока вьшода, второй вход которого соединен с четвертым выходом блока управления,- выходы триггера соединены с

5 третьими входами вторых элементов И-НЕ.

Заказ 4718/50 Тираж 836Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления производственными процессами | 1984 |

|

SU1208534A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для управления производ-СТВЕННыМи пРОцЕССАМи | 1978 |

|

SU807220A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2106676C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для реализации логических функций | 1977 |

|

SU732878A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1997 |

|

RU2134442C1 |

| Вычислительное устройство | 1985 |

|

SU1283746A1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

Устройство относится к области управления производственными процессами и может быть использовано в дискретных системах управления, например,в угольной и горнорудной промьшшенности . Цель изобретения - упрощение конструкции устройства, что приведет к повышению его надежности. Устройство для управления производственными процессами содержит блок коммутации, элементы И-НЕ, блок памяти, элемент ИЛИ, дешифратор, блок вьшода, блок таймеров и блок управления. За счет ввода в устройство дешифратора и блока коммутации, которые при изменении свярей в устройстве позволили значительно уменьшить количество разрядов второго блока памяти (постоянного запомина- ющего устройства), сократилось коли чество элементов И-НЕ, ШШ-НЕ. i2 ил. (Л IsD СД 4 4;: 00 00

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ПРОИЗВОДСТВЕННЫМИ ПРОЦЕССАМИ | 0 |

|

SU300879A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для управления производ-СТВЕННыМи пРОцЕССАМи | 1978 |

|

SU807220A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-08-30—Публикация

1984-12-06—Подача