Изобретение относится к электроизмерительной технике и предназначено для цифрового измерения среднеквадратиче- ского значения (СКЗ) переменного напряжения сигналов с большим коэффициентом амплитуды,

Цель изобретения - повышение точности измерений напряжений с большим коэффициентом амплитуды.

Сущность изобретения заключается в предварительном нормировании входного сигнала по амплитуде вновь введенными блоками так, чтобы сигнал, подаваемый на вход линейного преобразователя напряжения переменного тока в постоянное, всегда бы превышал половину шкалы допустимых амплитуд на его входе.

Такое нормирование входного сигнала позволяет проводить измерение СКЗ напряжения в более верхней части диапазона из- мерения, в которой у линейного преобразователя напряжения переменного тока в постоянное гарантируется большее петлевое усиление и большая за счет этого стабильность и точность показаний, большая разрешающая способность.

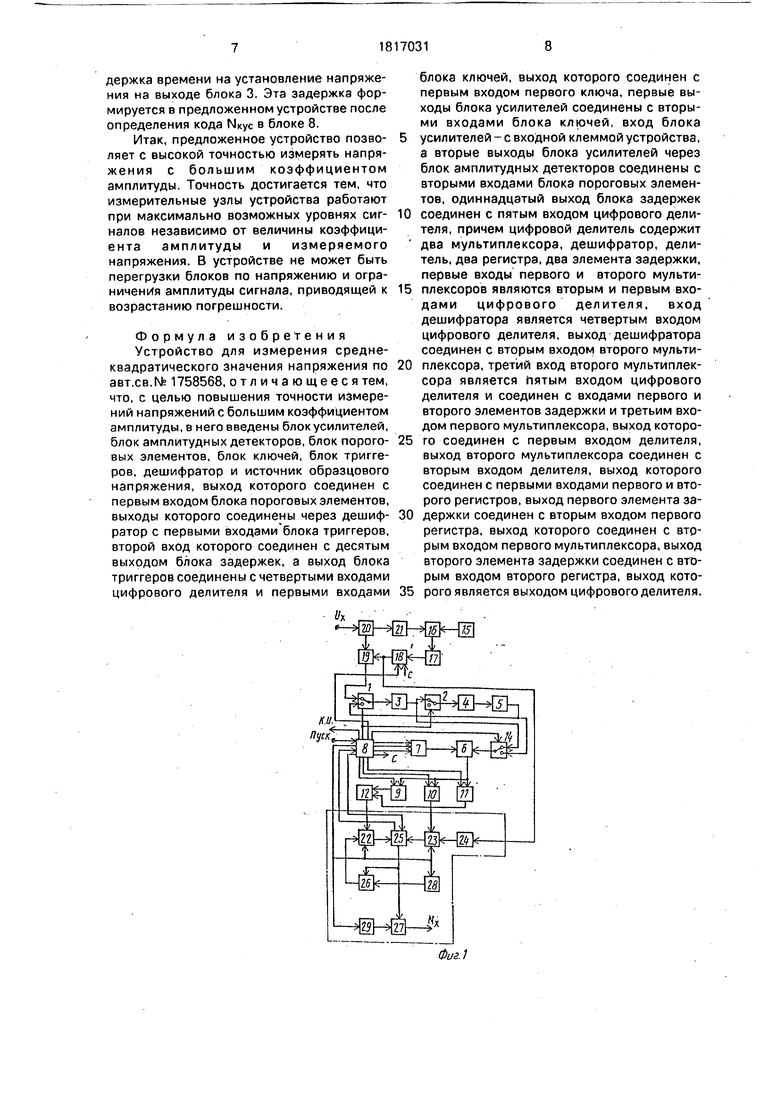

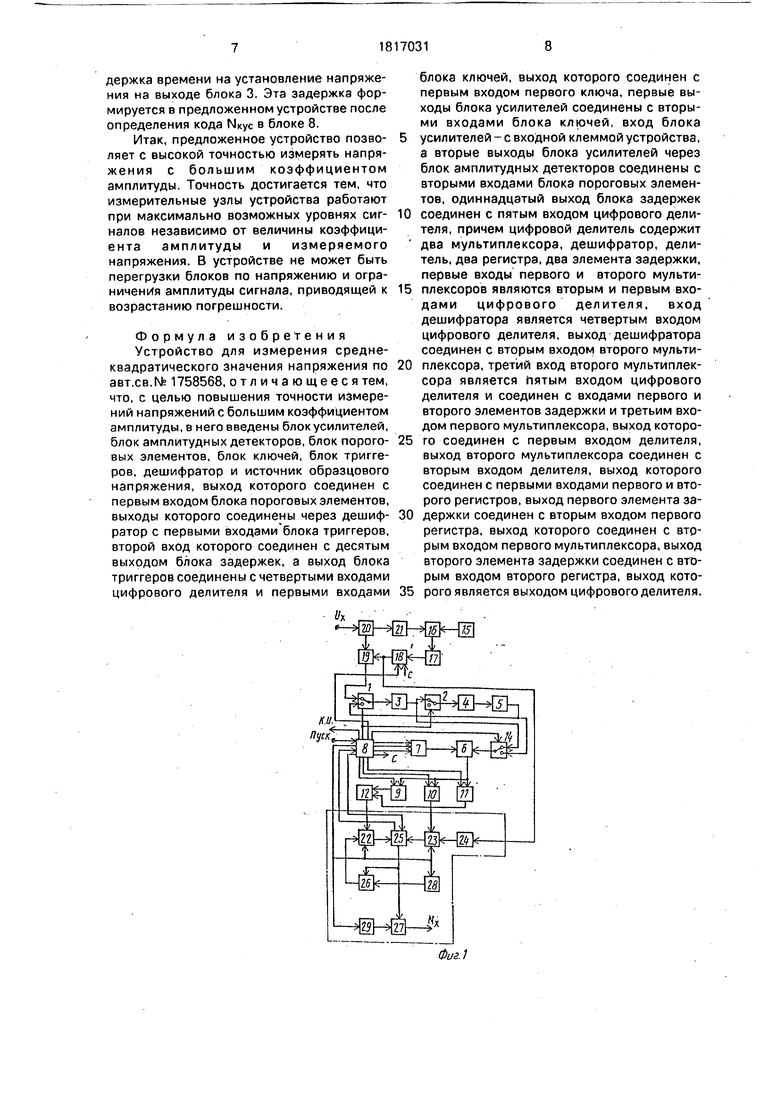

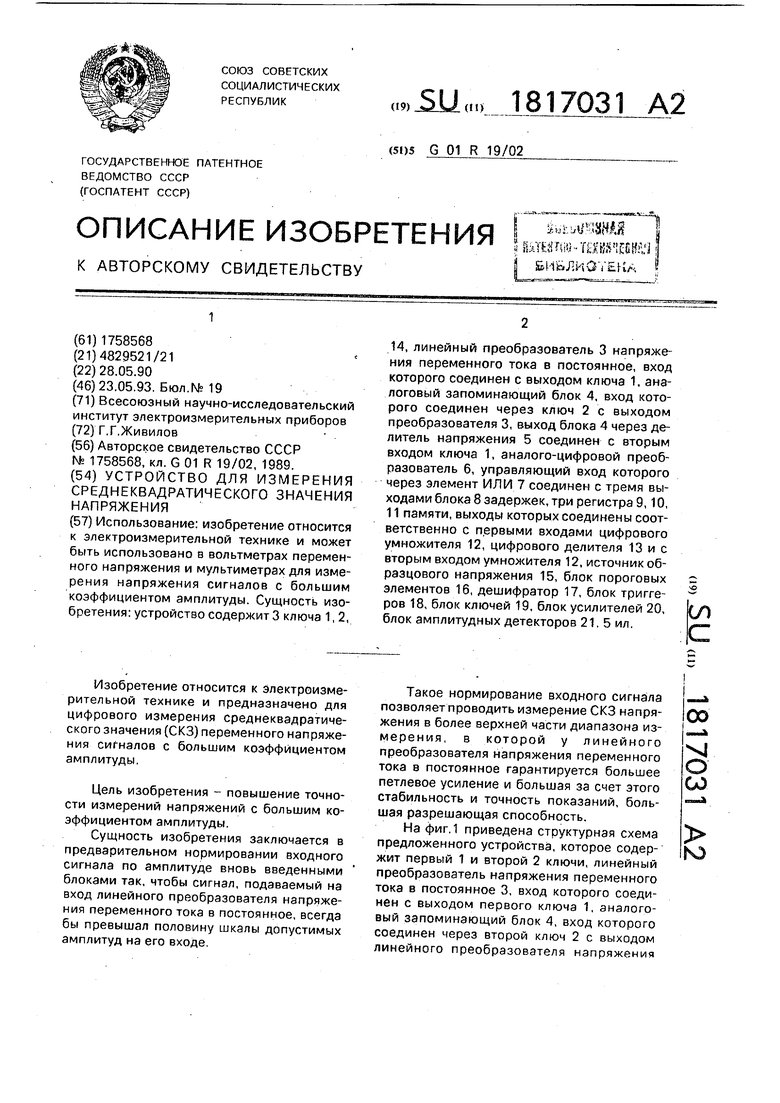

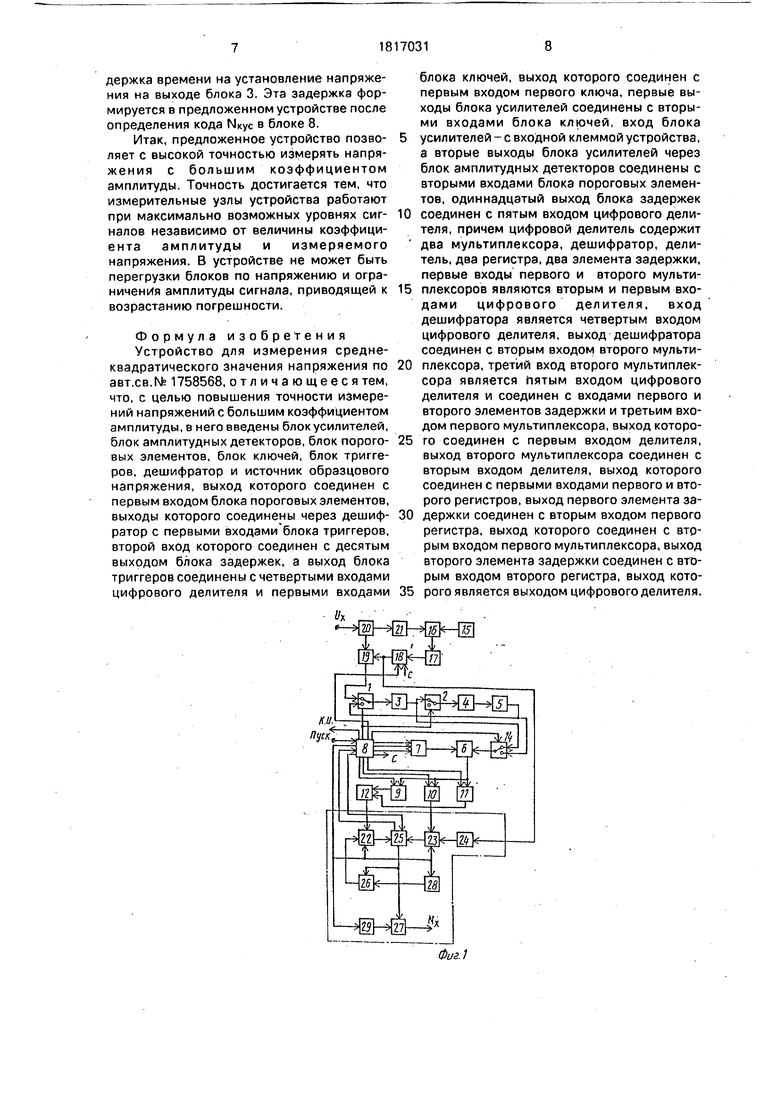

На фиг. 1 приведена структурная схема предложенного устройства, которое содержит первый 1 и второй 2 ключи, линейный преобразователь напряжения переменного тока в постоянное 3, вход которого соединен с выходом первого ключа 1, аналоговый запоминающий блок 4, вход которого соединен через второй ключ 2 с выходом линейного преобразователя напряжения

00

VJ

о ы

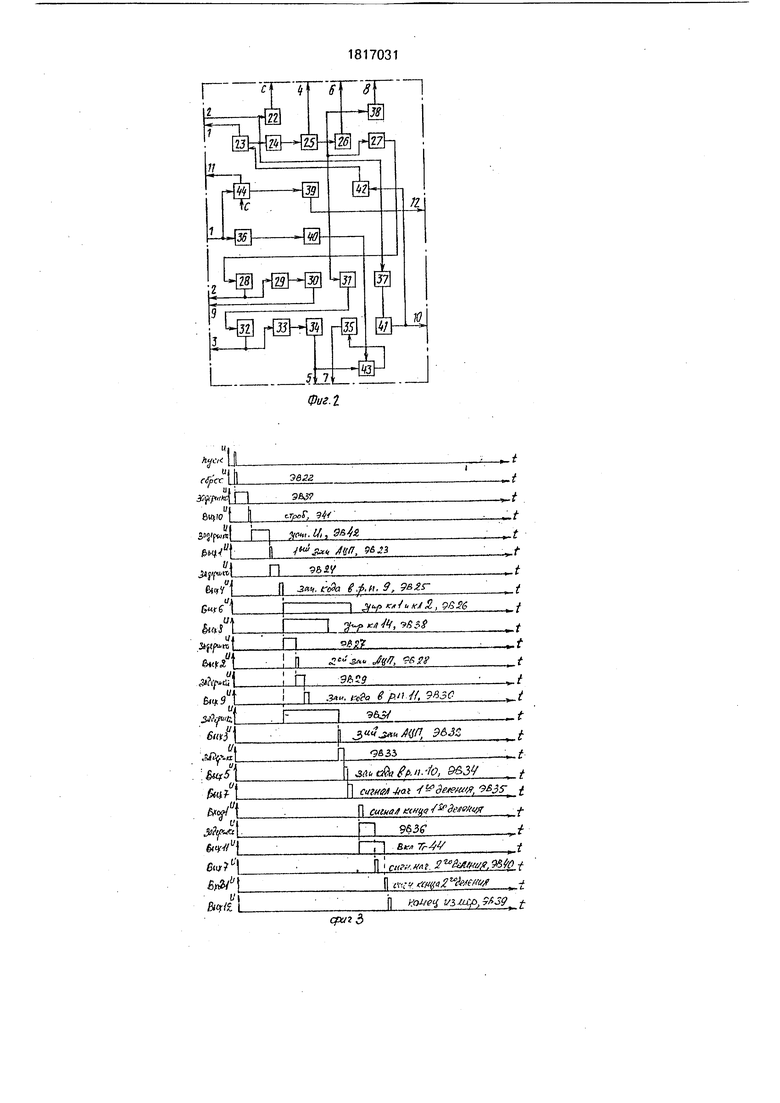

переменного тока в постоянное 3, а выход блока 4 через делитель напряжения 5 соединен с вторым входом первого ключа 1, ана- лого-цифровой преобразователь 6, управляющий вход которого через элемент ИЛИ 7 соединен с первым, вторым и третьим выходами блока задержек 8, первый 9, второй 10 и третий 11 регистры памяти, информационные входы которых соединены с выходом аналого-цифрового преобразователя б, управляющие входы соединены соответственно с четвертым, пятым и девятым выходами блока задержек 8, а выходы регистров памяти 9, 10 и 11 соединены соответ- ственн о с первым входом цифрового умножителя 12, первым входом цифрового делителя 13 и с вторым входом цифрового умножителя 12, входы которого соединены с вторым информационным входом цифрового делителя 13, третий управляющий вход которого соединен с седьмым выходом блока задержек 8, первый выход блока 13 соединен с первым входом блока 8, второй вход которого является входом ПУСК, двенадцатый выход блока задержек 8 соединен с клеммой устройства КОНЕЦ ИЗМЕРЕНИЯ, шестой выход блока задержек 8 соединен с управляющими входами первого 1 и второго 2 ключей, а восьмой выход блока задержек 8 соединен с управляющим входом третьего ключа 14, первый вход которого соединен с выходом блока 3, второй вход - с выходом блока 5, а выход - с входом аналого-цифрового преобразователя 6, источник образцового напряжения 15, выход которого соединен с первым входом блока пороговых элементов 16, выход которого соединен через дешифратор 17 с первым входом блока триггеров 18, второй вход которого соединен с десятым выходом блока задержек 8, а выход блока триггеров 18 соединен с четвертым входом цифрового делителя 13 и первым входом блока ключей 19, выход которого соединен с первым входом первого ключа 1, второй вход блока ключей 19 соединен с первым выходом блока усилителей 20, вход которого соединен с входной клеммой устройства, а выход блока усилителей 20 через блок амплитудных детекторов 21 соединен с вторым входом блока пороговых элементов 16, одиннадцатый выход блока задержек 8 соединен с пятым входом цифрового делителя 13, причем цифровой делитель 13 содержит два мультиплексора 22 и 23, дешифратор 24, делитель 25, два регистра 26 и 27, два элемента задержки 28 и 29, первые входы первого 22 и второго 23 мультиплексоров являются вторым и первым входами цифрового делителя 13, вход дешифратора 24 является четвертым входом

цифрового делителя, выходдешифратора 24 соединен с вторым входом второго мультиплексора 23, третий вход второго мультиплексора 23 является пятым входом

5 цифрового делителя 13 и соединен с входами первого 28 и второго 29 элементов задержки и третьим входом первого мультиплексора 22, выход которого соединен с первым входом делителя 25, выход

10 второго мультиплексора 23 соединен с вторым входом делителя 25, выход которого соединен с первыми входами первого 26 и второго 27 регистров, выход первого элемента задержки 28 соединен с вторым вхо15 дом первого регистра 26, выход которого соединен со вторым входом первого мультиплексора 22, выход второго элемента задержки 29 соединен со вторым входом второго регистра 27, выход которого является выхо20 дом цифрового делителя 13.

Устройство для измерения среднеквад- ратического значения напряжения, представленное на фиг.1, работает следующим образом.

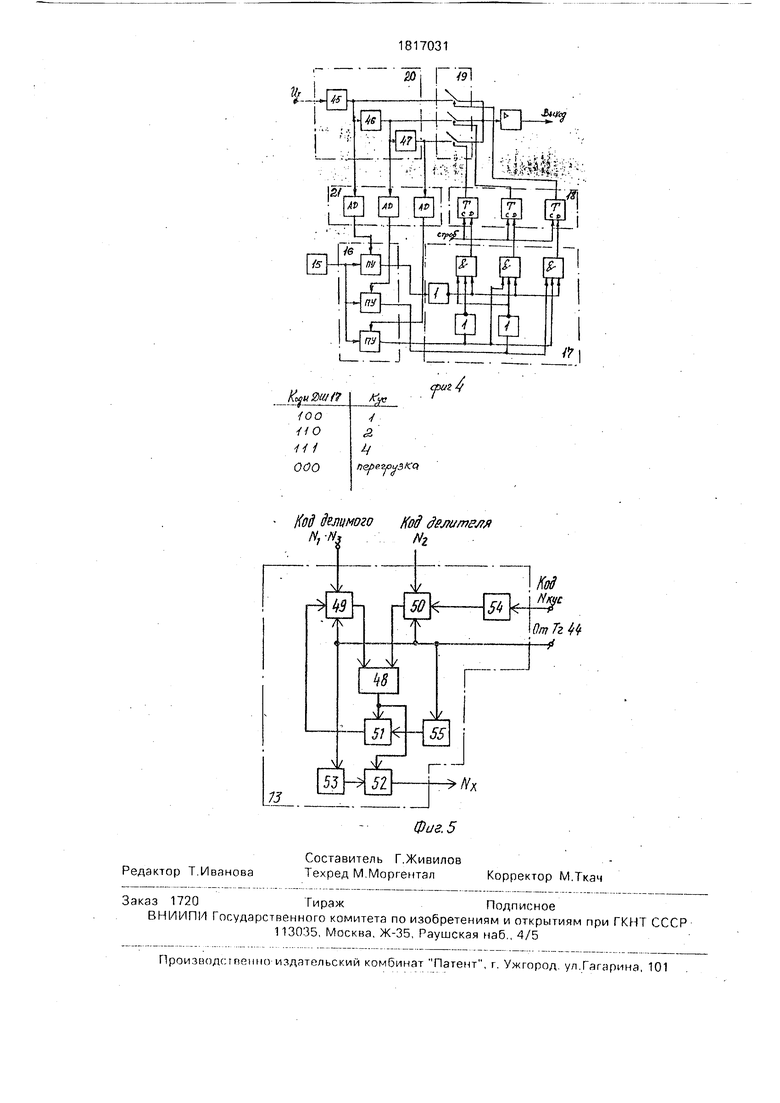

25 На второй вход блока задержек 8 подается сигнал ПУСК, от воздействия которого производится общий сброс и включается задержка в блоке 8 на время нормирования сигнала по амплитуде, в течение которой

30 работают блоки 15...21. Входной сигнал Ux подается на входы усилителей блока 20, а с их выхода на входы амплитудных детекторов 21 и ключей 19. При этом все ключи в блоке 19 заперты. В блоке амплитудных де35 текторов 21 по каждому каналу определяется экстремумы входного сигнала и постоянные напряжения, соответствующие определенным экстремумам, поступают на вторые входы блока пороговых элементов

40 16, а на первые входы блока 16 поступает напряжение, равное максимальному значению амплитуды сигнала на входе, блока 3.

В зависимости от поданного на вход устройства напряжения часть усилителей в

45 блоке 20 может перегрузиться. В работе устройства при измерении 1)х должен участвовать не перегруженный усилитель, выходное напряжение которого по амплитуде будет наибольшим. Для осуществления

50 логической операции определения наибольшего по амплитуде напряжения после блока амплитудных детекторов 21 включены блок пороговых элементов 16, дешифратор 17 и блок триггеров 18, которые работают следу55 ющим образом. В случае, если срабатывают все пороговые элементы в блоке 16 (вход Ux перегружен), дешифратор 17 выдает такой сигнал, что ни один триггер в блоке 18 и ни один ключ в блоке 19 не переключится, а в устройстве может быть зафиксирован сигнал перегрузки входа. В других случаях, когда хотя бы одно пороговое устройство не сработает, дешифратор выделяет канал усиления с наибольшим сигналом, находящимся в линейной области работы.блока 3, и включает один из триггеров в блоке 18 и соответствующий ему ключ в блоке 19.

Коэффициенты усиления Кус каждого канала в блоке 20 известен, и его код NKyc снимается из блока триггеров 18 и подается на четвертый вход блока деления 13, в котором из позиционного декодируется в двоичный. Перед измерением входного сигнала их на входе блока 3 устанавливается напряжение Kyc Ux. От заднего фронта импульса нбрмирования входного сигнала в блоке 8 формируется импульс первого запуска ана- лого-цифрового преобразователя б, который с первого выхода блока 8 через блок 7е поступает в блок 6. При этом в течение первого цикла измерения контакты ключей 1, 2 и 14 находятся в положении, указанном на фиг.1. С задержкой на время аналого-циф- рового преобразования с четвертого выхода блока 8 следует сигнал записи кода NI в первый регистр памяти 9.

В течение времени первого цикла напряжение Ui отслеживается аналоговым запоминающим блоком 4, так как ключ 2 замыкает вход блока 4 с выходом преобразователя 3. Второй цикл измерения начинается с того, что от заднего фронта импульса записи кода в регистр памяти 9 в блоке задержек 8 формируются сигналы.на шестом и восьмом выходах, которые одновременно переключают ключи 1, 2 и 14, При этом блок 4 запоминает напряжение Ui после преобразования напряжения Kyc Ux блоком 3. Из напряжения Ui делителем 5 формируется напряжение Уз, которое подается на входы преобразователей 3 и 6. С второго выхода блока 8 через блок 7 следует сигнал запуска аналого-цифрового преобразователя 6 на преобразование напряжения Уз. С задержкой на время аналого-цифрового преобразования с девятого выхода блока 8 следует сигнал записи кода NS в третий регистр памяти 11. После записи кода NS в регистр памяти 11 на восьмом выходе блока 8 изменяется управляющий потенциал и третий ключ 14 переключателя в исходное положение, подключая на вход блока 6 выходной зажим преобразователя 3.

К этому моменту на выходе преобразователя 3 устанавливается напряжение IJ2. На третьем цикле блок 8 формирует на третьем выходе сигнала запуска аналого- цифрового преобразователя 6, который через блок 7 подается на его управляющий

вход и запускает его. С задержкой на время аналого-цифрового преобразования с пятого выхода блока 8 следует сигнал записи кода N2 во второй регистр памяти 10. Далее

устройство переходит к цифровой обработке результатов измерения,

Цифровой умножитель 12 перемножает коды NI и N3, произведение которых поступает на второй вход цифрового делителя 13

как делимое,

На вход цифрового делителя 13 приходит код N2 в качестве делителя. С одиннадцатого выхода блока задержек 8 на пятый вход цифрового делителя 13 приходит сигнал, который управляет мультиплексорами 22 и 23 так, что на входы делителя 25 приходят коды Мг№ и N2. С выхода 7 блока 8 приходит сигнал деления этих кодов в блок 25 (сигнал приходит на третий вход блока

13). Код результата деления записывается в регистр 26 блока 13 по сигналу с элемента задержки 28, срабатывающего от переднего фронта сигнала переключения мультиплексоров 22 и 23.

От импульса конца первого деления, приходящего из блока 25 с первого выхода блока 13 на первый вход блока задержек 8, формируется сигнал, переключающий мультиплексор 22 и 23 блока 13, которые результат предыдущего деления NiN3/N2 подают в делитель 25 в качестве делимого, а в качестве делителя подается код NKyc с дешифратор ра 24.

С седьмого выхода блока 8 через третий

вход блока 13 на блок 25 приходит сигнал начала деления в результате чего вычисляется результат измерения напряжения Ux

Nx

N1 N3

N

кус

N2

который по сигналу от элемента задержки 29 записывается в регистр 27 блока 13. Код NX поступает с второго выхода блока 13

на выход устройства. Элемент задержки 29 срабатывает от заднего фронта импульса переключения мультиплексоров 22 и 23.

С первого выхода блока 13 на первый вход блока 8 следует импульс окончания

второго деления. От заднего фронта этого импульса формируется сигнал КОНЕЦ ИЗМЕРЕНИЯ, который с двенадцатого выхода блока 8 поступает на выход устройства. Импульс КОНЕЦ ИЗМЕРЕНИЯ сопровождает результат измерения Nx и позволяет записать этот код во внешнее устройство на индикацию и регистрацию. В отличие от основного устройства в предложенном после конца измерения не формируется задержка времени на установление напряжения на выходе блока 3. Эта задержка формируется в предложенном устройстве после определения кода Мкус в блоке 8.

Итак, предложенное устройство позволяет с высокой точностью измерять напряжения с большим коэффициентом амплитуды. Точность достигается тем, что измерительные узлы устройства работают при максимально возможных уровнях сигналов независимо от величины коэффициента амплитуды и измеряемого напряжения. В устройстве не может быть перегрузки блоков по напряжению и огра- ничени-я амплитуды сигнала, приводящей к возрастанию погрешности.

Формула изобретения Устройство для измерения средне- квадратического значения напряжения по авт.св.№ 1758568, отличающееся тем, что, с целью повышения точности измерений напряжений с большим коэффициентом амплитуды, в него введены блок усилителей, блок амплитудных детекторов, блок пороговых элементов, блок ключей, блок триггеров, дешифратор и источник образцового напряжения, выход которого соединен с первым входом блока пороговых элементов, выходы которого соединены через дешифратор с первыми входами блока триггеров, второй вход которого соединен с десятым выходом блока задержек, а выход блока триггеров соединены с четвертыми входами цифрового делителя и первыми входами

блока ключей, выход которого соединен с первым входом первого ключа, первые выходы блока усилителей соединены с вторыми входами блока ключей, вход блока усилителей - с входной клеммой устройства, а вторые выходы блока усилителей через блок амплитудных детекторов соединены с вторыми входами блока пороговых элементов, одиннадцатый выход блока задержек соединен с пятым входом цифрового делителя, причем цифровой делитель содержит два мультиплексора, дешифратор, делитель, два регистра, два элемента задержки, первые входы первого и второго мульти- 5 плексоров являются вторым и первым вхо- дами цифрового делителя, вход дешифратора является четвертым входом цифрового делителя, выход дешифратора соединен с вторым входом второго мульти- 0 плексора, третий вход второго мультиплексора является пятым входом цифрового делителя и соединен с входами первого и второго элементов задержки и третьим входом первого мультиплексора, выход которо- 5 го соединен с первым входом делителя, выход второго мультиплексора соединен с вторым входом делителя, выход которого соединен с первыми входами первого и второго регистров, выход первого элемента за- 30 держки соединен с вторым входом первого регистра, выход которого соединен с вторым входом первого мультиплексора, выход второго элемента задержки соединен с вторым входом второго регистра, выход кото- 35 рого является выходом цифрового делителя.

Ryu.swft

too но

14 1

000

J$Ј

CfXii

4

/

3.

ц

ПелеглиЗКЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения среднеквадратичного значения напряжения | 1989 |

|

SU1758569A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1989 |

|

SU1758570A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1989 |

|

SU1786443A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2012036C1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Цифровой акселерометр | 1984 |

|

SU1242831A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

Использование: изобретение относится к электроизмерительной технике и может быть использовано в вольтметрах переменного напряжения и мультиметрах для измерения напряжения сигналов с большим коэффициентом амплитуды. Сущность изобретения: устройство содержит 3 ключа 1, 2, 14, линейный преобразователь 3 напряжения переменного тока в постоянное, вход которого соединен с выходом ключа 1, аналоговый запоминающий блок 4, вход которого соединен через ключ 2 с выходом преобразователя 3, выход блока 4 через делитель напряжения 5 соединен с вторым входом ключа 1, аналого-цифровой преобразователь 6, управляющий вход которого через элемент ИЛИ 7 соединен с тремя выходами блока 8 задержек, три регистра 9,10, 11 памяти, выходы которых соединены соответственно с первыми входами цифрового умножителя 12, цифрового делителя 13 и с вторым входом умножителя 12, источник образцового напряжения 15, блок пороговых элементов 16, дешифратор 17, блок триггеров 18, блок ключей 19, блок усилителей 20, блок амплитудных детекторов 21.5 ил. ел С

Код делимого Код делителя н,-ЪЪ

| Устройство для измерения среднеквадратического значения напряжения | 1989 |

|

SU1758568A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-05-23—Публикация

1990-05-28—Подача