управляющие и ВЕЖОД которого подключены соответственно к входу кода операции устройстваs выходу адреса следующей микрокоманды блока памяти микрокоманд5ВЬ1Ходу признака безусловного перехода блока памяти микрокоманд, первому входу первого элемента ИЛИ и к информационному входу счетчика адреса, синхровход и вход прибавления 1 которого подклю чены к выходам соответственно перво го и третьего элементов И, первый и второй входы первого элемента И соединены соответственно о первым и вторым входами третьего элемента И, второй вход которогоподключен к выходу первого элемента ИЛИ, вто-ч рой и третий входы которого подключены соответственно к первому управляющему входу коммутатора адреса и к выходу коммутатора меток, управ-

ЛЯЮЩИЙ вход которого подключен к ВЫ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления и диагностирования дис кретных объектов,

Целью изобретения является повышение быстродействия.

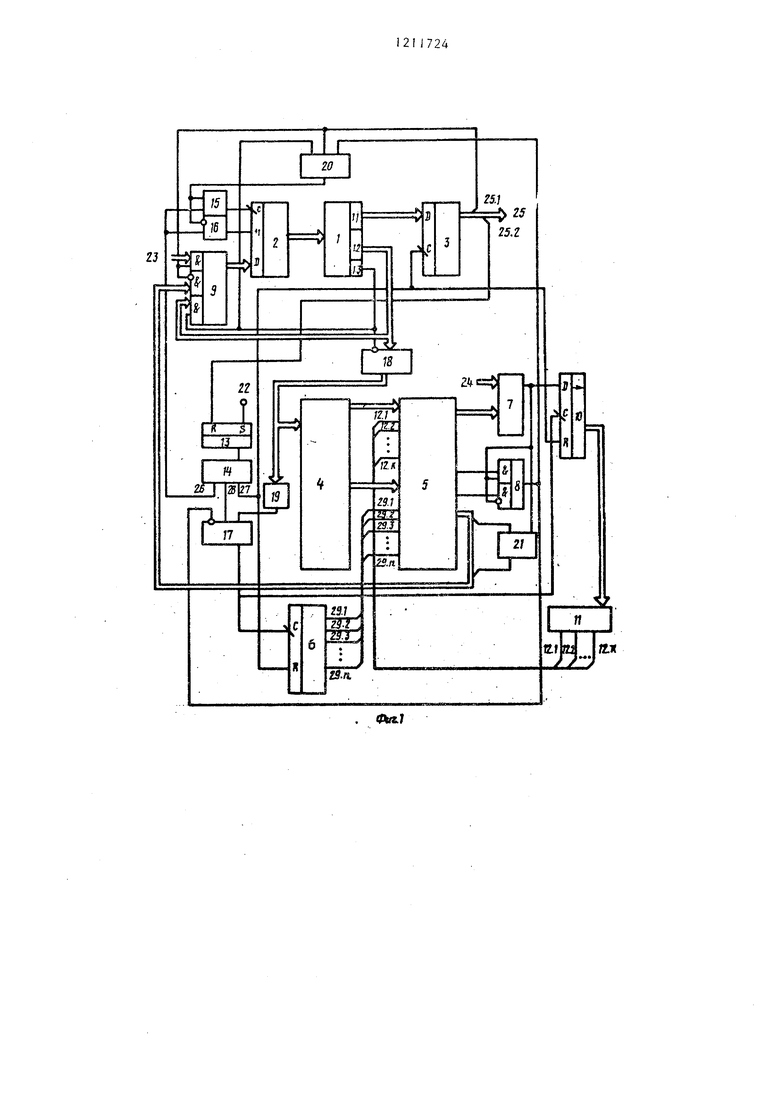

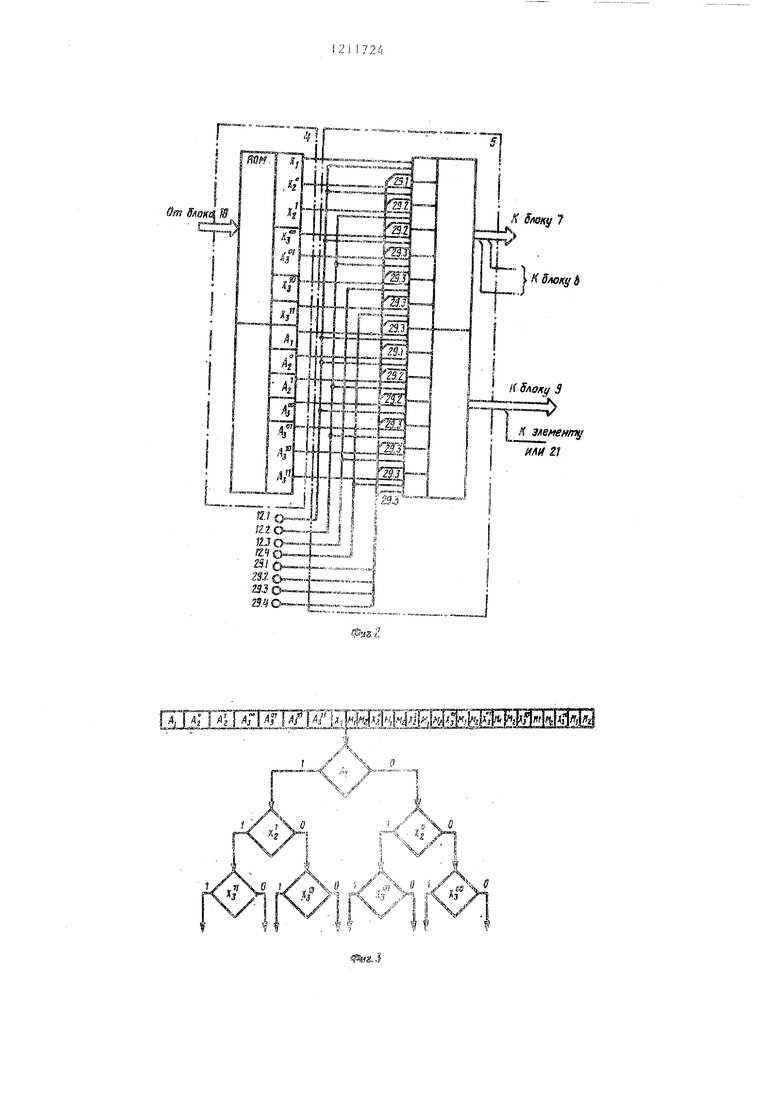

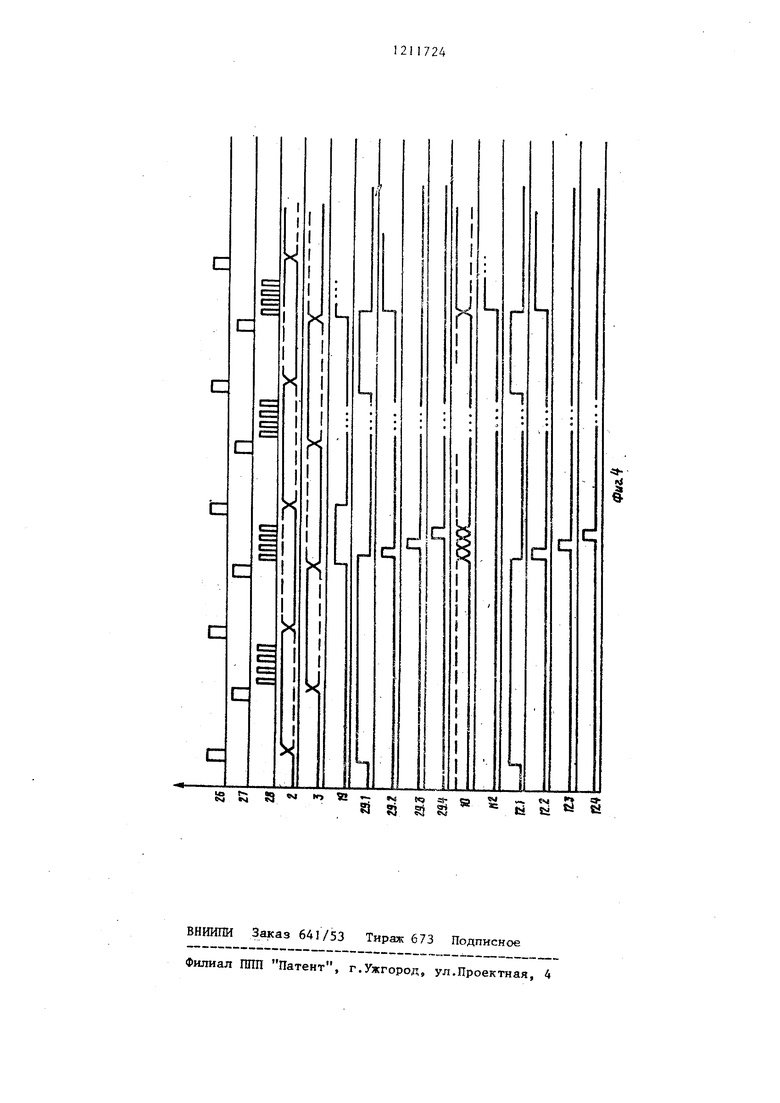

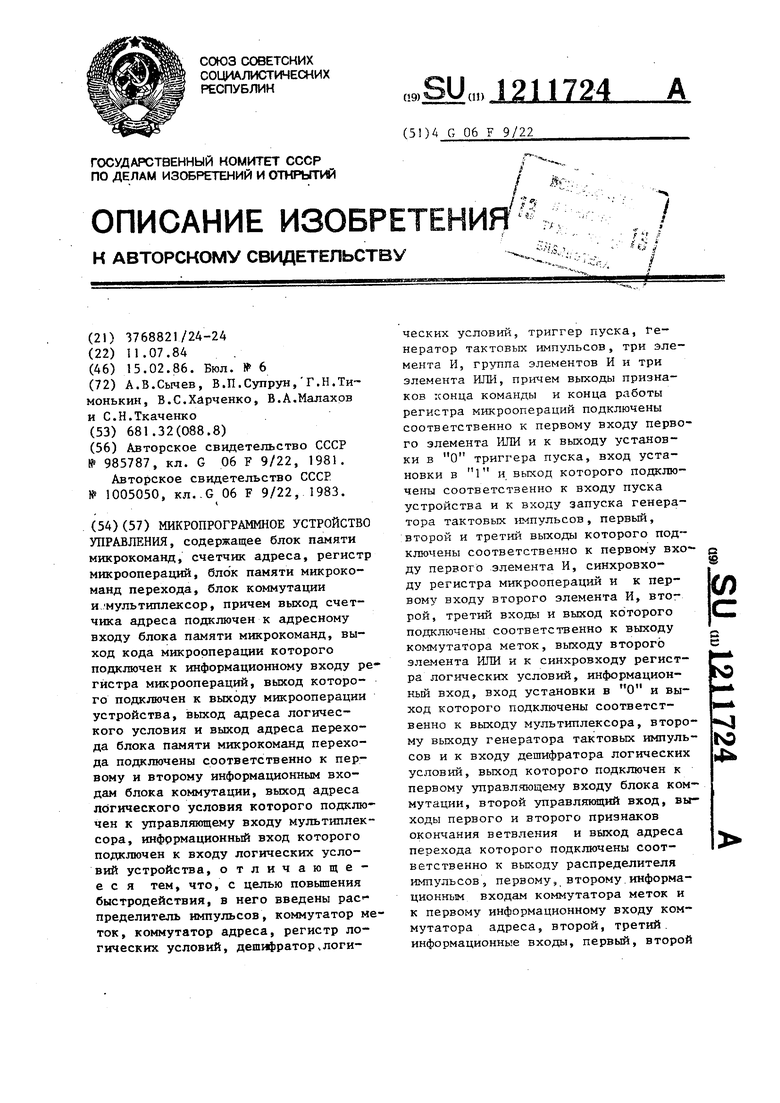

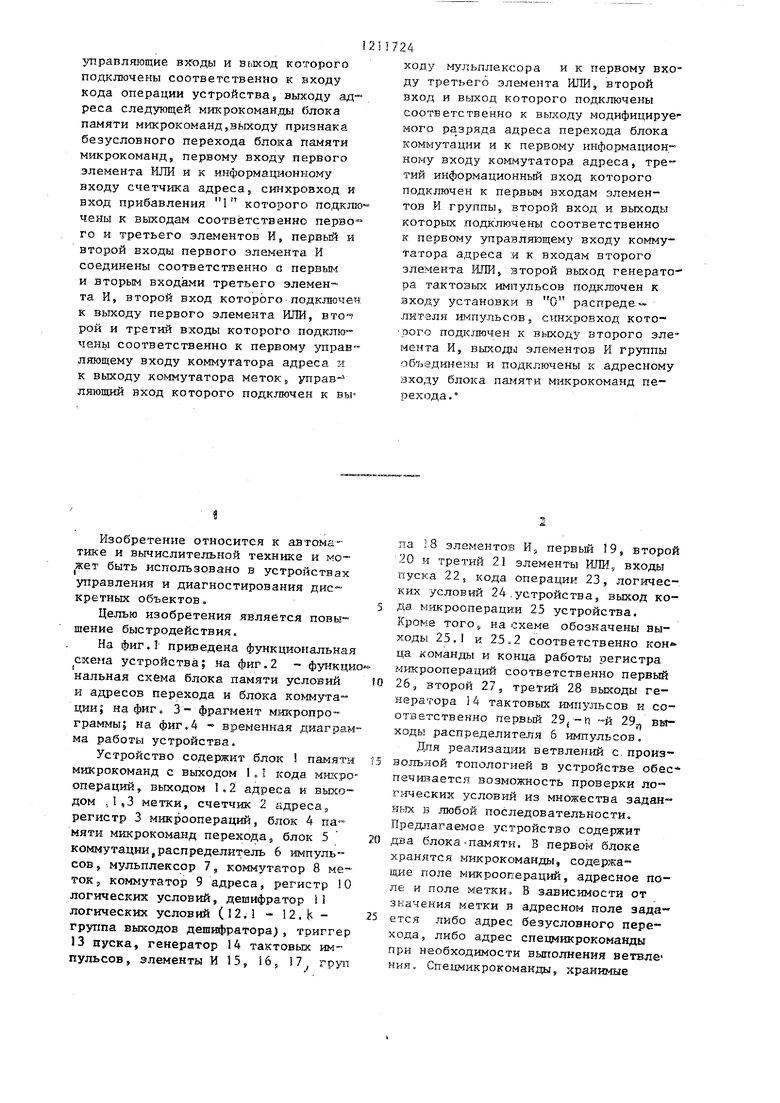

На фиг.Г приведена функциональная схема устройства; на фиг.2 - нальная схема блока памяти условий и адресов перехода и блока коммутации; на фиг 3- фрагмент микропро граммы; на фиг„4 временная диаграмма работы устройства.

Устройство содержит блок 1 памяти микрокоманд с выходом кода мшсро- операций, выходом 1,2 адреса и выходом ,1,3 метки, счетчик 2 адреса регистр 3 микроопераций, блок 4 памяти микрокоманд перехода, блок 5 коммутации,распределитель 6 импульсов J мульплексор 7, коммутатор 8 меток, ком утатор 9 адреса, регистр 0 логических условийj дешифратор 11 логических условий (12,1 - 12, группа выходов дeшяфpaтopa, триггер 13 пуска, генератор 14 тактовых импульсов, элементы И 15, 16s 7, груп

11724

ходу мульплексора и к первому входу третьего элемента ИЛИ, второй вход и выход которого подключены соот-ветственно к выходу модифицируе|- мого разряда адреса перехода блока коммутации и к первому информационному входу коммутатора адреса, тре тий информационный вход которого подключен к первым входам элементов И группыS второй вход и выходы которых подключены соответственно к первому управляющему входу коммутатора адреса и к входам второго элемента ИЛИ, второй выход генератора тактовых импульсов подключен к входу установки в О распреде - лителя Hi inynbcoB,, синхровход кото- рого подключен к вькоду второго элемента И, выходы элементов И группы об ьединены и подключены к адресному входу блока памяти микрокоманд перехода.

па 18 элементов И, первьй 19, второй 20 и третий 21 элементы ИЛИ, входы пуска 22, кода операции 23, логических условий 24.устройства, выход кода микрооперации 25 устройства. Кроме того J на схеме обозначены выходы 25.1 и 25,2 соответственно коно да команды и конца работы регистра микроопераций соответственно первый 26, второй 27, третий 28 выходы генератора 14 тактовых импульсов к соответственно первый 29( -И -и 29 выходы распределителя 6 импульсов,

Для реализации ветвлений с. произвольной топологией в устройстве обес печшзается возможность проверки ло гическик условий из множества заданных в любой последовательности. Предлагаемое устройство содержит два блока-памяти, В первом блоке хранятся микрокоманды, содержащие поле микроопераций, адресное поле и поле метки, В зависимости от значения метки в адресном поле задается либо адрес безусловного перехода, либо адрес спецмикрокоманды при необходимости выполнения ветвле- ПИЯ. Спецмикрокоманды, хранимые

во втором блоке памяти, задают порядок проверки и номера проверяемых логических условий. Для того, чтобы обеспечить вьшолнение произвольных ветвлений, в устройстве реализуется проверка логических условий образующих граф типа дерево.

В формате спецмикрокоманды задаются коды первого логического условия X,, находящегося в вершине дерева, вторых логических условий Х и Х, проверяемых после первого логического условия при X, О и X, I соответственно (логических условий второго уровня), третьих логи

„ ,, ОО ,, 01 -.г 1 -fT

ческих условии X,, Х , Х,, X, , проверяемьсх при Х° О, Х 1 , Х О, Х- I соответственно (логических условий третьего уровня) и т.д., а также коды соответствующих

. t .0 ,1 д 00

им адресов перехода А , А„, А„, А, О д ° г 3

А , , А , А, и т.д.

Разрядность спецмикрокоманд определяется количеством уровней ветвления с максимальным числом последовательно проверяемых условий, количеством различных логических условий и разрядностью адресных частей.

Каждое поле логических условий имеет два разряда-метки, в которых записьшается 1 в случае, если данное условие является последним при его единичном и нулевом значениях соответственно.

Блок 1 памяти микрокоманд предназначен для хранения микрокоманд и имеет три выхода. С выхода 1.1 считываются сигналы микроопераций и поступают на соответствующие информационные входы регистра 3 микроопег- рации. С выхода 1.2 считьтается адрес спецмикрокоманды, в которой предусмотрен анализ условий переходов. По адресу, содержащемуся в этой микрокоманде, на первый и второй информационные входы блока коммутации выбирается информация, содежащая коды проверяемых в данной микрокоманде условий и соответствующие им адреса переходов. С выхода 1.3 считьшается единичная метка при выполнении микрокоманд безусловного перехода (по адресу). В этом случае содержимое поля 1.2 интерпретируется как адрес безусловного перехода.

Генератор 14 тактовых импульсов предназначен для формирования

1724

последователькостей тактовых импульсов. На выходах 26 и 27 формир тот- ся последовательности, сдвинутые одна относительно другой на время 5 записи в счетчик 2 адреса очередной микрокоманда и выборки микрокоманды из блока 1 памяти микрокоманд. На выходе 28 формируется последовательность импульсов, управляю0 щая проверкой логических условий. Блок 4 памяти предназначен для хранения и вьщачи кодов адреса проверяемых логических условий и соответствующих ш- адресов перехо5 да.

Устройство работает следующим образом.

В исходном состоянии все элемен- Tbi схемы находятся в нулевом состояQ НИИ, а в разряде регистра 3 микроопераций, соответств к щем микрооперации Конец команды (выход 25.1), записана и на первом выходе 29.1 распределителя 6 присутствует еди-

5 ничный сигнал. Также единичный сигнал присутствует на выходе 12.1 дешифратора 11. Цепи приведения схемы в исходное состояние условно не показаны. По сигналу Пуск, поступаюп1ему через вход 22 устройства на вход триггера 13, последний устанавливается Б един гчное состояние. При этом iHa выходах генератора 14 возбуждаются последовательности тактовых им- л пульсов.

Первый тактовьй импульс с первого выхода 26 генератора 14 поступает на синхровход счетчика 2 при разрешающем сигнале конца команды с выхода регистра 3.

При этом код операции, являющийся адресом первой микрокоманды выполняемой микропрограммы, через коммутатор 9 поступает на информационный вход счетчика 2 адреса.

По записанному в счетчике 2 адресу в блоке I памяти микрокоманд выбит рается соответствующая микрокоманда и поступает на его выходы. При наличии сигнала на синхровходе регист ра 3 операционная часть микрокоманды с выхода 1.1 поступает на информационный вход и записьшается в регистр 3 микроопераций. Сигналы микроопераций с регистра 3 поступают на вы5 ход 25 устройства.

При формировании адреса очередной микрокоманды возможны следующие режимы работы устройства:

0

0

I, Реализация линейных участков микропрограммы без проверки логичес ких условий.

2..Реализация безусловных пере- ходов в микропрограммах, о U 3. Реализация ветвлений с различной конфигурацией прове энемых логических условий,

I. По очередному тактовому им- пульсу с выхода 26 генератора 14 содержимое счетчика 2 адреса увеличивается на 1, Из-блока 1 памяти мш рокоманд выбирается следующая микрокоманда и т.д. до тех пор, пока не выбирается микрокоманда безусловного перехода по адресу шти микрокоманда , в которой предусмотрен анализ условий переходов.

2. При организации безусловного перехода с блока 1 памяти микрокоманд считывается микрокоманда, в формате которой присутствует код адреса перехода и метка, разреша{ощая прО хождение кода адреса перехода на вто рой информационный вход коммутатора 9 адреса. По очередному синхроим пульсу с выхода 26 генератора 14 код адреса через информационный .вход эа- письшается в счетчик 2 адреса, С блока 1 памяти микрокоманд выбирается микрокоманда безусловного перехода. По синхроимпульсу с вьпсода 27 генератора 14 сигналы микроопераций поступают на выход устройства. 3. Для определенности и наглядности рассмотрим функционирование микропрограммного устройства для тестового диагностирования и управ™ ления при реализации фрагмента мик- ропрограммы, показанного ка фиг.З. Функциональная схема блока 4 памяти условий перехода и блока 5 коммутации для этого случая представлена на фиг. 2 „

По очередному тактовому ик1пулъсу 26 с выхода счетчика 2 считьшаетсл адрес очередной микрокоманды. С блока i памяти выбирается мшсрокоман- да, операционная часть которой по™ ступает на информа ционный вход регистра 3 5 а адресная часть на блок 4 памяти. По этому адресу с блока 4 памяти на первый и второй

вхо.цы блока 5 коммутации выбирается информация, содержащая коды проверяемых в данной микрокоманде логических условий и соответствую- пще им адреса переходов. По тактовому импульсу с выхода 27 генератора 4 сигналы микроопераций с регист ра .3 поступают на выход 25 устройства.

Код первого проверяемого логического условия XI поступает на мультиплексор 7 (так как на выходе 29. распределителя 6 и на выходе 12.1 дешифратора I присутствует единичный сигнал ) и значения проверяемого логического условия Xj подаются на информационньш вход регистра 10. По заднему фронту первого тактового импульса 28 с выхода третьего элемента И 17 значение первого проверяемого условия,заносится в регистр 10. На выходах 29,2 распределителя 6 и выходах 12,2 (12,1/ дешифратора 1I при единичном (нулевом значении X, устанавливается (сохраняется единичный сигнал. По очередному тактовому импу.льсу 28 в регистр 10 заносится код второго проверяемого логического условия . Сигналы с « выходом дешифратора 11 указьшают, по какой ветви осуществляется переход ..

Далее устройство функционирует ая логично описанному. В случае, если очередное проверяемое условие является последним (например, последним является условие Х° l. , то в поле логического условия Х задается метка М| I, которая, проходя через блок 5 коммутации и коммутатор 8 (при единичном значении Х°, закрьшает элемент И 17 тем . запрещает прохождение синхроимпульсо 28 на вход распределителя 6, Следую- щи2 1 импульсом с выхода 26 генератора 14 (фиг.4), проходящим через открытый сигналом с выхода коммутатора 8 через (элемент ИЛИ 20J элемент И 5, в счетчик 2 заносится адрес

А

младший условия Х (изменен

с С на 1. Далее работа устройства продо тждется в соответствии с рассмотренным алгоритмом.

.f §№ху 7

; К§лок(1

ЛВ1111 UAILIIMU ,/

К длояу 3

К зяеменщ

КМ 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1327103A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU985787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР | |||

| Микропрограммное устройство управления | 1981 |

|

SU1005050A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-11—Подача