П

fcceo

оэ ф

со

ОГ ОС

113

Изобретение относится к вычислительной технике, предназначено для оперативного определения корреляционных функций случайньк процессов в реальном времени и может быть использовано в автоматике, биологии, медици не и других областях науки и техники

Цель изобретения - расширение частотного диапазона исследуемого сигна-

ла.

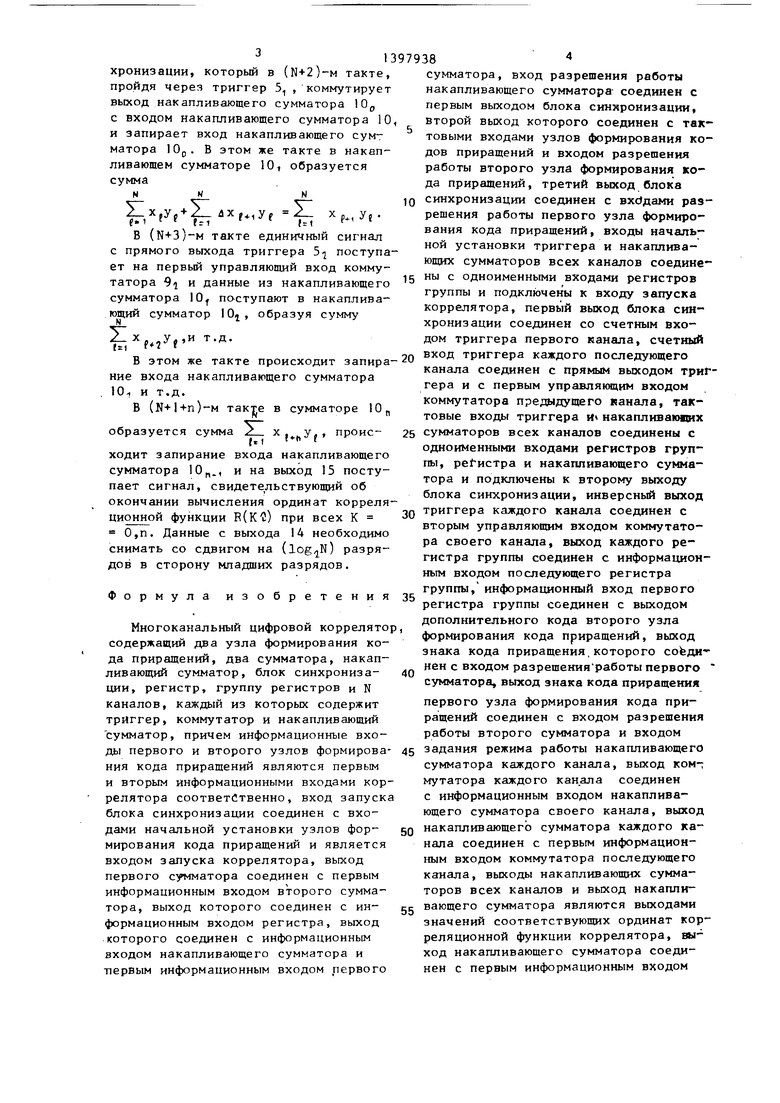

На чертеже приведена структурная схема коррелятора.

Коррелятор содержит блок 1 синхронизации, узлы 2, и 2 формиро- вания кода приращений, шифраторы 3 и 3,j, группу регистров , группу триггеров , сумматоры 6., и 6 , регистр 7, блоки сдвига ко1,1

дов, группу коммутаторов ,, накап-20 мпадших разрядов из результата с выхода первого сумматора 6 . 13наче25

ливающие сумматоры 10j,-10p, информационные входы 11 и 12, вход 13 запуска, выход 14, выход 15 сигнализации окончания вычислений.

Коррелятор работает следующим образом.

По сигналу, поступающему на вход 13 запуска устройства, осуществляется запуск блока 1 синхронизации, установка в исходное состояние первого 2, и 30 второго 22 узлов, регистров , регистра 7, накапливающих сумматоров

ние р

1.1

определяется величиной прИ

ращения входного сигнала на выходе кода приращений первого узла 2, в i-M такте работы устройства и численно равно номеру разряда, содержащего 1 в коде приращения сигнала x(t). Результат с йыхода второго сумматора 6 поступает в регистр 7 и далее в накалливающий сумматор Ю, где « по достижению заданного числа отсчетов получается значение iZ х.у. .

п

10(,-10р и триггеров

С выхода узлов 2 и 2 снимается текущее значение сигналов x(t) и y(t) в дополнительном коде.

Если значение приращения лу. положительное, т.е. на знаковом выходе приращений узла 2 О, то код с выхода узла 2 ,, поступающий через блок Вр., сдвига кода на второй вход первого сумматора 6 , со сдвигом на р . разрядов в сторону младщих разрядов, .суммируется со значением, поступа- кнцим с выхода регистра 7 и равным произведению предыдущих отсчетов сигналов x(t) и y(t). Значение определяется величиной приращения входного сигнала на выходе кода приращений второго узла 2 Ъ(-м такте работы устройства и численно равно номеру разряда, содержащего 1 в коде приращений сигнала y(t). Если же приращение Лу отрицательное, т.е. на выходе знака кода приращений узла 2 1, то код с выхода узла 2, поступающий на второй вход первого сумматора 6 со сдвигом на р разрядов в сторону младших разрядов, вычитается из значения, поступающего с выхода регистра 7. Управление режимами Суммирование н Вычитание на первом сумматоре-вычитателе 6. осуществляется сигналом с выхода знака кода приращений второго узла 2 . На втором сумматоре 6 выполняются сложение (если сигнал на выходе знака кода приращений первого узла 2, равен О) результата с выхода первого сумматора 6, и кода у текущего значения сигнала y(t), сдвинутого на р I разрядов в сторону млад- щих разрядов, или вычитание (если сигнал на выходе знака кода приращений первого узла 2 равен у текущего значения сигнала y(t), сдвинутого на р

1,1

разрядов в сторону

мпадших разрядов из результата с вы хода первого сумматора 6 . 13начение р

1.1

определяется величиной прИ

5

0

ращения входного сигнала на выходе кода приращений первого узла 2, в i-M такте работы устройства и численно равно номеру разряда, содержащего 1 в коде приращения сигнала x(t). Результат с йыхода второго сумматора 6 поступает в регистр 7 и далее в накалливающий сумматор Ю, где « по достижению заданного числа отсчетов получается значение iZ х.у. .

В течение N тактов работы устрой- ства на первом 6 и втором 6 сумматорах и регистре 7 осуществляется вычисление произведения отсчетов сигналов x(t) и y(t) и их накопление на накапливающем сумматоре 10. В результате зтого в N-M такте в накап- 0 ливающем сумматоое lOg образуется

сумма, равная XI . В течение этого времени значение единичного сигнала с инверсных выходов ров 5,-5, поступающее на второй уп- 5 равляющий вход коммутаторов 9i-9h разрещает коммутацию выходов регистров с входами накапливающих

5

0

сумматоров . К этому времени на накапливающем сумматоре 10 буhJ-1

ZI -лх

t 1 сумматоре lOj дет накоплена сумма

f.,yp

на

накапливающем

Н-1

ИХ (у, , на сумматоре

lOj N-3

2Z ЛХ . , И Т.Д. Рг1 г л с

В ()-M такте работы появляется сигнал на первом выходе блока 1 сии- 139

хронизации, который в (N+2)-M такте, пройдя через триггер 5 .коммутирует выход накапливающего сумматора 10 с входом накапливающего сумматора 10, и запирает вход накапливающего сум

матора 10р. В этом же такте в накапливающем сумматоре 10, образуется сумма

NNN

. (. (N-i-3)-M такте единичный сигнал с прямого выхода триггера 5 поступает на первый управляющий вход коммутатора 9 и данные из накапливающего сумматора 10 поступают в накаплива- сумматор lOj, образуя сумму

,У,,и т.д

сумматора, вход разрешения работы накапливающего сумматора соединен с первым выходом блока синхронизации, второй выход которого соединен с тактовыми входами узлов формирования кодов приращений и входом разрешения работы второго узла формирования кода приращений, третий выход блока

1Q синхронизации соединен с разрешения работы первого узла формирования кода приращений, входы начальной установки триггера и накапливающих сумматоров всех каналов соедине15 ны с одноименными входами регистров группы и подключены к входу запуска коррелятора, первый выход блока синхронизации соединен со счетным входом триггера первого канала, счетный

ющий

N

ui z

-.on ВХОД триггера каждого последующего

В этом же такте происходит запира- о - - h- м м -«

канала соединен с прямым выходом триГ- ние входа накапливающего сумматора«к

гера и с первым управляющим входом коммутатора предыдущего канала, тактовые входы триггера и« накаплнваюпих

10-, и т.д.

В ()-м такте

образуется сумма

t l

ходит запирание входа накапливающего сумматора Ю., и на выход 15 поступает сигнал, свидетельствующий об окончании вычисления ординат корреляционной функции В(К 2) при всех К О,п. Данные с выхода 14 необходимо снимать со сдвигом на () разрядов в сторону младших разрядов.

Формула изобретения 35

30

Многоканальный цифровой коррелято содержащий два узла формирования кода приращений, два сумматора, накапливающий сумматор, блок синхронизации, регистр, группу регистров и N каналов, каждый из которых содержит триггер, коммутатор и накапливающий сумматор, причем информационные входы первого и второго узлов формирования кода приращений являются первым и вторым информационными входами коррелятора соответственно, вход запуска блока синхронизации соединен с входами начальной установки узлов формирования кода приращений и является входом запуска коррелятора, выход первого сумматора соединен с первым информационным входом второго сумматора, выход которого соединен с информационным входом регистра, выход которого соединен с информационным входом накапливающего сумматора и первым информационным входом первого

сумматора, вход разрешения работы накапливающего сумматора соединен с первым выходом блока синхронизации, второй выход которого соединен с тактовыми входами узлов формирования кодов приращений и входом разрешения работы второго узла формирования кода приращений, третий выход блока

синхронизации соединен с разрешения работы первого узла формирования кода приращений, входы начальной установки триггера и накапливающих сумматоров всех каналов соединены с одноименными входами регистров группы и подключены к входу запуска коррелятора, первый выход блока синхронизации соединен со счетным входом триггера первого канала, счетный

канала соединен с прямым выходом триГ- «к

35

р,

гера и с первым управляющим входом коммутатора предыдущего канала, тактовые входы триггера и« накаплнваюпих

25 сумматоров всех каналов соединены с одноименными входами регистров группы, pefHCTpa и накапливающего сумматора и подключены к второму выходу блока синхронизации, инверсный выход

30 триггера каждого канала соединен с вторым управляющим входом коммутатора своего канала, выход каждого регистра группы соединен с информационным входом последующего регистра группы, информационный вход первого регистра группы соединен с выходом дополнительного кода второго узла формирования кода приращений, выход знака кода приращения,которого соёди нен с входом разрешения работы первого сумматора, выход знака кода приращения

первого узла формирования кода приращений соединен с входом разрешения работы второго сумматора и входом

45 задания режима работы накапливающего сумматора каждого канала, выход ком-; мутатора каждого кан.ала соединен с информационным входом накапливающего сумматора своего канала, выход

gQ накапливающего сумматора каждого канала соединен с первым информационным входом коммутатора последующего канала, выходы накапливающих сумматоров всех каналов и выход накаплн5 г вающего сумматора являются выходами значений соответствующих ординат корреляционной функции коррелятора, выход накапливающего сумматора соединен с первым информационным входом

40

5

коммутатора первого канала, прямой выход триггера последнего канала является выходом сигнализации окончания вычислений коррелятора, вход задания режима работы накапливающего сумматора соединен с шиной нулевого потенциала, отличающийся тем, что, с целью расширения частотного диапазона, в коррелятор введены два блока сдвига fcoдoв, группа блоков сдвига кодов, первый и второй шифраторы, входы первого и второго шифраторов соединены с выходами кода приращений соответствующих узлов формирования кода приращений, выход дополнительного кода первого узла формирования кода приращений соедине с информационным входом первого блок сдвига кодов, управляющий вход кото-

рого

соединен с выходом второго шифратора, выход дополнительиого кода второго узла формирования кода приращений соедииен с информационным входом второго блока сдвига кодов, управляющий вход которого соединен с управляющими входами блоков сдвига кодов группы и по дключен к выходу первого шифратора, выходы регистров группы соединены с информационными входами блоков сдвига кодов группы, выходы первого и второго блоков сдвигов кода соедииены соответственно с вторыми входами первого и второго сумматоров, выходы блоков сдвига кодов группы соединены с вторыми информационными входами соответствующих коммутаторов группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Вычислительное устройство для решения дифференциальных уравнений | 1985 |

|

SU1277134A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Коррелометр | 1984 |

|

SU1179368A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение частотного диапазона исследуемых сигналов. Коррелятор содержит блок 1 синхронизации, узлы формирования кодч приращений 2 и 2, шифраторы 3, 3,, группу регистров 4 I - 4, группу триггеров , сумматоры 6, 6, регистр 7, блоки о ti4i сдвига кодов, группу коммутаторов 9i-9p, накапливающие сумматори lOo-lOf,. Б корреляторе применены узлы формирования кода приращений с показательной системой кодирования приращений, лри этом ординаты корреляционной функции вычисляются параллельно. 1 йл.

| Коррелометр | 1984 |

|

SU1179368A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1985-02-22—Подача