121

Изобретение относится к контрольно-измерительной технике и может быть использовано при контроле цифровых блоков, имеющих двунаправленные выводы.

Цель изобретения - расшире 1ие функциональных возможностей выходного узла путем обеспечения допус- кового-контроля уровней на вьшодах цифрового блока и возможности контроля цифровых блоков, имеющих двунаправленные выводы на псевдослучайных кодах.

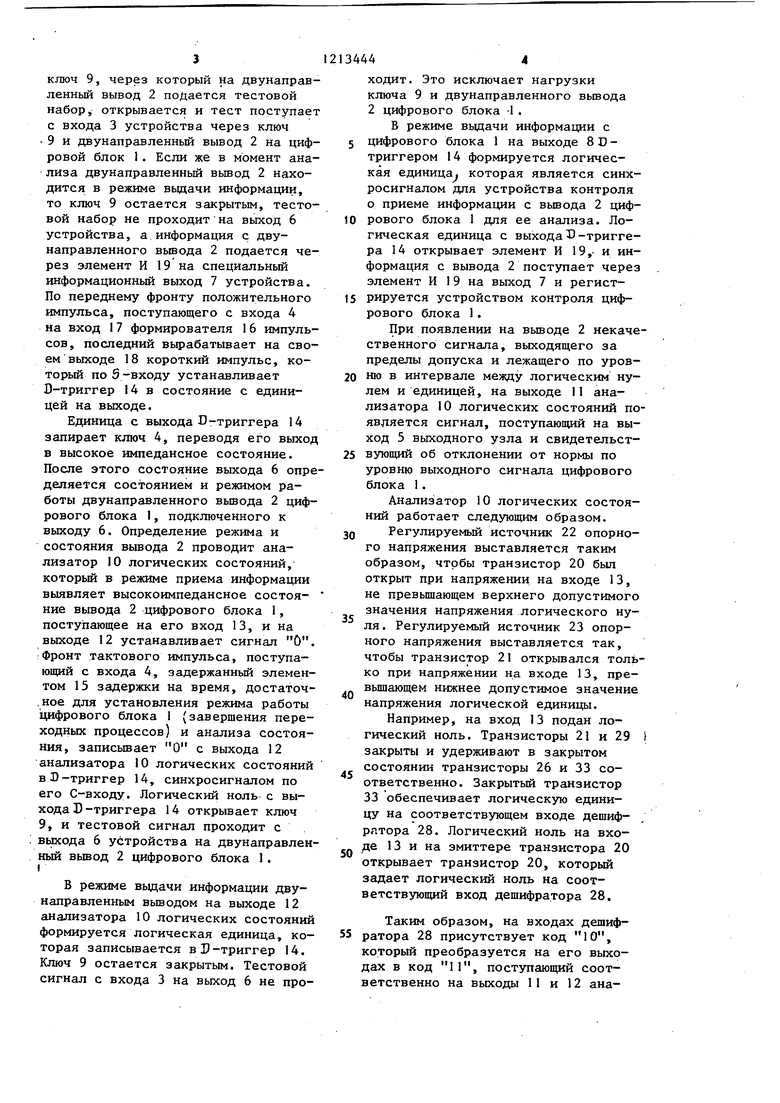

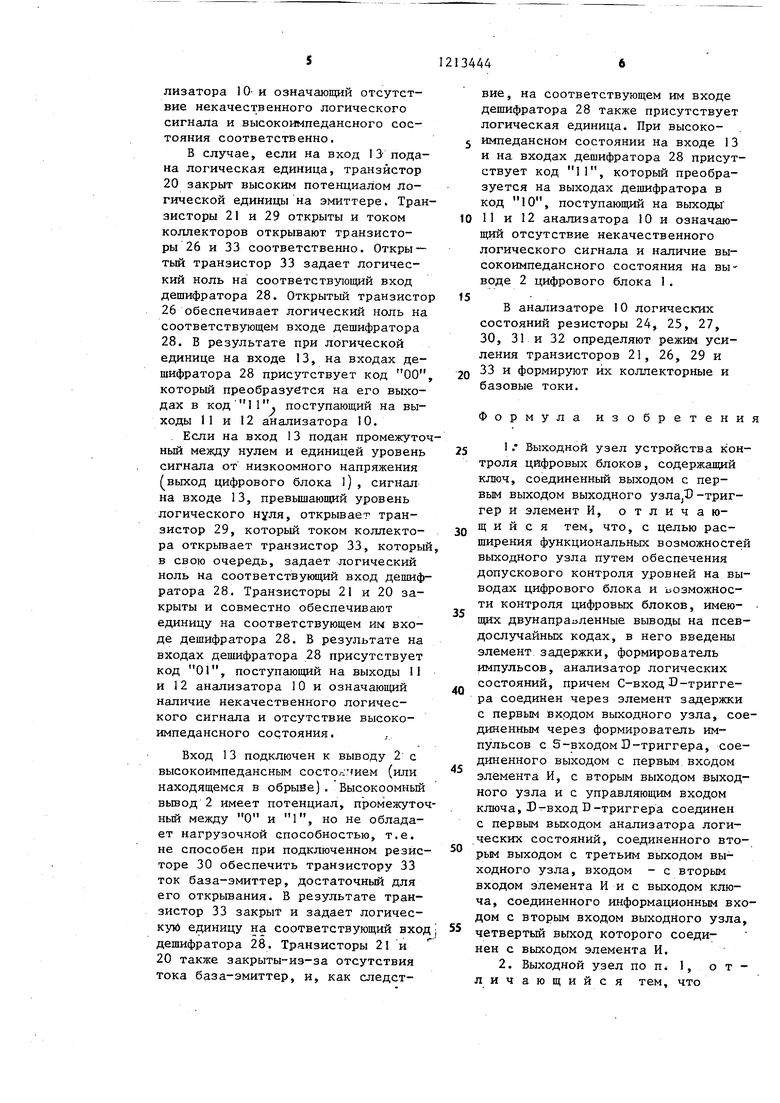

На фиг. 1 приведена схема выходного узла устройства контроля, цифровых блоков-, на фиг. 2 - схема анализатора логических состояний .

Выходной узел устройства контроля цифрового блока 1, имеющего двунаправленный вьшод 2, содержит второй 3 и первый 4 входы, третий 5, первый 6, четвертый 7 и второй 8 выходы, ключ 9, анализатор 10 логических состояний с вторым 11 и первым 12 выходами и входом 13, D-триггер 14, элемент 15 задержки, ормирователь 16 импульсов с вхоом 17 и выходом 18, элемент И I9.

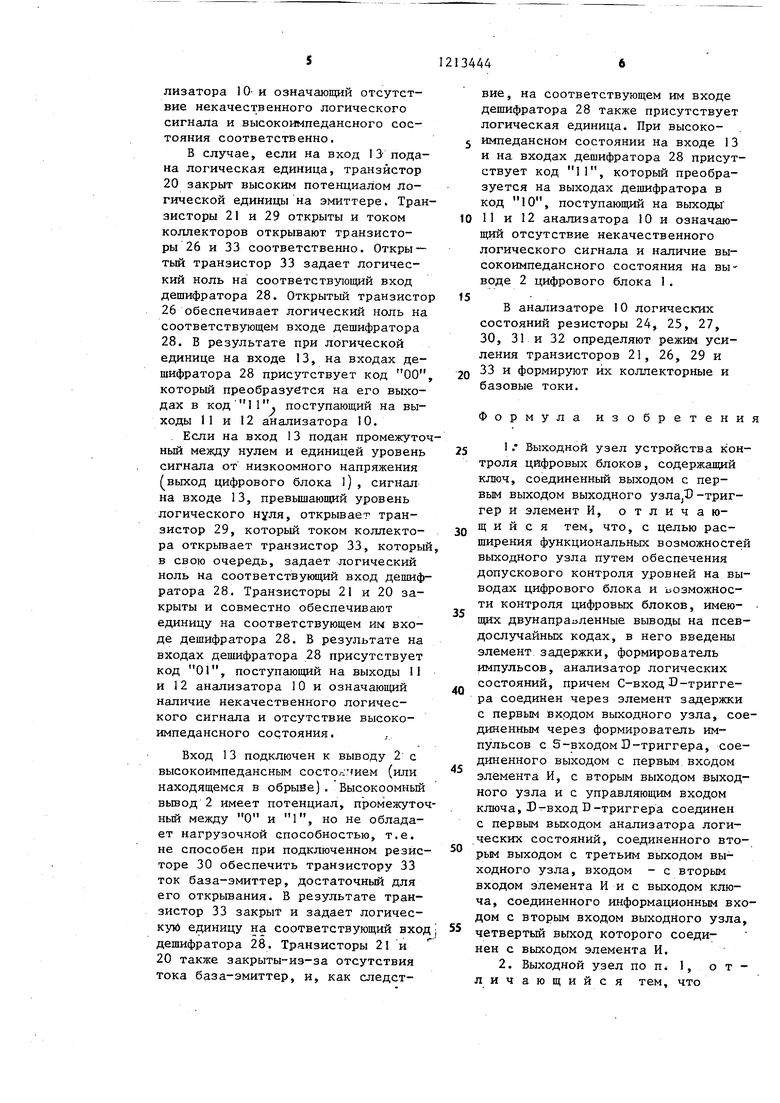

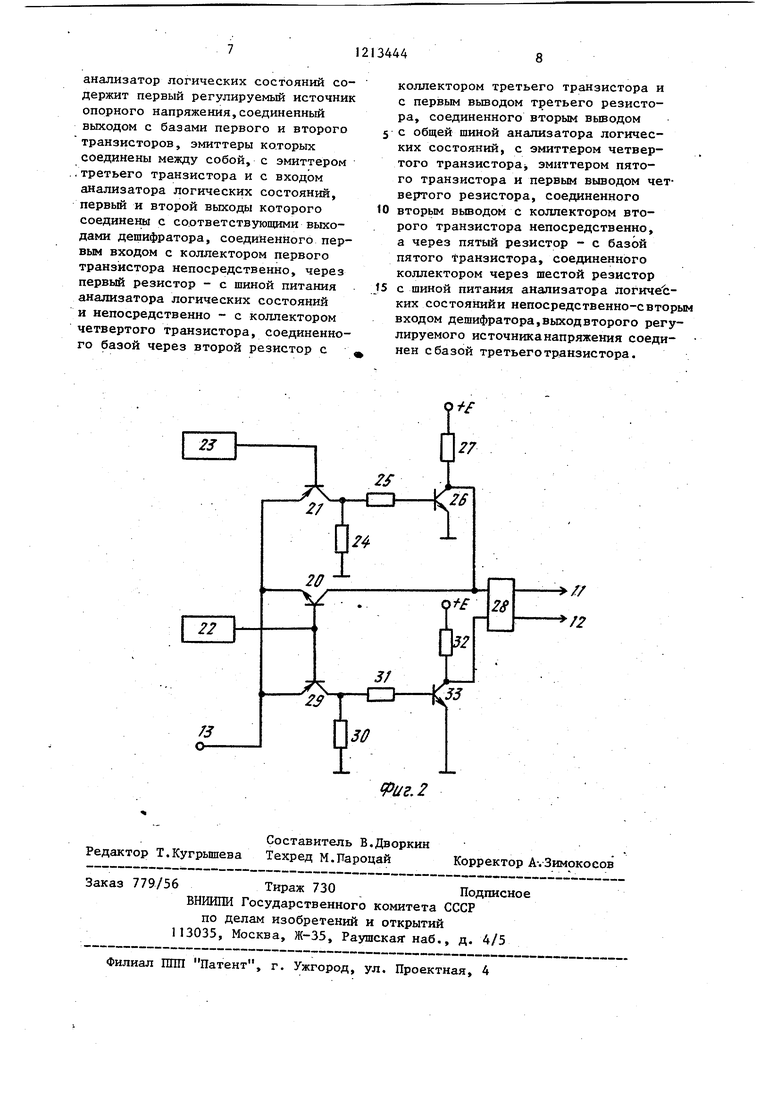

Анализатор 10 логических состояний содержит первый 20 и третий 21 транзисторы, первый 22 и второй 23 регулируемые источники опорного на- пряжения, третий 24 и второй 25 jpe- зисторы, четвертый транзистор . 26, первый резистор 27, дешифратор 28, второй транзистор 29, четвертый 30, пятый 31 и шестой 32 реггисторы, пятый транзистор 33.

Выход ключа 9 соединен с первым, выходом 6 выходного узла. С-вход -триггера 14 соединен через элемент 15 задержки с первым входом 4 выходного узла. Соединенным через формирователь 16 импульсов с S-вхо- , дом D-триггера 14, соединенного выходом с первым входом элемента И 19, с вторым выходом 8 выходного узла и с управляющим входом ключа 9,D -входом с первым выходом 12 анализатора 1 О логических.состояний, соединенного вторым выходом с третьим выходом 5 выходного узла, входом 13 - с вторым входом элемента И 19 и с выходом ключа 9, соединенного информационным входом с вторым входом 3 выходного узла, четвер42

тьй выход 7 которого соединен с вы- ходом элемента И 19.

В анализаторе 10 логических состояний первый регулируемый источник

22 опорного напряя ения соединен выходом с базой первого 20 и второго 29 транзисторов, эмиттеры которых соединены между собой, с эмиттером третьего транзистора 21 и с входом

13 анализатора 10 логических состояний, первый 12 и второй П выходы которого соединены с соответствующими выходами дешифратора 28, соединенного первым входом, с коллектором

первого транзистора 20 непосредственно J через первый резистор 27 - с шиной питания анализатора 10 логических состояний и непосредственно - с коллектором четвертого транзистора 26, соединенного базой через второй резистор 25 с коллектором третьего транзистора 21 и с первым вьшодом третьего резистора 24, соединенного вторым вьшодом с общей

шиной анализатора логических состояний, эмиттером пятого транзистора 33 и первым выводом четвертого резистора 30, соединенного вторым выводом с коллектором второго транзистора 29 непосредственно, а через пятый резистор 31 - с базой пятого транзистора 33, соединенного коллектором через шестой резистор 32 с шиной питания анализатора логических состояний и непосредственно - с вто-. рым входом дешифратора 28, выход второго регулируемого источника 23 опорного напряжения соединен с базой третьего транзистора.

Выходно узел устройства для контроля цифровых блоков работает следующим образом.

В режиме вьщачи информации двунаправленный вьшод 2 цифрового блока 1 находится в одном из логических состояний (О или 1), а , в режиме приема информации - в вы- ; сокоимпедансном состоянии. Так как .при испытании цифрового блока 1 .

псевдослучайными воздействиями заранее не известно, в каком из указанных режимов будет находиться двунаправленный вьшод, анализ режима проводится после каждого

задания тестового набора. Если в результате анализа определено, что двунаправленный вывод 2 находится в режиме приема информации, то

ключ 9, через который на двунаправленный вывод 2 подается тестовой набор, открывается и тест поступает с входа 3 устройства через ключ 9 и двунаправленный вывод 2 на цифровой блок 1. Если же в момент анализа двунаправленный вьшод 2 находится в режиме вьщачи информации, то ключ 9 остается закрытым, тестовой набор не проходит на выход 6 устройства, а информация с двунаправленного вьшода 2 подается через элемент И 19 на специальный информационный выход 7 устройства. По переднему фронту положительного импульса, поступающего с входа 4 на вход 17 формирователя 16 импульсов, последний вырабатывает на своем выходе 18 короткий импульс, который по S-входу устанавливает D-триггер 14 в состояние с единицей на выходе.

Единица с выхода D-триггера 14 запирает ключ 4, переводя его выход в высокое импедансное состояние. После этого состояние выхода 6 определяется состоянием и режимом работы двунаправленного вывода 2 цифрового блока 1, подключенного к выходу 6. Определение режима и состояния вывода 2 проводит анализатор 10 логических состояний, который в режиме приема информации выявляет высокоимпедансное состоя- ние вывода 2 цифрового блока 1, поступающее на его вход 13, и на выходе 12 устанавливает сигнал О. Фронт тактового импульса, поступающий с входа 4, задержанный элементом 15 задержки на время, достаточ- .ное для установления режима работы цифрового блока 1 (завершения переходных процессов) и анализа состояния, записьшает О с выхода 12 анализатора 10 логических состояний в Л-триггер 14, синхросигналом по его С-входу. Логический ноль с выхода D -триггера 14 открывает ключ 9, и тестовой сигнал проходит с выхода 6 устройства на двунаправленный вьюод 2 цифрового блока 1. I

В режиме выдачи информации двунаправленным вьшодом на выходе 12 анализатора 10 логических состояний формируется логическая единица, которая записывается в II-триггер 14. Ключ 9 остается закрытым. Тестовой сигнал с входа 3 на выход 6 не проходит. Это исключает нагрузки ключа 9 и двунаправленного вьгоода 2 цифрового блока -1 .

В режиме выдачи информации с

5 цифрового блока 1 на выходе 8 D- триггером 14 формируется логическая единица, которая является синхросигналом для устройства контроля о приеме информации с вьшода 2 циф10 рового блока 1 для ее анализа. Логическая единица с выхода И-триггера 14 открывает элемент И 19,- и информация с вывода 2 поступает через элемент И 19 на выход 7 и регист15 рируется устройством контроля цифрового блока 1.

При появлении на выводе 2 некачественного сигнала, выходящего за пределы допуска и лежащего по уров20 ню в интервале между логическим нулем и единицей, на выходе 11 анализатора 10 логических состояний появляется сигнал, поступающий на выход 5 выходного узла и свидетельст25 вующий об отклонении от нормы по уровню выходного сигнала цифрового блока 1.

Анализатор 10 логических состояний работает следующим образом.

3Q Регулируемый источник 22 опорного напряжения выставляется таким образом, чтобы транзистор 20 был открыт при напряжении на входе 13, не превьщ1ающем верхнего допустимого значения напряжения логического нуля . Регулируемый источник 23 опорного напряжения выставляется так, чтобы транзистор 21 открывался только при напряжении на входе 13, превышающем нижнее допустимое значение напряжения логической единицы.

Например, на вход 13 подан логический ноль. Транзисторы 21 и 29 закрыты и удерживают в закрытом состоянии транзисторы 26 и 33 соответственно. Закрытый транзистор 33 обеспечивает логическую единицу на соответствующем входе дешифратора 28. Логический ноль на входе 13 и на эмиттере транзистора 20 открывает транзистор 20, который задает логический ноль на соот- ветствзпощий вход дешифратора 28,

Таким образом, на входах дешиф- 55 ратора 28 присутствует код 10, который преобразуется на его выходах в код II, поступающий соответственно на выходы 11 и 12 ана35

40

45

50

лизатора 10- и означающий отсутствие некачественного логического сигнала и высокоимпедансного состояния соответственно.

В случае, если на вход 13 подана логическая единица, транзистор 20 закрыт высоким потенциалом Логической единицы на эмиттере. Транзисторы 21 н 29 открыты и током коллекторов открывают транзисторы 26 и 33 соответственно. Открытый транзистор 33 задает логический ноль на соответствующий вход дешифратора 28. Открытый транзистор 26 обеспечивает логический ноль на соответствующем входе дешифратора 28, В результате при логической единице на входе 13, на входах дешифратора 28 присутствует код 00, который преобразуется на его выходах в , поступающий на выходы 11 и 12 анализатора 10.

. Если на вход 13 подан промежуточный между нулем и единицей уровень сигнала от низкоомного напряжения (вьгход цифрового блока 1) , сигнал на входе 13, превышающий уровень логического нуля, открывает транзистор 29, который током коллектора открывает транзистор 33, который в свою очередь, задает логический ноль на соответствующий вход дешифратора 28. Транзисторы 21 и 20 закрыты и совместно обеспечивают единицу на соответствующем им входе дешифратора 28. В результате на входах дешифратора .28 присутствует код 01, поступающий на выходы II и 12 анализатора 10 и означающий наличие некачественного логического сигнала и отсутствие высокоимпедансного состояния.

Вход 13 подключен к выводу 2 с высокоимпедансным состоявшем (или находящемся в обрыве). Высокоомный вьшод 2 имеет потенциал, промежуточ ньш между О и 1, но не обладает нагрузочной способностью, т.е. не способен при подключенном резисторе 30 обеспечить транзистору 33 ток база-эмиттер, достаточньй для его открьгоания. В результате транзистор 33 закрыт и задает логичес- куй единицу на соответствующий вход дешифратора 28. Транзисторы 21 и 20 также закрыты-из-за отсутствия тока база-эмиттер, и, как следстдешифратора 28 также присутствует логическая единица. При высоко- импедансном состоянии на входе 13 и на входах дешифратора 28 присутствует код 11, который преобразуется на выходах дешифратора в код 10, поступающий на выходы 11 и 12 анализатора 10 и означающий отсутствие некачественного логического сигнала и наличие высокоимпедансного состояния на выводе 2 цифрового блока 1.

В анализаторе 10 логических состояний резисторы 24, 25, 27, 30, 31 и 32 определяют режим усиления транзисторов 21, 26, 29 и 33 и формируют их коллекторные и базовые токи.

Формула изобретения

I. Выходной узел устройства контроля цифровых блоков, содержащий ключ, соединенный выходом с первым выходом выходного узла) -триггер и элемент И, отличающийся тем, что, с целью расширения функциональных возможностей выходного узла путем обеспечения допускового контроля уровней на выводах цифрового блока и ьозможнос- ти контроля цифровых блоков, имеющих двунаправленные выводы на псевдослучайных кодах, в него введены элемент задержки, формирователь импульсов, анализатор логических состояний, причем С-вход D-триггера соединен через элемент задержки с первым входом выходного узла, соединенным через формирователь импульсов с 5-входомD-триггера, соединенного выходом с первым входом элемента И, с вторым выходом выходного узла и с управляющим входом ключа,D-вход D-триггера соединен с первым выходом анализатора логических состояний, соединенного вторым выходом с третьим выходом выходного узла, входом - с вторым входом элемента И и с выходом ключа, соединенного информационным входом с вторым входом выходного узла, четвертый выход которого соединен с выходом элемента И.

2. Выходной узел по п 1, отличающийся тем, что

анализатор логических состояний содержит первый регулируемый источник опорного напряжения,соединенный выходом с базами первого и второго транзисторов, эмиттеры которых соединены между собой, с эмиттером .третьего транзистора и с входом анализатора логических состояний, первый и второй выходы которого соединены с соответствующими выходами дешифратора, соединенного первым входом с коллектором первого транзистора непосредственно, через первый резистор - с шиной питания анализатора логических состояний и непосредственно - с коллектором четвертого транзистора, соединенного базой через второй резистор с

коллектором третьего транзистора и с первым вьтодом третьего резистора, соединенного вторым вьшодом 5 с общей шиной анализатора логических состояний, с эмиттером четвертого транзистораj эмиттером пятого транзистора и первым выводом четвертого резистора, соединенного

0 вторым вьгоодом с коллектором второго транзистора непосредственно, а через пятый резистор - с базой пятого транзистора, соединенного коллектором через шестой резистор

S с шиной питания анализатора логиче - ких состоянийи непосредственно-свторым входом дешифратора, выход второго регулируемого источника напряжения соединен с базой третьеготранзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Зонд для проверки сигналов цифровых микросхем | 1986 |

|

SU1348759A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Зонд для проверки сигналов цифровых микросхем | 1984 |

|

SU1228055A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| Релейный ключ | 1983 |

|

SU1091244A1 |

| Устройство для коммутации электромагнитного реле постоянного тока при неразрушающем контроле | 1984 |

|

SU1270748A1 |

| Измеритель сопротивлений резисторов | 1985 |

|

SU1357866A1 |

Изобретение относится к контрольно-измерительной технике и мо жет использоваться при контроле цифровых блоков, имеющих двуна- правленные выводы. Цель изобретения - расширение функциональных возможностей выходного узла - достигается путем допускового контроля уровней на вьюодах цифрового блока и возможности контроля цифровых блоков, имеющих двунаправленные выводы на псевдослучайных входах. Выходной узел устройства контроля цифрового блока 1, имеющий двунаправленный вывод 2, содержит входы 4, 5 и 6, выходы 7 и 8, ключ 9, анализатор логических состояний 10 с выходами Пи 12, входом 13,1)-триггер 14, элемент задержки 15, формирователь импульсов 16 с вхрдом 17 и выходом 18, логический элемент И 19. 1 з.п. ф-лы. 2 ил. to 00 4 4 «U е,/

// /

Составитель В.Дворкин Редактор Т.Кугрьшхева Техред М.Пароцай Корректор А-.Зимркосов

Заказ 779/56 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

иг.2

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-18—Подача