рым входам 1,М-х схем сравнения матрицы (,п), первый, второй и третий информатщонные входы 1, j-ro компаратора подключены соответственно к выходу 1-й (,n-l) схемы сравнения группы, к выходу J-й (,n) схемы сравнения группы и к выходу 1,-й схемы сравнения матрицы, К-и и М-й входы i-ro элемента И группы подключены соответственно к первому выходу К ,i-ro компаратора и к второму выходу i,M-ro компаратора.

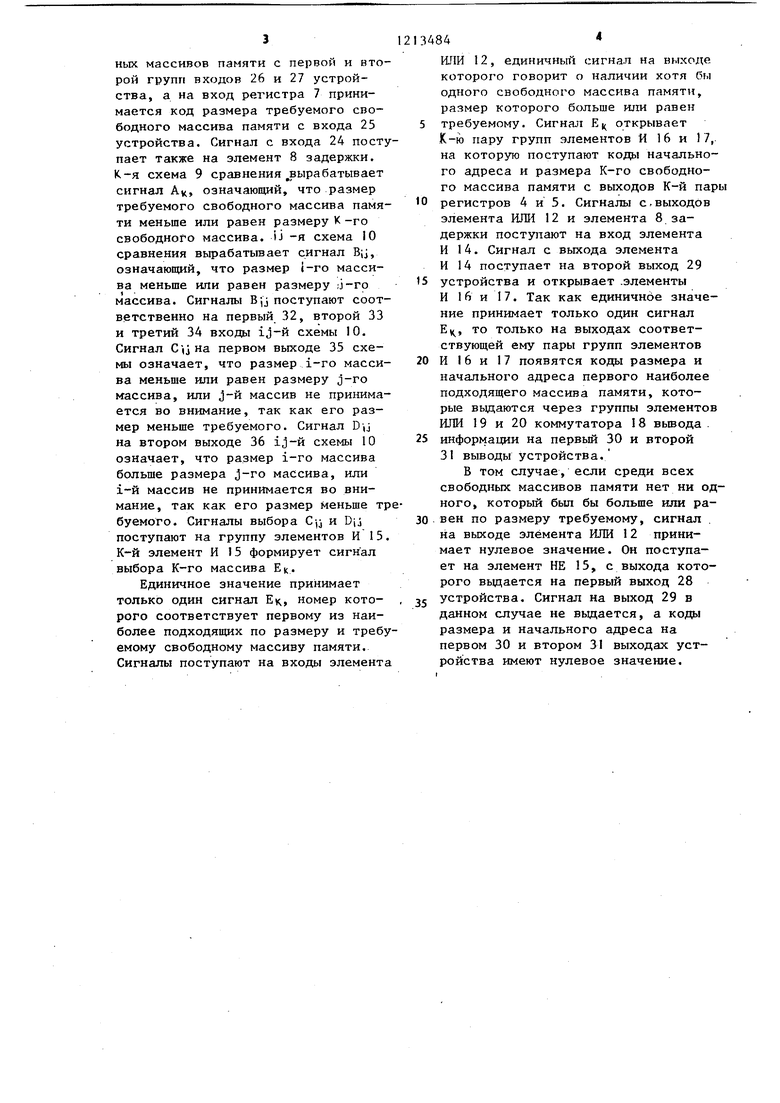

2. Устройство по п. 1, отличающееся компаратор содержит пять элементов НЕ, четыре элемента И и два элемента ИЛИ, причем первый, второй и третий информациойные входы компаратора подключены соответственно к первому второму и третьему входам первого элемента И компаратора, выход которого подключен к первому входу первого элемента ИЛИ компаратора, второй в5сод и выход которого подключеИзобретение относится к вычислительной технике, в частности к устройствам управления вычислительными комплексами.

Цель изобретения - сокращение среднего времени поиска свободного массива памяти.

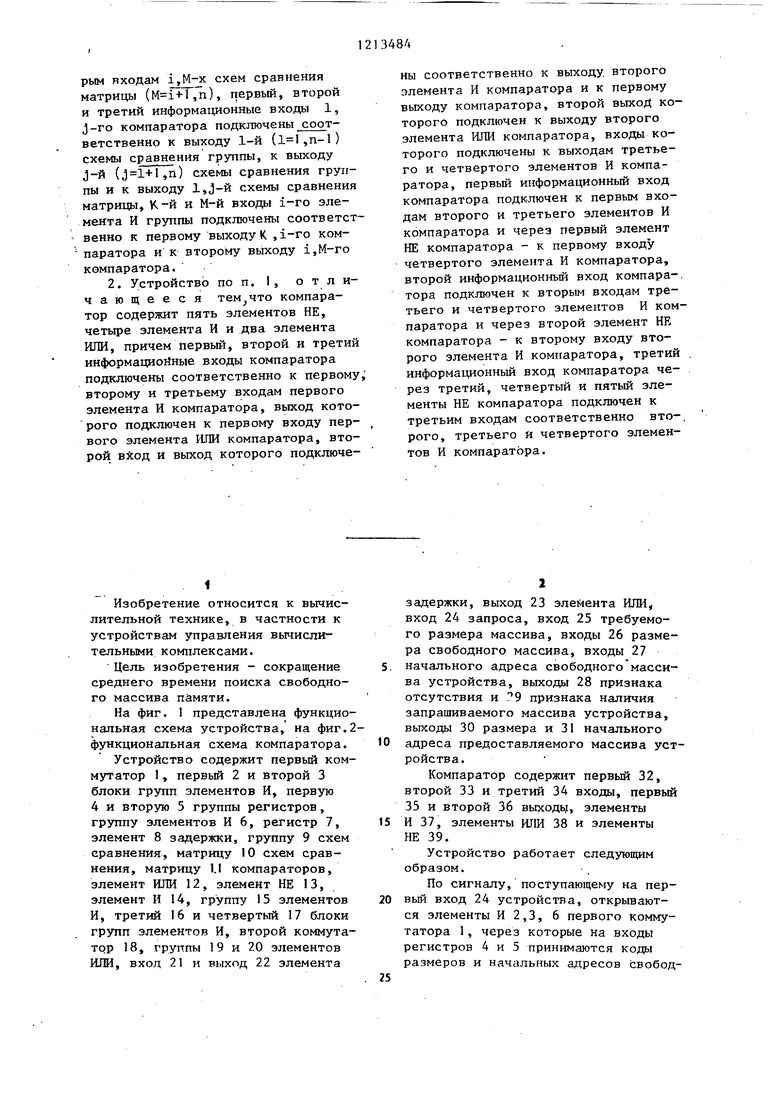

На фиг. 1 представлена функциональная схема устройства, на фиг. функциональная схема компаратора.

Устройство содержит первый коммутатор 1, первьй 2 и второй 3 блоки групп элементов И, первую 4 и вторую 5 группы регистров, группу элементов И 6, регистр 7, элемент 8 задержки, группу 9 схем сравнения, матрицу 10 схем сравнения, матрицу 1.1 компараторов, элемент ИЛИ 12, элемент НЕ 13, элемент И 14, группу 15 элементов И, третий 16 и четвертый 17 блоки групп элементов И, второй коммутатор 18, группы 19 и 20 элементов ИЛИ, вход 21 и выход 22 элемента

ны соответственно к выходу, второго элемента И компаратора и к первому выходу компаратора, второй выход которого подключен к выходу второго элемента ИЛИ компаратора, входы которого подключены к выходам третьего и четвертого элементов И компаратора, первый информационный вход компаратора подключен к первым входам второго и третьего элементов И компаратора и через первый элемент НЕ компаратора - к первому входу четвертого элемента И компаратора, второй информационный вход компаратора подключен к вторым входам третьего и четвертого элементов И компаратора и через второй элемент НЕ компаратора - к второму входу второго элемента И компаратора, третий информационный вход компаратора через третий, четвертый и пятый элементы НЕ компаратора подключен к третьим входам соответственно второго, третьего и четвертого элементов И компаратора.

задержки, выход 23 элемента ИЛИ, вход 24 запроса, вход 25 требуемого размера массива, входы 26 размера свободного массива, входы 27 начального адреса свободного массива устройства, выходы 28 признака отсутствия и 9 признака наличия запрашиваемого массива устройства, выходы 30 размера и 31 начального

адреса предоставляемого массива устройства.

Компаратор содержит первый 32, второй 33 и третий 34 входы, первый 35 и второй 36 выходу, элементы

И 37, элементы ИЛИ 38 и элементы НЕ 39.

Устройство работает следующим образом.

По сигналу, поступающему на пер- вый вход 24 устройства, открываются элементы И 2,3, 6 первого коммутатора 1, через которые на входы регистров 4 и 5 принимаются коды размеров и начальных адресов свобод-

5

ных массивов памяти с первом и второй групп входов 26 и 27 устройства, а на вход регистра 7 принимается код размера требуемого свободного массива памяти с входа 25 устройства. Сигнал с входа 24 поступает также на элемент 8 задержки. К.-я схема 9 сравнения ,вырабатывает сигнал АК, означающий, что размер требуемого свободного массива памяти меньше или равен размеру К-го свободного массива. iJ -я схема 10 сравнения вырабатывает сигнал B;j, означающий, что размер 1-го массива меньше или равен размеру ;j-ro массива. Сигналы Bij поступают соответственно на первый 32, второй 33 и третий 34 входы ij-й схемы 10. Сигнал C(j на первом выходе 35 схемы означает, что размер i-ro массива меньше или равен размеру j-ro массива, или j-й массив не принимается во внимание, так как его размер меньше требуемого. Сигнал D ,j на втором выходе 36 ij-й схемы 10 означает, что размер i-ro массива больше размера J-ro массива, или i-й массив не принимается во внимание, так как его размер меньше трбуемого. Сигналы выбора Cij и Djj поступают на группу элементов И 15. К-й элемент И 15 формирует сигнал выбора К-го массива ЕК.

Единичное значение принимает только один сигнал E|, номер которого соответствует первому из наиболее подходящих по размеру и требуемому свободному массиву памяти. Сигналы поступают на входы элемента

13484

ИЛИ 12, единичный сигнал на выходе которого говорит о наличии хотя бы одного свободного массива памяти, размер которого больше или равен

5 требуемому. Сигнал Е| открывает К-ю пару групп элементов И 16 и 17, на которую поступают коды начального адреса и размера К-го свободного массива памяти с выходов К-й пары

10 регистров 4 и 5. Сигналы с,выходов элемента ИЛИ 12 и элемента 8 задержки поступают на вход элемента И 14. Сигнал с выхода элемента И 14 поступает на второй выход 29

tS устройства и открывает .элементы

И 16 и 17. Так как единичное значение принимает только один сигнал Е(, то только на выходах соответствующей ему пары групп элементов

20 И I6 и 17 появятся коды размера и начального адреса первого наиболее подходящего массива памяти, которые выдаются через группы элементов ИЛИ 19 и 20 коммутатора I8 вьшода .

25 информации на первый 30 и второй 31 выводы устройства.

В том случае, если среди всех свободньк массивов памяти нет ни одного, который бьш бы больше или ра30 вен по размеру требуемому, сигнал на выходе элемента ИЛИ 12 принимает нулевое значение. Он поступает на элемент НЕ 15, с выхода которого выдается на первый выход 28

35 устройства. Сигнал на выход 29 в данном случае не выдается, а коды размера и начального адреса на первом 30 и втором 31 выходах устройства имеют нулевое значение.

2

а 2J

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения ресурсов оперативной памяти | 1985 |

|

SU1290335A1 |

| Устройство для ввода информации | 1984 |

|

SU1259241A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Устройство распределения оперативной памяти | 1988 |

|

SU1509909A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1315968A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Устройство управления распределением оперативной памяти | 1985 |

|

SU1298754A1 |

| Устройство для управления распределенной вычислительной системой | 1981 |

|

SU972509A1 |

| Устройство для адресации памяти | 1986 |

|

SU1328820A1 |

Составитель М.Силин Редактор Н.Данкулич Техред С.Мигунова Корректор С.Шекмар ,

Заказ 782/58, Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филяал ППП Патент, г. Ужгород, ул. Проектная, 4

f

39

35

Г

J

36

| Устройство сопряжения | 1976 |

|

SU602934A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-11—Подача