121

ЗНАЧЕЮСТЬ,группу из п элементрв И, группу из п элементов ИЛИ-НЕ,В-триг- гер.блок задержки,три элемента ИЛИ, три элемента И,элемент HEPАВНОЗНАЧ НОСТЬ,три элемента ИЛИ-НЕ и элемент НЕ,Блок задержки содержит два одновиб-1 ратора.По входу разрешения вычитания 1яа вход блока задержки поступает 1ЙЙ-; пульс сопровождения операндов.По спаду этого гошульса на первом выхо- де блока задержки появляется импульс.

Изобретение относится к вычислительной технике и может быть исполь зовано при обработке цифровой информации.

Целью изобретения является упрощение устройства и расширение об ласти применения за счет осуществления управляемого обнуления выхода устройства.

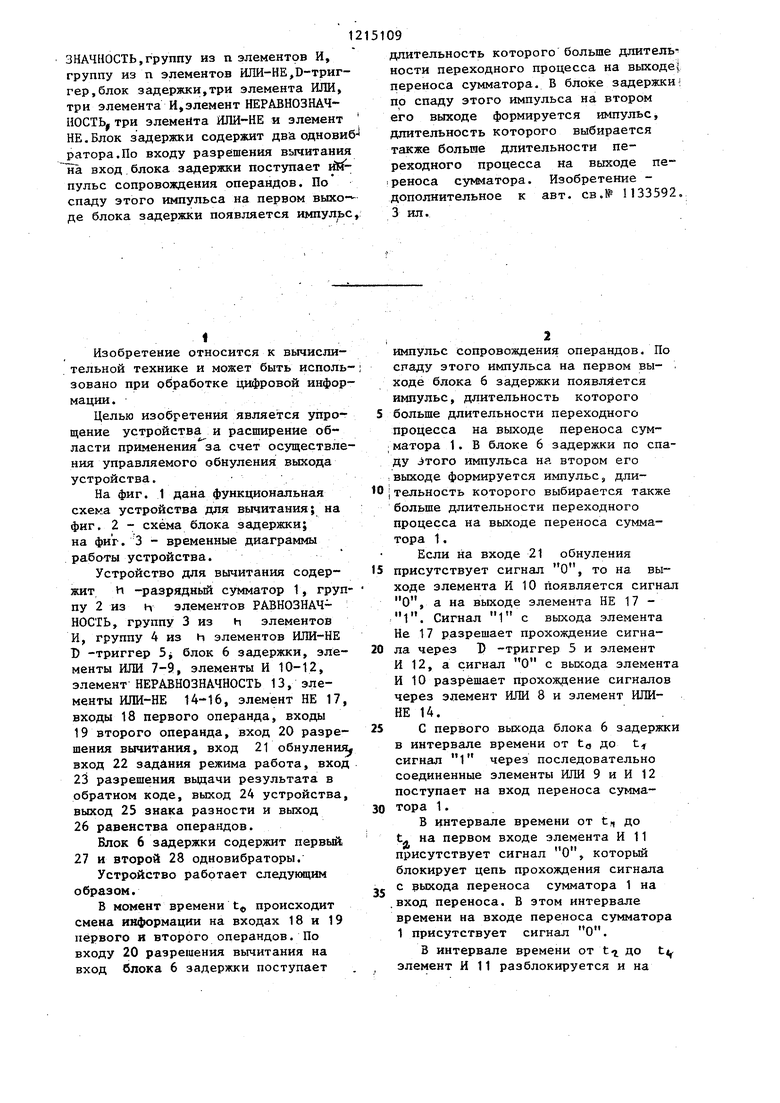

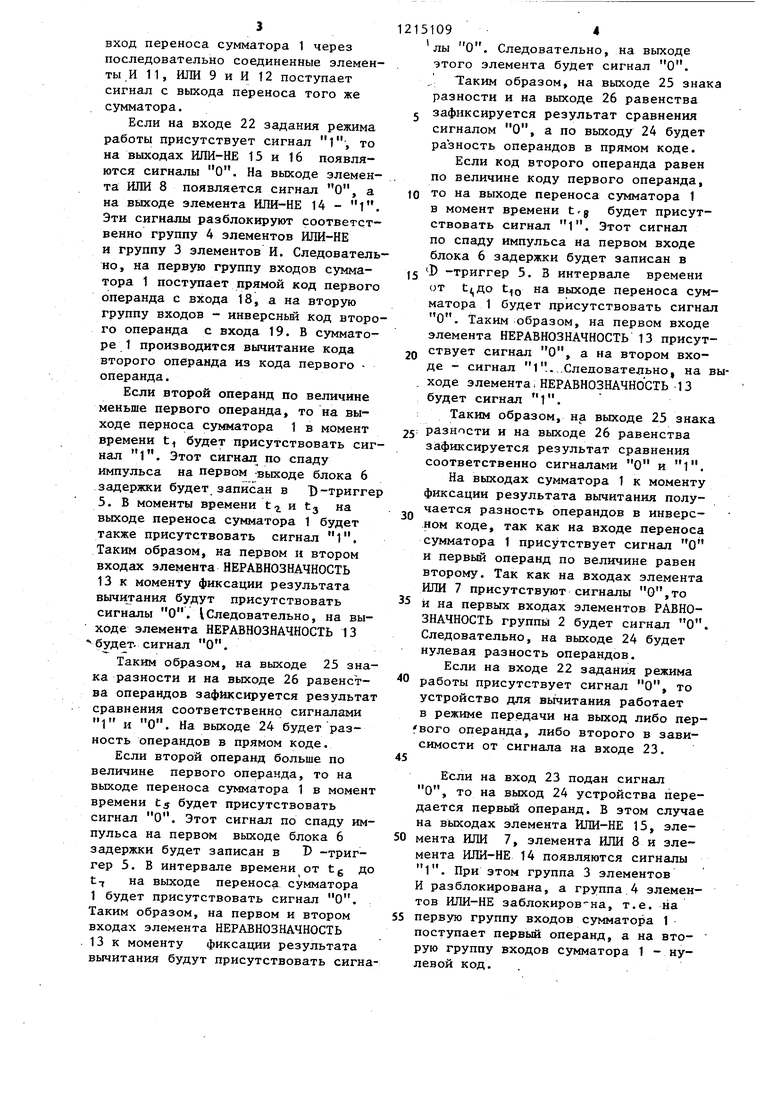

На фиг. 1 дана функциональная схема устройства для вычитания; на фиг. 2 - схема блока задержки; на фиг. 3 - временные диаграммы работы устройства.

Устройство для вычитания содер жит н -разрядньй сумматор 1, группу 2 из h элементов РАВНОЗНАЧНОСТЬ, группу 3 из h элементов И, группу 4 из h элементов ШШ-НЕ D -триггер 5j блок 6 задержки, элементы ИЛИ 7-9, элементы И 10-12, элемент НЕРАВНОЗНАЧНОСТЬ 13, элементы ИЛИ-НЕ 14-16, элемент НЕ 17, входы 18 первого операнда, входы 19 второго операнда, вход 20 разрешения вычитания, вход 21 обнуленшц вход 22 задания режима работа, вход 23 разрешения выдачи результата в обратном коде, выход 24 устройства, выход 25 знака разности и выход

26равенства операндов.

Блок 6 задержки содержит первый

27и второй 28 одновибраторы. Устройство работает следующим

образом.

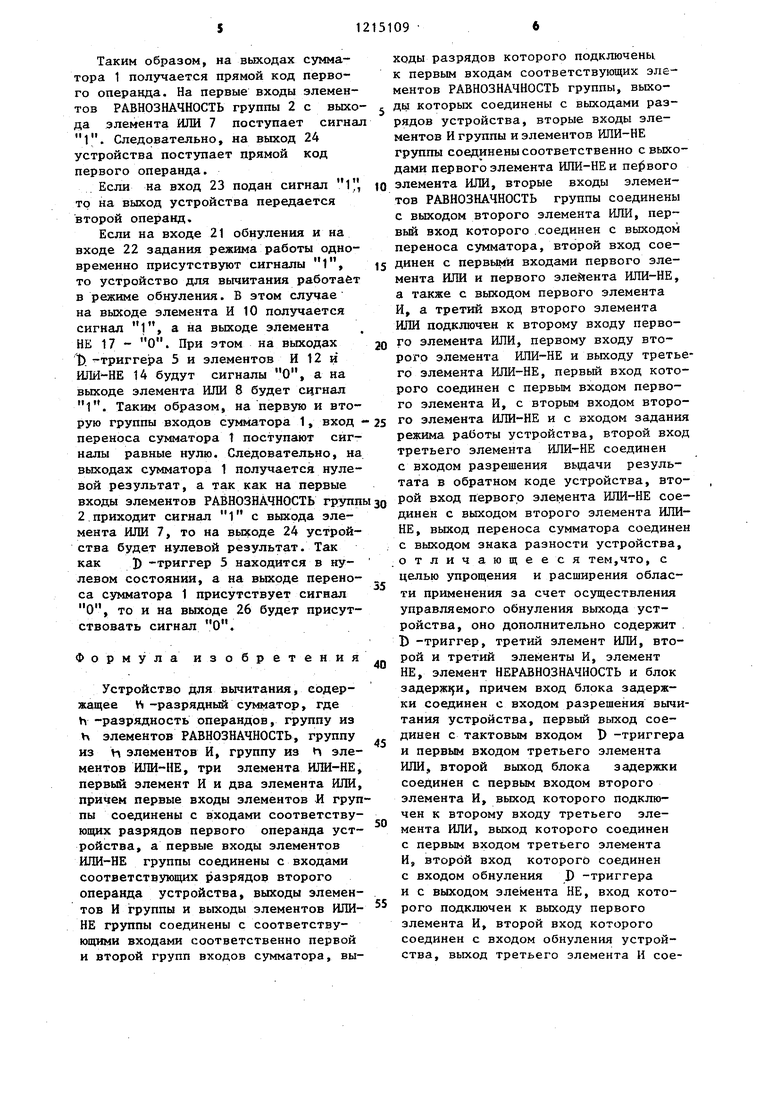

В момент времени t, происходит смена информации на входах 18 и 19 первого и второго операндов. По входу 20 разрешения вычитания на вход блока 6 задержки поступает

109

длительность которого больше длитель ности переходного процесса на выходе переноса сумматора, В блоке задержкиi по спаду этого импульса на втором его выходе формируется импульс, длительность которого выбирается также больше длительности переходного процесса на выходе пе- ipeHOca сумматора. Изобретение - дополнительное к авт. св.№ 1133592, 3 ил.

импульс сопровождения операндов. По спаду этого импульса на первом вы- . ходе блока 6 задержки появляется импульс, длительность которого 5 больше длительности переходного процесса на выходе переноса сум- ;матора 1. В блоке 6 задержки по спаду jToro импульса на втором его ,выходе формируется импульс, дли0Iтельность которого выбирается также больше длительности переходного процесса на выходе переноса сумматора 1.

Если на входе 21 обнуления

5 присутствует сигнал О, то на выходе элемента И 10 появляется сигнал О, а на выходе элемента НЕ 17 - 1. Сигнал 1 с выхода элемента Не 17 разрешает прохождение сигна0 ла через Т) -триггер 5 и элемент И 12, а сигнал О с выхода элемента И 10 разрешает прохождение сигналов через элемент ИЛИ 8 и элемент ШШ- НЕ 14.

5 С первого выхода блока 6 задержки в интервале времени от te до t сигнал 1 через последовательно соединенные элементы ИЛИ 9 и И 12 поступает на вход переноса сумма0 тора 1.

В интервале времени от t,, до t на первом входе элемента И 11 присутствует сигнал О, который блокирует цепь прохождения сигнала

- с выхода переноса сумматора 1 на .вход переноса. В этом интервале времени на входе переноса сумматора 1 присутствует сигнал О.

В интервале времени от t до t элемент И 11 разблокируется и на

вход переноса сумматора 1 через последовательно соединенные элементы И 11, ИЛИ 9 и И 12 поступает сигнал с выхода переноса того же сумматора.

Если на входе 22 задания режима работы присутствует сигнал 1, то на выходах ИЛИ-НЕ 15 и 16 появляются сигналы о. На выходе элемента ИЛИ 8 появляется сигнал О, а на выходе элемента ИЛИ-НЕ 14 - 1. Эти сигналы разблокируют соответственно группу 4 элементов ШШ-НЕ и группу 3 элементов И. Следовательно, на первую группу входов сумматора 1 поступает прямой код первого операнда с входа 18, а на вторую группу входов - инверсный код второго операнда с входа 19. В сумматоре 1 производится вычитание кода второго операнда из кода первого - операнда.

Если второй операнд по величине меньше первого операнда, то на выходе перноса сумматора 1 в момент времени t будет присутствовать сигнал 1. Этот сигнал по спаду импульса на первом -выходе блока 6 задержки будет записан в Т)-триггер 5. В моменты времени t и tj на выходе переноса сумматора 1 будет также присутствовать сигнал 1. Таким образом, на первом и втором входах элемента НЕРАВНОЗНАЧНОСТЬ 13 к моменту фиксации результата вычитания будут присутствовать сигналы О, iСледовательно, на выходе элемента НЕРАВНОЗНАЧНОСТЬ 13

будет- сигнал О.

Таким образом, на выходе 25 знака разности и на выходе 26 равенства операндов зафиксируется результат сравнения соответственно сигналами 1 и О. На выходе 24 будет разность операндов в прямом коде.

Если второй операнд больше по величине первого операнда, то на выходе переноса сумматора 1 в момент времени ty будет присутствовать сигнал О, Этот сигнал по спаду импульса на первом выходе блока 6 задержки будет записан в D -триггер 5. В интервале времени от tg до t-f на выходе переноса сумматора 1 будет присутствовать сигнал О. Таким образом, на первом и втором входах элемента НЕРАВНОЗНАЧНОСТЬ

13 к моменту фиксации результата вычитания будут присутствовать сигна2151094

лы О. Следовательно, на выходе этого элемента будет сигнал О.

Таким образом, на выходе 25 знака разности и на выходе 26 равенства с зафиксируется результат сравнения сигналом О, а по выходу 24 будет разность операндов в прямом коде.

Если код второго операнда равен по величине коду первого операнда, to то на выходе переноса сумматора 1 в момент времени t g будет присутствовать сигнал 1. Этот сигнал по спаду импульса на первом входе блока 6 задержки будет записан в J5 f -триггер 5. В интервале времени от t,o на выходе переноса сумматора 1 будет присутствовать сигнал О. Таким образом, на первом входе элемента НЕРАВНОЗНАЧНОСТЬ 13 присут- 20 ствует сигнал О, а на втором входе - сигнал 1 ...Следовательно, на вы- . ходе элемента,НЕРАВНОЗНАЧНОСТЬ .13 будет сигнал 1.

Таким образом, на выходе 25 знака 25 разности и на выходе 26 равенства зафиксируется результат сравнения соответственно сигналами О и 1, На выходах сумматора 1 к моменту фиксации результата вычитания полу- чается разность операндов в инверсном коде, так как на входе переноса сумматора 1 присутствует сигнал О и первый операнд по величине равен второму. Так как на входах элемента ИЛИ 7 присутствуют сигналы О,то 35 и на первых входах элементов РАВНОЗНАЧНОСТЬ группы 2 будет сигнал О. Следовательно, на выходе 24 будет нулевая разность операндов.

Если на входе 22 задания режима 0 работы присутствует сигнал О, то устройство для вьгчитания работает в режиме передачи на выход либо пер- fBoro операнда, либо второго в зависимости от сигнала на входе 23. 45

Если на вход 23 подан сигнал О, то на выход 24 устройства передается первый операнд. В этом случае на выходах элемента ИЛИ-НЕ 15, эле50 мента ИЛИ 7, элемента ИЛИ 8 и элемента ШШ-НЕ 14 появляются сигналы 1. При этом группа 3 элементов И разблокирована, а группа 4 элементов ИЛИ-НЕ заблокирована, т.е. на

55 первую группу входов сумматора 1 поступает первый операнд, а на вторую группу входов сумматора 1 - нулевой код. ..

Таким образом, на выходах сумматора 1 получается прямой код первого операнда. На первые входы элементов РАВНОЗНАЧНОСТЬ группы 2 с выхо да элемента ИЛИ 7 поступает сигна 1. Следовательно, на выход 24 устройства поступает прямой код первого операнда.

Если на вход 23 подан сигнал 1, то на выход устройства передается второй операнд.

Если на входе 21 обнуления и на входе 22 задания режима работы одновременно присутствуют сигналы 1, то устройство для вычитания работает в режиме обнуления. В этом случае на выходе элемента И 10 получается сигнал 1, а на выходе элемента НЕ 17 - О. При этом на выходах Ъ. -тригге ра 5 и элементов И 12 и ИЛй-НЕ 14 будут сигналы О, а на выходе элемента ИЛИ 8 будет счгнал 1. Таким образом, на первую и вторую группы входов сумматора 1, вход переноса сумматора t поступают сигналы равные нулю. Следовательно, на выходах сумматора 1 получается нулевой результат, а так как на первые входы элементов РАВНОЗНАЧНОСТЬ групп 2 приходит сигнал 1 с выхода элемента ИЛИ 7, то на выходе 24 устройства будет нулевой результат. Так как D -триггер 5 находится в ну- левом состоянии, а на выходе перено- са сумматора 1 присутствует сигнал О, то и на выходе 26 будет присутствовать сигнал О.

Формула изобретения

Устройство для вычитания, содержащее h -разрядный сумматор, где h -разрядность операндов, группу из h элементов РАВНОЗНАЧНОСТЬ, группу из и элементов И, группу из h элементов ИЛИ-НЕ, три элемента ИЖ-НЕ, первый элемент И и два элемента ИЛИ причем первые входы элементов И группы соединены с входами соответствующих разрядов первого операнда устройства, а первые входы элементов ИЛИ-НЕ группы соединены с входами соответствующих разрядов второго операнда устройства, выходы элементов И группы и выходы элементов ИЛИ- НЕ группы соединены с соответствующими входами соответственно первой и второй групп входов сумматора, вы

ю

15 20 5 о

0

5

0

ходы разрядов которого подключены к первым входам соответствующих элементов РАВНОЗНАЧНОСТЬ группы, выходы которых соединены с выходами разрядов устройства, вторые входы элементов И группы и элементов ИЛИ-НЕ группы соединены соответственно с выходами первого элемента ШШ-НЕи первого элемента ИЛИ, вторые входы элементов РАВНОЗНАЧНОСТЬ группы соединены с выходом второго элемента ИЛИ, первый вход которого .соединен с выходом переноса сумматора, второй вход соединен с первыми входами первого элемента ИЛИ и первого элейента ИЛИ-НЕ, а также с выходом первого элемента И, а третий вход второго элемента ИЛИ подключен к второму входу первого элемента ИЛИ, первому входу второго элемента ИЛИ-НЕ и выходу третьего элемента ИЛИ-НЕ, первый вход которого соединен с первым входом первого элемента И, с вторым входом второго элемента ИЛИ-НЕ и с входом задания режима работы устройства, второй вход третьего элемента ИЛИ-НЕ соединен с входом разрешения выдачи результата в обратном коде устройства, второй вход первого элемента ИЛИ-НЕ соединен с выходом второго элемента ИЛИ- НЕ, выход переноса сумматора соединен с выходом знака разности устройства, отличающееся тем,что, с целью упрощения и расширения области применения за счет осуществления управляемого обнуления выхода устройства, оно дополнительно содержит Ъ -триггер, третий элемент ИЛИ, второй и третий элементы И, элемент НЕ, элемент НЕРАВНОЗНАЧНОСТЬ и блок задерж15И, причем вход блока задержки соединен с входом разрешения вычитания устройства, первьш выход соединён с тактовым входом D -триггера и первым входом третьего элемента ИЛИ, второй выход блока задержки соединен с первьм входом второго элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с входом обнуления Р -триггера И с выходом элемента НЕ, вход которого подключен к выходу первого элемента И, второй вход которого соединен с входом обнуления устройства, выход третьего элемента И соединен с входом переноса сумматора, выход переноса которого подключен к D -входу D.-триггера, второму входу второго элемента И и первому

входу элемента НЕРАВНОЗНАЧНОСТЬ,второй вход которого соединен с выходом D -триггера,а выход подключен к выходу равенства операндов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1984 |

|

SU1327091A1 |

| Устройство для вычитания | 1985 |

|

SU1277097A1 |

| Устройство для вычитания | 1983 |

|

SU1133592A1 |

| Устройство для вычитания | 1984 |

|

SU1211720A1 |

| Устройство для обработки телединамограмм глубинно-насосных скважин | 1988 |

|

SU1671843A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Устройство для умножения | 1985 |

|

SU1252774A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

Изобретение относится к области вычислительной техники и может быть использовано при обработке цифровой информации. Целью изобретения является упрощение устройства и расширение области применения за счет .осуществления управляемого обнуле- ния выхода устройства. Устройство для вычитания содержит п-разрядный сумматор, группу из п элементов PABTi(DЯ-lf (П

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1983 с.337, рис | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Устройство для вычитания | 1983 |

|

SU1133592A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-28—Публикация

1984-07-20—Подача