1

ИтоГг -тч-кие .т осится к вычисли- тсупике и может быть исполь- 301, ИИ u.i)i iincTpoeiDiH арифметических II гяюжитсльных устройств, реали- чунчиих умножения двоичных

чисел со сдииг(1М множителя и суммы частимнмх 1111ои-- недсний на два разряда ппр;1.во.

HPJTI. и пОретеиия - увеличе)ше Г, рслсГ Г гиия устройства.

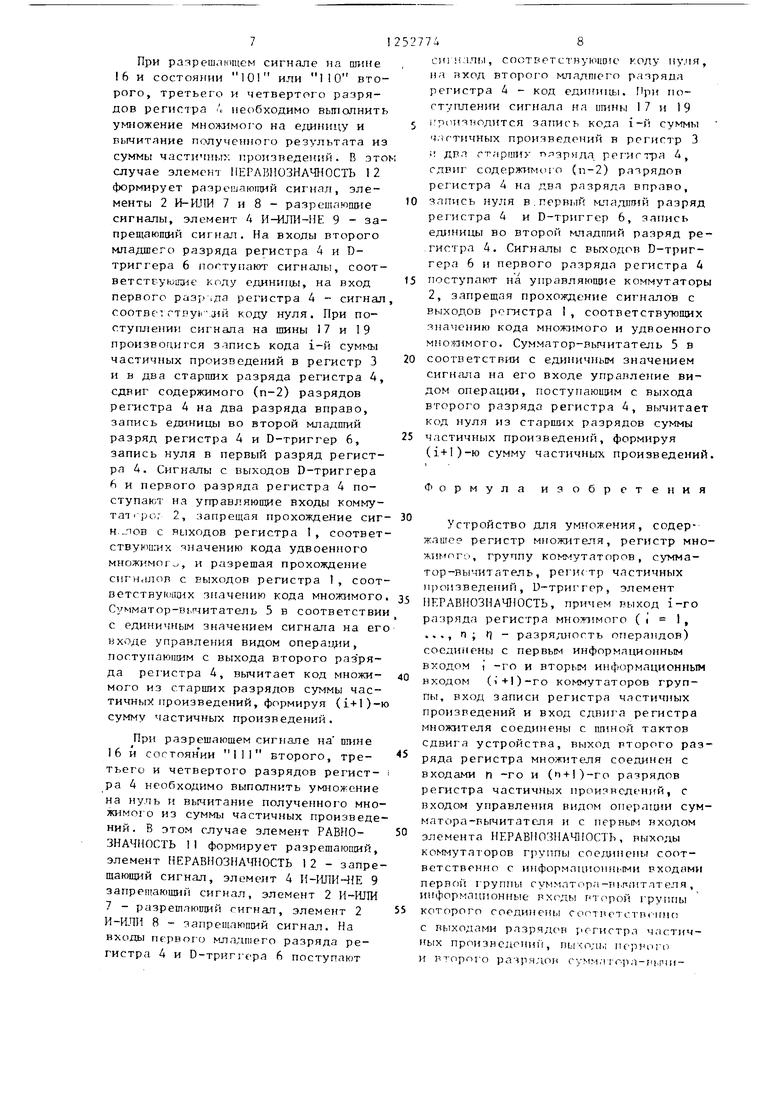

11л Ч(. р1оже представлена функцио- HaiTMiav су.ома устройства.

Устроив : р.о содеряз{Т регистр 1 множимого, группу коммутаторов 2, регистр 3 частичных произведений,

Iiervir- i - : множителя, сумматор-ны- П)татс .:п, , D-триггер 6, элементы 2 M-lL in 7 и 8, элемент 4 И-ШШ-НЕ 9, эломгнт НЕ 10, элемент РАВНОЗНАЧНОСТЬ 1 1 , элемент НЕРАВНОЗНАЧНОСТЬ 12, unilsy 13 установки первого разряда множителя, шину 14 установки нторого разряда множителя, шину 15 стробиропаиия первого такта, шину 1 С1робиронания тактов сдвига, такте- ную шяну 17, шину 18 первого такта тину 19 тактов сдвига. В случае от- гутстния необходимости стробировани на шины 15 и 18 и на шины 16 и 19 соо гнете гпенно мог ут подаваться од- ){и ч те же сигналы.

Устро1и;гво раОотает следующим образом.

В исходном состоянии в регистрах 3 и 4 и трит гера 6 хранится код нуля в 1 - длоичный код множимо- Ч), В пeppo такте умножения при ратрешенни на шине 18 н (п-2) старших ,ачрял,ах реги(тра 4 хранится код мщглителя (п-рачрядность операндов), яо втором и первом разрядах регистра 4, D-тригге-ра ( - сигналы управления счпчмт ором-пычитателем 5, передачей удвоенного fнoжимoгo, передачей множимого I Oij гветственно. После выполнения i-ro такта сдвига операции умножения (i - I,..., I ) при Р 1чрсп 1нии нл игине 19 в регистре хриштги дпоичный код множимого, в регистр.- ( г (2i.) старпшх разря- ;i,ix регистр: 4 - код i-и суммы частичных Пр.,Н: гОт;РнИ(, в (п -21 -2)

м;(.ч;:п-и, г-. . Т -Х регистра 4 - стар- K lst/ ; .. множителя, во л тор ом, .i M Hfv Г М .;ах регистра 4, D-триг- i f i | f - ( игиг:; упранле1П1Я суммато- ;ч - - ь.--ц гп 1 .(c, нсредачс; удвоенно

5

10

15

2025 30

52774J

множимого, передачей множимого соот- Г етстненно.

При разретаюшем сигнале на шине

я, - , ; а я

35

40

«5

50

55

15 и состоянии 00 на шинах 13 и 14 необходимо выполнить умножение на нуль и сложение полученного результата с нулевой суммой частичных произведений (перед умножением в регистре 3 хранится код нуля) .

В этом случае элементы 7 и 8 формируют запрещающий сигнал, элемент И-ИЛН-НЕ 9 также формирует запре- 1цаюио1Й сигнал. При поступлении сигнала на шины 17 и 18 производится запись нуля в D-триггер 6, первый и второй разряды регистра 4, запись (п-2) старших цифр множителя в (п-2) старшие разряды регистра 4, Сигналы с выхода D-триггера 6 и первого разряда регистра 4 поступают на управляюа1ие входы коммутаторов 2, запре- шая прохождение сигналов с выходов регистра 1. Сумматор-вычитатель 5 в соответствии с нулевым значением сигнала на его входе управления видом операции, поступающим с выхода второго разряда регистра 4 множителя, складывает коды нуля.

При разрешающем сигнале на тине .15 и состоянии 01 на шинах 13 и 14 необходимо выполнить умножение на единицу и сложение полученного результата с нулевой суммой частичных произведений. В этом случае элемент 2 И-ИПИ 7 формирует запрещающий сигнал, элемент 4 И-JVIH-HE 9 - запре- шаюшлй сигнал, элемент 2 И-ИЛИ 8 - разрешаюшлй сигнал. При поступлении сигнала на шины 17 и 18 производится з апись нуля в D-триггер 6 и второй разряд регистра 4, единицы - в первый разряд регистра 4, запись (п-2) старших цифр множителя в (п-2) старшие разряды регистра 4. Сигналы с выхода D-триггера 6 и первого разряда регистра 4 поступают на управляющие входы коммутаторов 2, запрещая прохождение сигналов с выходов регистра 1, соответствующих значению кода удвг)енного множимого, и разрешая прохождение сигналов с выходов регистра I , соответствуюп1их значению кода множимог о. Сумматор-вычитатель 5 в соответствии с нулевым значением сигнала на его входе управления видом операции, поступающим с выхода второго разряда регистра 4, склады- нает код множимого с кодом ггуля.

При разрешающем сигнале на шине 15 и состоянии 10 на шинах 13 и 1А необходимо выполнять умножение на два и вычитание множимого из нулевой суммы частичных произведений. В этом случае элемент 2 И-ИЛИ 7 формирует разрешающий сигнал, элемент А И-ИЛИ- НЕ 9 - разрешающий, элемент 2 И-ИЛИ 8 - запрещающий сигнал. При поступлении сигнала иа шииы 17 и 18 производится запись нуля в D-триггер 6, единицы - в первый и второй разряды регистра 4, запись (п-2) старших цифр множителя - в (п-2) старшие разряды регистра 4. Сигналы с выхода D-триггера 6 и первого разряда регистра 4 поступают на управляющие входы коммутаторов 2, запрещая прохождение сигналов с выходов регистр 1 множимого, соответствующих значе- нию кода множимого, и разрешая прохождение сигналов с выходов регистра

1множимого, соответствующих значени кода удвоенного множимого. Сумматор- вычитатель 5 в соответствии с единич ным значением сигнала на его входе управления видом операции, поступающим с выхода второго разряда регистра 4 множителя, вычитает из нуля код удвоенного множимого.

При разрешающем сигнале на шине 15 и состоянии 11 на шинах 13 и 14 необходимо вьшолнить умножение мно- жимого на единицу и вычитание множимого из нулевой суммы частичных прб- изведений. В этом случае элементы

2И-41ПИ 7 и 8 формируют разрешающий сигнал, элемент 4 И-ИЛИ-НЕ 9 - з,а- прешающий сигнал. При поступлении сигнала на шины 17 и 18 производится запись единицы в D-триггер 6, второй разряд регистра 4, нуля в первый разряд регистра 4, запись (п-2) старших цифр множителя в (п-2) старшие разряды регистра 4. Сигналы с выхода D-триггера 6 и первого разряда регистра 4 поступают на управ- ляюв9 е входы коммутаторов 2, запрещая прохождение сигналов с выходов регистра 1, соответствующих значению удвоенного множимого, и разрешая прохождение сигналов с выходов регистра I, соответствующих значению кода множимого. Сумматор-вьии- татель 5 в соответствии с единичным, значением сигнала на его входе управления видом операции, поступающим С выхода второго разряда регистра

0

5а20

ю -25 30

35

2527744

4 множителя, вычитает из нуля код множимого.

При разрешающем сигнале на пине 16 и состоянии 000 второго, третьего и четвертого разрядов регистра 4 необходимо выполнить умножение множимого на нуль и сложение полученного результата с суммой частичных произведений. В этом случае элемент НЕРАВРЮЗНАЧНОСТЬ I2 формирует запрещающий сигнал, элемент РАВНО- ЗНАЧРЮСТЬ 11 - разрешающий сигнал, элементы 2 И-ИЛН 7 и 8 - запрещающие сигналы, элемент 4 ИЧШИ-НЕ 9 - также запрещающий сигнал. Па входы двух младших разрядов регистра 4 и D-триггера 6 поступают сигналы, соответствующие коду нуля. При поступлении сигнала на шины 19 и 17 производится запись кода i-й суммы частичных Произведений в регистр 3 и в два старших разряда регистра 4, сдвиг содержимого (п-2) разрядов регистра 4 на два разряда вправо, запись нуля в два младших разряда регистра 4 и D-триггер 6, Сигналы с выходов D-триггера 6 и первого разряда регистра 4 поступают на управляющие входы коммутаторов 2, запрещая прохождение сигналов с выходов регистра 1 . Сумматор-вьгчита- тель 5 в соответствии с нулевым значением сигнала на его входе управления видом операции, поступающим с выхода второго разряда регистра 4, складывает коды нуля и старших разрядов суммы частичных произведений, формируя ()-ю сумму частичных произведений. Эта сумма в следующем такте сдвига будет записана в регистр 3.

При разрешающем сигнале на шине 16 и состоянии 001 или 010 второго, третьего и четвертого разрядов регистра 4 необходимо выполнить умножение множимого на единицу и сложение полученного результата с суммой частичных произведений. В этом случае элемент НЕРАВНОЗНАЧНОСТЬ 12 формирует разрешающий сигнал, элемент 4 И-ИЛИ-НЕ 9 - запрещающий сигнал, элемент 2 И-ИЛИ 8 - разрешающий сигнал, элемент 2 И-ИЛИ 7 - запрещающий сигнал. На входы двух младших разрядов регистра 4 поступают сигналы, соответствующие коду нуля, на вход D-триггера 6 - сигнал, соответствующий коду единицы. При поступлен«-ги

40

45

50

55

51

ni .ч n l пгины 17 и 19 производится чапнсь кодл i-и ryMNtbi частичных произведений и рег игтр 3 и в два стар- iunx разридл регистра А, сдвиг содер- ;ет1мого (п -2) разрядов регистра А на два разряда вправо, запись нуля в дна штадших разряда регистра А, запись единицы в D-триггер 6. Сигналы с выходов D-триггера 6 и первого раз рягл регистра А поступают на управ- ляюиа1е входа коммутаторов 2, запре- П1ая прохождение сигналов с выходов рег истра I множимого, соответствующих значении) кода удвоенного множимого, и разрешая прохождение сигна- лов с выходов регистра 1 множимого, соответствующих значению кода множи- мог о. Суммятор-вычитатель 5 в соответствии с нулевым значением сигнала на его входе управления видом опера- дни, поступающим с выхода второго разряда регистра А множителя, складывает коды MHOMiMoro и старших разрядов суммы частичных произведений, |}юрмируя (г + 1)-ю сумму частичных

произведений.

При разрешающем сигнале на шине

16и состоянии ОП второго, третьего и четвертого разрядов регистра А необходимо выполнить умножение множимого на два и сложение полученного результата с суммой частичных произведений. В зтом случае злемент РАВНОЗНАЧНОСТЬ 11 формирует запрещающий сигнал, злемент НЕРАВНОЗНАЧ- НОСТЬ 12 - запрещающий сигнал, эле мент А И-ИПИ-НЕ 9 - разрешающий супшал, элементы 2 И-ИЛИ 7 и 8 запрещающие сигн;1лы. На входы второго младшего разряда регистра А и D-триггера 6 поступают сигналы, соответствующие коду нуля, на вход первого младщего разряда регистра А - сигнал, соответствующт коду единицы. При поступлении сигнала на шины

17и 19 производится запись кода г-й суммы частичных произведений

в регистр 3 и в два старших разряда регистра А, сдвиг содержимого (п-2) разрядов регистра А на два разряда вправо, заггись нуля во второй млад- игий разряд рег истра А и D-триггер , запись единицы в первый разряд регистра А. Сигналы с выходов D- триггерл 6 и первого разряда ре-

I Истра А поступают на управляющие входы коммутаторов 2, запрещая прохождение сигналов с выходов рет ист

0 5 0 5

5

0

0

7А6

р,1 1 мнсзжимо- о, соответствующих значению кода множимого, и разрешая прохождение сигналов с выходов регистра 1 , соответствующих значению кода удвоенного множимого. Сумматор- вычитатель 5 в соответствии с нулевым значеним сигнала на его входе управления режимом,операции, поступающим с выхода второго разряда регистра А, складьгеает коды удвоенного множимого и старших разрядов сумм, частичных произведений, формируя (1-ь1)-ю сумму частичных произведений.

При разрешающем сигнале на шине

16и состоянии 100 второго, третьего и четвертого разрядов регистра А необходимо выполнить умножение множимого на два и вычитание удвоенного множимого из суммы частичных произведений, В этом случае элемент РАВНОЗНАЧНОСТЬ 1I формирует запрещающий сигнал, элемент НЕРАВНОЗНАЧНОСТЬ 12 - запрещающий сигнал, элемент 2 И-ИЛИ 7 - разрешающий сигнал , элемент А И-ИЛИ-НЕ 9 - разрешающий сигнал, элемент 2 И-ИЛИ 8 - запрещающий сигнал. На входы второго, первого младших разрядов регистра А поступают сигналы, соот- ветствующле коду единицы, на вход D-триггера 6 - сигнал, соответствую- ощй коду нуля.

При поступлении сигнала на шины

17и 19 производится запись кода i-й суммы частичных произведений в регистр 3 и в два старших разряда регистра А, сдвиг содержимого (п-2) разрядов регистра А на два разряда вправо, запись единицы во второй и первый младщие разряды регистра А, запись нуля в D-триггер 6. Сигналы

с выходов D-триггера 6 и первого разряда регистра А поступают на управ- ляющие входы коммутаторов 2, запре- щая прохождение сигналов с выходов регистра 1, соответствующих значению кода множимого, и разрешая прохождение сигналов с выходов регистра I, соответствующих значению кода удвоенного множ11мого. Сумматор-вы- читатель 5 в соответствии с единичным значением сигнала на его входе управления видом операции, поступающим с выхода второго разряда регистра А, вычитает код удвоенного множимого из старших разрядов суммы частичных произведений, формгруя (1+1)-ю сумму частичных произведений.

7

При разрешлкпцем сигнале на цнне 16 и состоянии 101 или 110 второго, третьего и четвертого разрядов регистра 4 необходимо выполнить умножение множимого на e;ijinHuy и вычитание полученного результата из суммы частичных нроизведений. В это случае элемент НЕРАВНОЗНАЧНОСТЬ 12 формирует разрешающий сигнал, элементы 2 И-ИЛИ 7 и 8 - разрешающие сигналы, элемент 4 И ЛИ-НЕ 9 - за- прещаюпшй сигнал. На входы второго младшего разряда регистра 4 и D- триггера 6 погтупают сигналы, соот- ветстг-уюад-1е коду едини1ц,1, на вход первого раэ1 ,да регистра 4 - сигнал cooTBci гтпу11 лй коду нуля. При поступлении сигнала на шины 17 и 19 производится запись кода i-й суммы частичных произведений в регистр 3 и в два старших разряда регистра 4, сдвиг содержимого (п-2) разрядов регистра 4 на два разряда вправо, запись единицы во второй младший разряд регистра 4 и D-триггер 6, запись нуля в первый разряд регистра 4. Сигналы с вь ходов D-триггера 6 и первого разряда регистра 4 поступают на управляюшие входы комму- тат 2, запрещая прохождение сиг Н..ЛОВ с выходов регистра 1 , соответ ствуюигих значению кода удвоенного множимого, и разрешая прохождение сигналов с выходов регистра I, соот ветствукшшх значению кода множимого Сумматор-вьгчитатель 5 в соответстви с единичным значением сигнала на ег входе управления видом операи 1И, поступающим с выхода второго раз ря- да регистра 4, вычитает код множимого из старших разрядов суммы час- тичныз произведений, формируя (1+1)сумму частичных произведений.

При разрешающем сигнале на пшне 16 и состоян ии 111 второго, третьего и четвертого разрядов регист- pa 4 необходимо выполнить умножение на нуль и вычитание полученного множимого из суммы частичных произведений. В этом случае элемент РАВНОЗНАЧНОСТЬ II формирует разрешагопий, элемент НЕРАВНОЗНАЧНОСТЬ 12 - запре шаюшлй сигнал, элемент 4 И-11ПИЧ1Е 9 запретаюший сигнал, элемент 2 И-ИПИ

7 разрешающий сигнал, элемент 2 И-ИПН 8 - запрещаюпмй сигнал. На входы первого младшего разряда регистра 4 и D-триггера 6 поступают

5277Д8

, соответствуюцще коду пуля, на вход второг О млялшего разряда регистра 4 - код единицы. Г1ри поступлении сигнала на пгины 17 и 19 5 1 П11изтюдится запись кода i-й суммы ч,-(гтичных произведений в регистр 3 и двл гтаршиу рег игтра 4, сдвиг содержимого (п-2) разрядов регистра 4 на два разряда вправо,

10 запись нуля в. первый младпгий разряд регистра 4 и D-триггер 6, запись единицы во второй младпгий разряд ре- .гистра 4. Сигналы с выходов D-триггера 6 и первого разряда регистра 4

15 поступают на управляюпа е коммутаторы 2, запрешая прохождение сигналов с выходов peniCTpa I, соответствующих значению кода множимого и удвоенного МНОШ1МОГО. Сумматор-вьгчитатель 5 в

20 соответствии с единичным значением на его входе управление видом операции, поступающим с выхода второго разряда регистра 4, вычитает код нуля из старших разрядов суммы

25 частичных произведений, формируя

(1+1)-ю сумму частичных произведений.

0

5

0

5

0

5

Формула изобретения

Устройство для умножения, содер- жяогее регистр множителя, регистр множимого, группу коммутаторов, сумма- тор-вычитатель, регистр частичных произведений, D-триггер, элемент НЕРАВНОЗНАЧНОСТЬ, причем выход i-ro разряда регистра множимого (i I, ..., п; П - разрядность операндов) соединены с первым информационным входом t -го и вторым информационным входом (1+1)-го KONiMyTaTopoB группы, вход записи регистра частичных произведений и вход сдвига регистра множителя соединены с шиной тактов сдвига устройства, выход второго разряда регистра множителя соединен с входами Г) -го и (i + )-ro разрядов регистра частичных произведений, с входом управления видом операщш сум- матора-вычитателя и с первым входом элемента НЕРАВНОЗНАЧНОСТЬ, выходы коммутаторов группы сое -цшены соответственно с информацио11Н1-1ми входами nepBoii группы суммптора-р1.г ;птлтеля , информационные второй группы которого соединены соотиетстпсппо с выходами разрядов регистра чпстнч- Hbix пронзяедони , пыходм первого и рторого рачря.чон сумм,ч 0 1;1-пьп111

,j1

.,,,,, ;.;: ii-i Ciiri-rHPTCTneHHO с

,.,-:n-. 1.-оД |ми (п-П-го и ,p;ni; .егистра мнода1теля, -i ( р.ч-.гчд.ч гумматпра-вычи- ..i,.jinHi H г входом () -2)-го

,, -г ри-к1 региггрп частичных произве- ;..иий (j 3, ,,.. и 1), о т л и - U а h. m - г- . U ген, что, с целью улепичги,.и быстродействия, п него ,,,,,, ,л.-..нт ГЛВНО-ИЛ ПЮСТЪ, эле- „Рит ИГ и ш-орой элементы : н-иПИ ,iT А И-ИЛИ-НЕ, причем ;ифвый . .ти.м.нта РЛННОЧИАЧНОСТЪ г,,г.ии-иеиы . . м :одом второго разряда (.ргиггрл ми(:житрля, выход третьего ,.,,.„,и--, .т..рого соединен с вторым ,v.,n.M -I.M и, л ИЕРАР ИГЯ1АЧИОСТЬ, первые и вторые управлянт е входы .,,,ммут,гг..ров группы соединены соот- иртственио г выходом D -триггера, i; с вых(-,ом первого разряда регистр мгоА1 ;1 ЛЯ, информапионный вход D (.г)нГГГ-р,-| : : - 1ИП.-И С ВЫХОДОМ ВТОрОГО

злр-, :;--ИМИ. riepBMH вход перво

,,.,-,;.-,.-.,,, -.ц Дияеи с выходом ,, | К 1 ЛИИ(1Ч11.ЧИОСТЬ, первый вх-д нторгч: групптл - г тпой уста- норки п./рв. - разряда миошггедя ус рг.йсти; -ini-: /Г г;чиовки второго ,- ми .:иге- --| vrrpojicTBa соединена ; i; 45f i i нх.;ь.м первой группы иерро -о 2 И-ИЛИ и входом 5Пгмегг1-1 И К , пнход кот рого сосди- иен с перво) группы

,t

у;(.-рТП)ГЙ ВХОД

0

15

27

5

20

25

30

7410

второй группы которого соединен с п.рвым входом второй группы пторого .,1емента 2 И-ШШ, выход элемента ., И-ШП1-НЕ соединен с информацион- иьм входом первого разряда регистра миижителя, информационный вход второго разряда которого сое;шнен с вы- хспюм первого элемента 2 И-ИЛИ, вто- р,.й вход первой группы которого сое- чпппч с вторыми входами первой и Рторой групп элемента 4 И-ИЛИ-НЕ, ртсрьр - входом второ.1 группы второ..пемента 2 И-ИЛН и г шшой стро- ;,ирот)апия первого такта устр : -тва, ы/ход х,етвертого разряда ре истра множителя coe;anieH с первым входом второй группы первого элемента 2 и с вторым входом элеке{гга ГЛ: .НОЗИАЧИОСТЬ, выход которого сое- с первым входом третьей груп- элемента А И-ИЛИ-ПЕ, первый вход четвертой группы КОТОРОГО соединен с выходом элемента НЕРАВНОЗНАЧНОСТЬ, стробирования тактов сдвига устройства соединена с вторыми входа- чш второй группы и первой группы второго элемента 2 И-ИЛИ и с вторыми вxoдa И третьей и четвертой групп элемента 4 И-ИШШЕ, входы син:фони- запии Т -триггера, первого и второго разрядов регистра множителя соединены с тактовой пшной устройства, вхо;т записи регистра мноткителя соединен с шиной первого такта устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения арифметических и множительных устройств, реализующих операции умножения двоичных чисел со сдвигом множителя и суммы частичных произведе- НИИ на два разряда вправо. Устройство позволяет увеличить быстро- цействие вьтолнения операции умножения за счет совмещения этапа полу- чепия суммы частичных произведений и этапа анализа пар разрядов множителя. Задача решается за счет того, что -в устройстве умножения функции форкирования управляющих сигналов передачей множимого, удвоенного множимого вьшолняют два младших разряда регистра множителя и допалин- тельньй триггер, на входе установки которых находится схема анализа пар разрядов множителя. 1 ил. (Л

| Астахов С.М | |||

| Цифровые вычислительные и управляющие машины и их использование в комплексных корабельных системах управления | |||

| Л.: ВМА, 1969, с | |||

| ТКАЦКИЙ СТАНОК | 1920 |

|

SU300A1 |

| Устройство для умножения | 1982 |

|

SU1084784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-01-02—Подача