Изобретение относится к вычислительной технике и предназначено для вычисления разности двух операндов в прямом коде, определения равенства операндов и передачи операндов на выход устройства.

Известно устройство для вычитания содержащее сумматор, компаратор, узлы записи, шину первого операнда, шину второго операнда и выход устройства. Шина первого операнда подключена к первой группе входов компаратора и к входам первого .узла записи, а шина второго операнда - к второй группе входов компаратора и входам второго узла записи. Сигналы с выходов узлов записи поступают соответственно на первую и вторую груп пы входов сумматора. Вход переноса младшего разряда сумматора подключей к сигналу в виде логической единицы. Управляющие входы узлов записи подключены к соответствующим выходам компаратора. Выходы сумматора образуют выход устройства lj .

Недостатками устройства являются сложность устройства, а также то, что оно не позволяет получить отдельно сигнал равенства операндов.

Наиболее близким к изобретению яв ляется устройство для вычитания, содержащее сумматор с параллельным переносом, элементы НЕ, элементы РАВНОЗНАЧНОСТЬ, элемент ИЛИ, шину первого операнда, шину второго операнда, выход знака разности и выход устройства. Шина первого операнда непосредственно подключена к первой группе входов сумматора с параллельным переносом, шина второго операнда - через элементы НЕ к второй группе входов сумматора, выход функции генерации переноса которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу функции, распространения переноса сумматора. Выход элемента ИЛИ подключен к входу переноса мпадшего разряда сумматора с параллельным переносом и к первой группе входов эле-v ментов РАВНОЗНАЧНОСТЬ, выходы которы образуют выход устройства, вторые входы группы элеме нтов РАВНОЗНАЧНОСТЬ к выходам сумматора с параллельным переносом. К выходу элемента ИЛИ подключен вход элемента НЕ, выход которого является выходом разности устройства 2 .

Недостатки известного устройства оно не позволяет получить сигнал равенства входных операндов и является относительно сложным.

При решении, например, задач нормализации изображений на выходе устройства для вычитания требуется получать либо разность двух операндов, либо первьй, либо второй операнды. В известных устройствах для вычитани такой режим работы непредусмотрен. Устройства не позволяют также получить сигнал равенства операндов. Все это снижает функциональные возможности устройств, увеличивает аппаратурные затраты и габариты устройств нормализации изображений.

Целью изобретения является расширение функциональных возможностей за счет реализации операций вьщачи сигнала равенства операндов и передачи операндов на выход устройства.

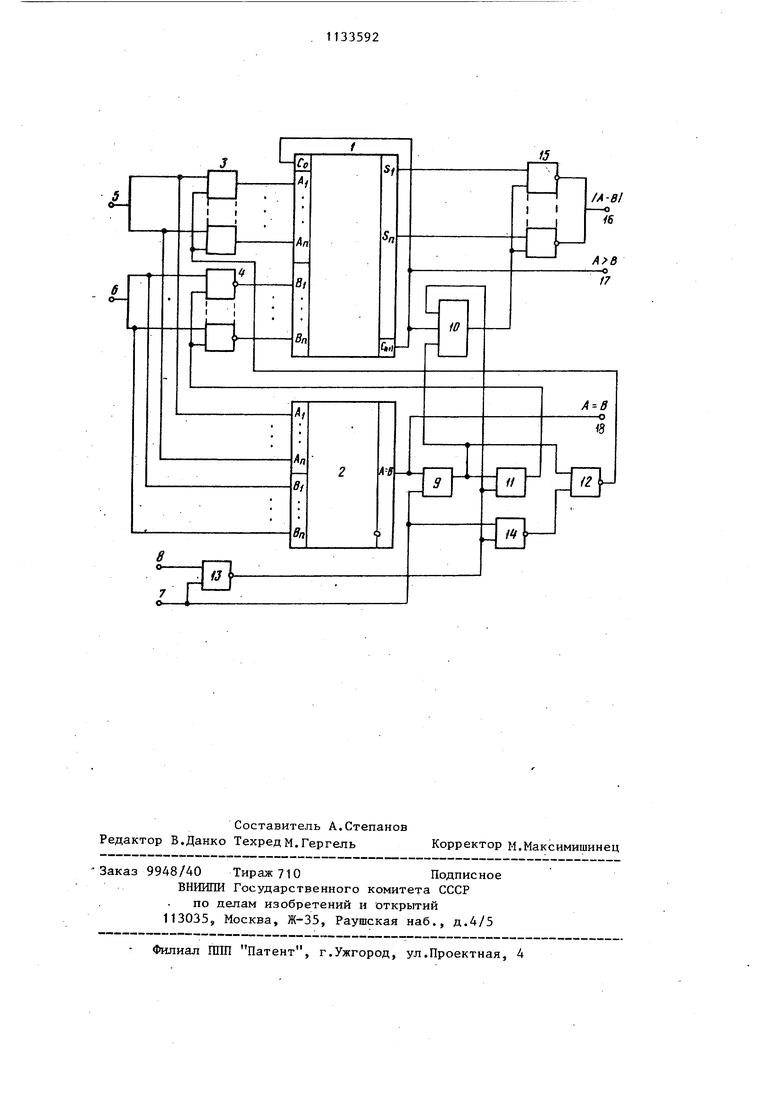

Указанная цель достигается тем, что в устройство для вычитания, содержащее П - разрядный сумматор, где -разрядность операндов, группу из п элементовРАВНОЗНАЧНОСТЬ и первый элемент ИЛИ, первый вход которого подключен к выходу переноса сумматора, а выход - к первым входам элементов РАВНОЗНАЧНОСТЬ группы, вторые входы которых подключены к выходам разрядов сумматора соответственно, выходы элементов РАВНОЗНАЧНОСТЬ группы образуют вьрсод устройства, введены компаратор, группа из И элементов И, группа из п элементов ИЛИ-НЕ, три элемента ИЛИ-НЕ, элемент И и второй элемент ИЛИ, причем первые входы элементов И группы подключены к соответствующим разрядам входной шины первого операнда устройства и к первой группе входов KONoiapaTopa, вторые входы элементов И группы соединены с выходом первого элемента ИЛИ-НЕ, первые входы элементов ИЛИ-НЕ группы - с соответствующими разрядами входной шины второго операнда устройства и с второй группой входов компаратора, вторые входы элементов ИЛИ-НЕ группы подключены к выходу второго элемента ИЛИ, выходы элементов И и ИЛИ-НЕ групп соединены соответственно с первой и второй группами входов сумматора, выход компаратора - с первым входом элемента И и с выходом равенства устройства, второй вход элемента И подключен к шине задания режима ра&оты устройства и к первым входам второго и третьего элементов ИЛЙ-НЕ, выход элемента И - к второму входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и .к первому входу первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента ИЛИ-НЕ, второй вход второго элемента ИПИ-НЕ -.с шиной вьщачи результата в обратном коде устройства, а выход подключен к третьему входу первого элемента ИЛИ, к второму входу второго элемента ИЛИ и к второму входу третьего элемента ИЛИ-НЕ, выход переноса сумматора соединен с входом переноса сумматора и с выходом знака разности устройства. На чертеже представлена функциональная схема устройства для вычитания. Устройство для вычитания-содержит 1Л -разрядный сумматор 1, компаратор 2, группу 3 из in элементов И, группу 4 из и элементов ИЛИ-НЕ, входную шину 5 первого операнда устройства, входную шину 6 второго операнда устройства, шину 7 задания режима работы устройства, шину 8 выдачи результата в обратном коде устройства, эле мент И 9, первый элемент ИЛИ 10, вто рой элемент ИЛИ 11, первый 12, второй 13 и третий 14 элементы ИПИ-НЕ, группу 15 из Г элементов РАВНОЗНАЧНОСТЬ, выход 16 устройства, выход 17 знака разности и выход 18 равенства устройства. Первые входы элеь ентов И группы 3 подключены к соответствующим разрядам входной шины 5 первого операнда и к первой группе входов компаратора 2. Первые входы элементов ИЛИ-НЕ группы 4 подключены к соответствующи разрядам входной шины 6 второго операнда и к второй группе входов компа ратора 2. Выходы элементов И иИЛИ-НЁ групп 3 и 4 подключены соответственн к первой и второй группам входов сум матора 1 о Выход компара;тора 2 подклю чен к первому входу элемента И 9 и является выходом 18 равенства устрой ства. Второй вход элемента И 9, первые входы второго 13 и третьего 14 элементов ШШ-НЕ подключены к шине 7 задания режима работы устройства. Второй вход второго элемента ИЛИ-НЕ 13 подключен к шине 8 вьщачи результата в обратном коде устройства.Третий вход первого элемента ИЛИ 10, второй вход второго элемента ИЛИ 11 и второй вход третьего элемента ИЛИ-НЕ 14 подключены к выходу второго элемента ИЛИ-НЕ 13. Выход элемента И 9 подключен к второму входу первого элемента ИЛИ 10, к первому входу второго элемента ИЛИ 11 и к первому входу первого элемента ИЛИ-НЕ 12, второй вход, которого подключен к выходу третьего элемента ИЛИ-НЕ 14. Вы- ход второго элемента ИЛИ 11 и выход первого элемента ИЛИ-НЕ 12 подключены соответственно к вторым входам элементов И и элементов ИЛИ-НЕ групп 3 и 4. Сигнал с выхода переноса сумматора 1 поступает на вход переноса сумматора 1, на выход 17 знака разности и на первый вход первого элемента ИЛИ 10, выход которого подключен к первым входам элементов РАВНОЗНАЧНОСТЬ группы 15, вторые входы которых подключены к выходам разрядов сумматора 1 соответственно. Выходы элементов РАВНОЗНАЧНОСТЬ группы 15 образуют выход 16 устройства. Устройство работает следующим образом. При наличии сигнала в виде логической единицы на шине 7 устройст о работает в режиме определения разности двух чисел в прямом коде. В этом режиме на выходах элементов ИЛИНЕ 14 и 13 образуются сигналы в виде логических нулей, которые поступают, соответственно, на второй вход первого элемента ИПИ-НЕ 12 и на вторые входы второго элемента ИЛИ 11, третьего элемента ИЛИ-НЕ 14 и третий вход первого элемента ИЛИ 10. Если уменьшаемое больше вычитаемого, то на выходе переноса сумматора 1получается сигнал в виде логической единицы, на выходе компаратора 2- сигнал в виде логического нуля. При этом на выходе второго элемента ИЛИ 11 и первого элемента ИЛИ-НЕ 12 образуются сигналы соответственно. в виде логического нуля и логической единицы, которые разрешают прохояодение операндов с шины 5 и с шины 6 через группу 3 элементов И и через группу 4 элементов ШШ-НЕ соответственно на первую и вторую группы входов сумматора 1, Таким образом, на первую группу входов сумматора 1 поступает прямой код первого операнда,, на вторую группу входов сумматора 51 1 - инверсный код второго операнда, а на вход переноса сумматора 1 - си нал в виде логической единицы. Сл довательно, на выходах сумматора 1 получается разность операндов в прямом коде. Так как на первые входы, элементов РАВНОЗНАЧНОСТЬ группы 15 поступает сигнал в виде логической единицы, то на выходе 16 устройства разность двух операндов получается в ijpHMOM коде, на выходе 17 знака разности : .фиксируется знак разности в виде логической единицы ; Если уменьшаемое меньше вычитаемо го, то на выходе переноса сумматора 1 получается сигнал в виде логического нуля. Как и в предьщущем случае, элементы И и ИЛИ-НЕ групп 3 и 4 не блокированы, так как на выходе элемента И 9 образуется сигнал в виде логического нуля. В этом случае н-а выходах сумматора 1 образуется разность операндов в инверсном.коде Так как на первые входы элементов РАВНОЗНАЧНОСТЬ группы 15 с выхода первого элемента РШИ 10 доступает сигнал в виде логического нуля, то на выходе 16 устройства разность опе рандов получается в прямом коде. На выходе 17 фиксируется знак разности В виде логического нуля. Если -меньшаемоа равно вычитаемому, то на выходе компаратора 2 и эле мента И 9 получаются сигналы в виде логической единицы. На выходе второго элемента ИЛИ 11 и первого элемента ИЛИ-НЕ 12 образуются сигналы соответственно в виде логической единицы и логического нуля, кото рые блокиру1от прохождение операндов с выходных шин 5 и 6. На первые и вторые группы входов сумматора 1 поступают нулевые коды. На выходе переноса сумматора 1 образуется сигнал в виде логического нуля, а на выходе первого элемента РШИ 10 - в виде логическбй единицы, так как на его второй вход поступает сигнал в виде логической единицы с выхода элемента И 9 Следовательно, на выходе 16 устройства получается нулевой код разности, а на выходе 18 фик сируется равенство операндов в виде логической единицы. При наличии сигнала виде логического нуля на шине задания ре2жима устройства работает в режиме передачи на выход 16 либо уменьшаемого, либо вычитаемого (в зависимости от сигнала на шине 8 выдачи результата в обратном коде). В этом режиме на выходе элемента И 9- получается сигнал в виде логического нуля, которьм поступает на первые входы элемента РШИ 11 и элемента РШИ-НЕ 12, а также на второй вход первого элемента ИЛИ 10., Если на шине 8. присутствует сигнал в виде логического нуля,то на выходе второго элемента ИЛИ-НЕ 13 образуется сигнал в виде логической единицы, который проходит через элементы РШИ 11 и 10, через последовательно соединенные элементы РШР1-НЕ 14 и 12 соответственно на первые входы элементов ИЛИ-НЕ группы 4 и первые входы элементов И группы 3. Таким образом, на первую группу входов сумматора 1 поступает прямой код первого операнда, на вторую группу входов - нулевой код. Следовательно, на выходах сумматора 1 и на выходе 16 устройства получается прямой код числа с входной шины 5,первого операнда. Если на шине 8 присутс1 ует сигнал в виде логической единицы, то на выходе второго элемента РШИ-НЕ 13 получается сигнал в виде логического нуля, которьй проходит через элемент РШИ 11, через последовательно соединенные элементы РШР1-НЕ 14 и 12 соответственно на первые входы элементов И и ИЛИ-НЕ групп 3 и 4. На выходе элемента РШИ 10 получается сигнал в виде логического нуля. на выходах сумматора 1 - инверсный, а на выходе 16 устройства - прямой код с входной шины 6 второго операнда. Использование предложенного изобретения позволяет получить на выходе устройства .либо разность операндов в прямом коде, либо первый, либо второй операнды, а также определять авенство операндов, что расширяет ункциональные возможности устройста. Применение изобретения в устройсте нормализации изображения позволио уменьшить аппаратурные затраты а его реализацию и габариты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1985 |

|

SU1277097A1 |

| Устройство для вычитания | 1984 |

|

SU1211720A1 |

| Устройство для вычитания | 1984 |

|

SU1215109A2 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| Арифметическое устройство | 1989 |

|

SU1635172A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1405049A1 |

| Сумматор-вычитатель по модулю | 1982 |

|

SU1075259A1 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

УСТРОЙСТВО Д.ПЯ ВЫЧИТАНИЯ, содержащее-П -разрядньш сумматор, где И - разрядность операндов, группу из П элементов РАВНОЗНАЧНОСТЬ и первый элемент ИЛИ, первьш вход которого подключен к выходу переноса сумматора, а выход - к первьм входам . элементов РАВНОЗНАЧНОСТЬ группы, вторые входы которых подключены к выходам разрядов cyiviMBTOpa соответственно, выходы элементов РАВНОЗНАЧНОСТЬ группы образуют выход устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации операций вьщачи сигнала равенства операндов и передачи операндов на , выход устройства, оно дополнительно содержит компаратор, группу из П элементов И, группу из П элементов ИЛИ-НЕ, три элемента ИЛИ-НЕ,элемент И и второй элемент ИЛИ, причем первые входы элементов И группы подключены к соответствующим разрядам входной шины первого операнда -устройства и к первой группе входов компаратора, вторые входы элементов И группы соединены с выходом первого элемента ШИ-НЕ, первые входы элементов 1ШИ-НЕ группы соединены с соответствующими разрядами входной шины второго операнда устройства и с второй группой входов компаратора, вторые входы элементов EJIIi-HE группы подключены к выходу второго элемента ИЛИ выходы элементов И и ИЛИ-НЕ , групп соединены соответственно с первой и второй группами входов сумматора, выход ко таратора -соединен с § первым входом элемента И и с выходом равенства устройства, второй вход (Л элемента И подключен к шине задания с режима работы устройства и к первым входам второго .и третьего элементов ИЛИ-НЕ,выход элемента И подключен к второму входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и к первому входу первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента ИЛИ-НЕ, второй вход второго элемента ИЛИ-НЕ соединен с шиной выдачи результата в обратном коде устройства, а выход подключен к третьему входу первого элемента ИЛИ, к второму входу второго элемента 1ШИ и к второму входу третьего элемента ИЛИ-НЕ, : выход переноса сумматора соединен с входом переноса сумматора и с выходом знака разности устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 756405, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М., Мир, 1983, с | |||

| Ленточный тормозной башмак | 1922 |

|

SU337A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1985-01-07—Публикация

1983-07-08—Подача