(54) СУММИРУЮЩЕ-ВЫЧИТАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующе-вычитающее устройство | 1986 |

|

SU1363192A1 |

| Адаптируемое суммирующе-вычитающее устройство | 1981 |

|

SU1005036A1 |

| УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ | 1969 |

|

SU244712A1 |

| Сумматор-вычитатель | 1984 |

|

SU1288691A1 |

| Арифметико-логический модуль | 1983 |

|

SU1160395A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

1

Изобретение относится к области вычислительной техники и может быть , использовано для построения арифмети 1еских устройств ЭВМ.

Известны комбинационные двоичные сумматоры-вычитатели, каждый разряд которых содержит Два элемента: неравнозначности 1. Недостатком таких устройств является невозможность реализации сложения или вычйтанйя йнверсных кодов двоичных чисел.

Наиболее близким к данному изобретению является суммирующё-вычитающее устройство, каждый разряд которо го содержит два элемента равноэначнрсти, входы первого из которых подключены к входам соответствующих разрядов операндов устройства, а ыход - к первому входу второго элемента равнозначности, выход которого является вь1ходом данного разряда устройства 2.

Недостатком этого устройства являeVcH то, что оно не реализует еложение или вычитание инверсий входных кодовдвоичных чисел/

Целью изобретения является расши рение функциональных возможностей, заключакяцихся в обеспечении сложения

2

и вычитания как прямых, так и инверо ных кодов операндов. Для достижения поставленной цели каждый разряд устройства дополнительно содержит третий и четвертый элементы равнозначности и элемент И, причемвторой вход второго элемента равнозначности соединен с первой . управляющей шиной устройства, первый вход элемента И соединен с выходом первого элемента равнозначности, а второй вход - с выходом третьего элемента равнозначности, входы которого подключены к входу переноса (заема) из предьщущего разряда устройства и второй управляющей шине устройства, выход элемента И соединен с первым входом четвертого элемента равнозначности, второй вход которого подклк)чен к третьей управляющей шине устройства, а выход к выходу переноса (заема) из данного разряда устройства.

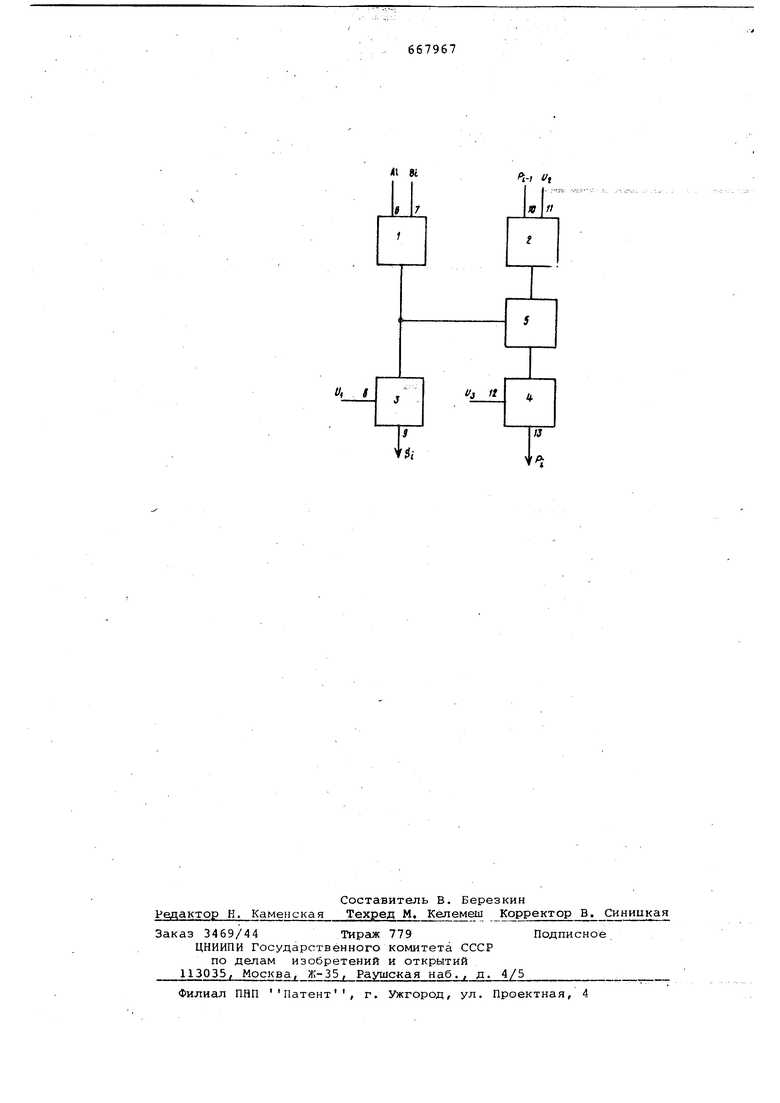

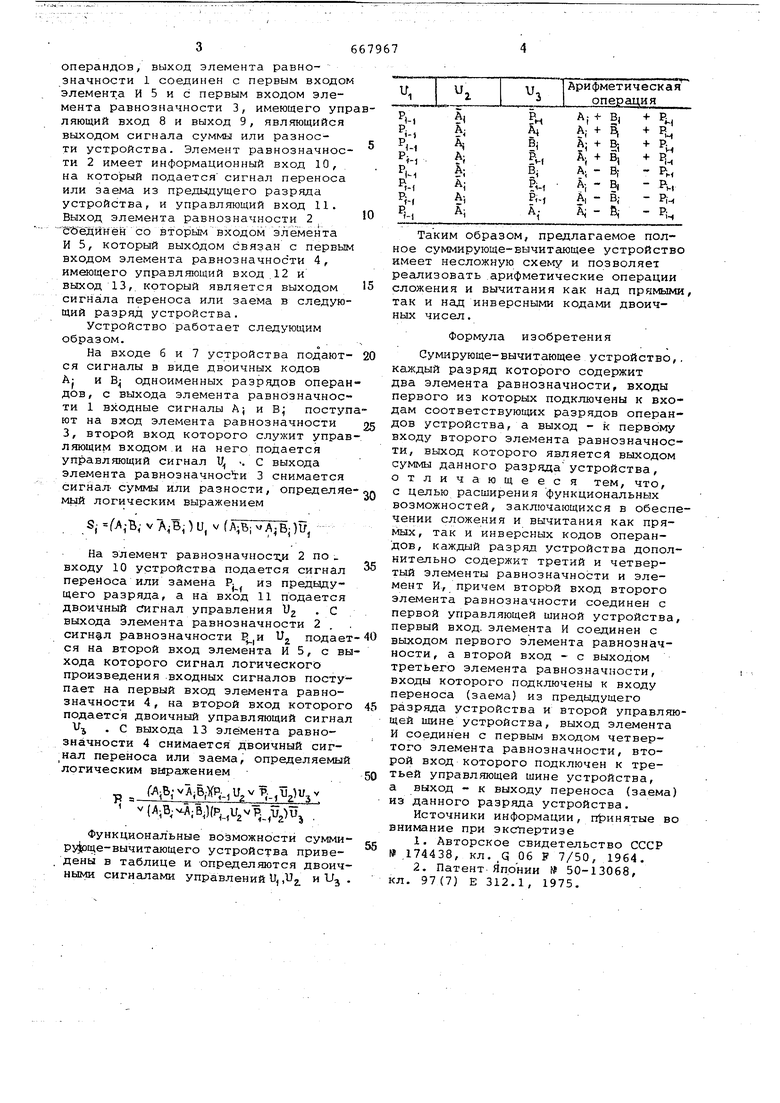

На чертеже представлена схема суммирующе-вычитающего устройства, которое содержит четыре элемента равнозначности 1-4 и элемент И 5. Элемент равнозначности 1 имеет два информационных входа б и 7, на которые подаются одноименные разряды операндов, выход элемента равнозначности 1 соединен с первым входом элемент.а И 5 и с первым входом элемента равнозначности 3, имеющего упр ляющий вход 8 и выход 9, являющийся выходом сигнала суммы или разности устройства. Элемент равнозначности 2 имеет информационный вход 10, . на который подается сигнал переноса или заема из предыдущего разряда устройства, и управляющий вход 11. Выход элемента равнозначности 2 с бедйнён со вторь1м входом элемента И 5, который выходом связан с первым входом элемента равнозначности 4, имеющего управляющий вход.12 и выход 13, который является выходом сигнала переноса или заема в следующий разряд устройства. Устройство работает следующим образом.. На входе 6 и 7 устройства подаются сигналы в виде двоичных кодов А: и В одноименных разрядов операн дов, с выхода элемента равнозначности 1 входные сигналы А; и В поступ ют на вход элемента равнозначности 3, второй вход которого служит управ ляющим входом и на него подается управляющий сигнал Ц -. С выхода элемента равнозначности 3 снимается сигнал- суммы или разности, определяв мый логическим выражением S- (Л-В, V ,) и, V )ir, На элемент равноэначносхд 2 по входу 10 устройства подается сигнал переноса или замена Pj из предьздущего разряда, а на вход 11 подается двоичный 1Л1гнал управления У С выхода элемента равнозначности 2 . сигнал равнозначности U подае ся на второй вход элемента И 5, с в хода которого сигнал логического произведения входных сигналов посту пает на первый вход элемента равнозначности 4, на второй вход которог подается двоичный управляющий сигна С выхода 13 элемента равнозначности 4 снимается двоичный переноса или заема, определяемы логическим выражением р - i.- .В.-ХРу., и (.V.,)Uj . Функциональные возможности сумми Р фще-вычитающего устройства приве. дены в таблице и определяются двоич ными сигналами управлений Ц ,. я з Таким образом, предлагаемое полое суммирующе-вычитающее устройство меет несложную cxeNiy и позволяет еализовать арифметические операции сложения и вычитания как над прямыми, так и над инверсными кодами двоичных чисел. Формула изобретения Сумирующе-вычитающее устройство,, каждый разряд которого содержит два элемента равнозначности, входы первого из которых подключены к входам соответствующих разрядов операндов устройства, а выход - к первому входу второго элемента равнозначности, выход которого является выходом суммы данного разрядаустройства , отличающееся тем, что, с целью расширения функциональных возможностей, заключающихся в обеспечении сложения и вычитания как прямых, так и инверсных кодов операндов, каждый разряд устройства дополнительно содержит третий и четвертый элементы равнозначности и элемент И, причем второй вход второго элемента равнозначности соединен с первой управляющей шиной устройства, первый вход, элемента И соединен с выходом первого элемента равнозначности, а второй вход - с выходом третьего элемента равнозначности, входы которого подключены к входу переноса (заема) из предьщущего разряда устройства и второй управляющей шине устройства, выход элемента И соединен с первым входом четвертого элемента равнозначности, второй вход которого подключен к третьей управляющей шине устройства, а выход - к выходу переноса (заема) из данного разряда устройства. Источники информации, пtинятыe во внимание при экспертизе 1.Авторское свидетельство СССР № ,174438, кл,,Q 06 F 7/50, 1964. 2.Патент Японии № 50-13068, кл. 97 (7) Е 312.1, 1975.

tit S

t/t

Авторы

Даты

1979-06-15—Публикация

1977-08-01—Подача