первым входом третьего элемента ИЛИ и с первым информационным входом коммутатора, второй вход третьего элемента ИЛИ соединён с выходом второго элемента И, а выход подключен к первому входу первого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом четвертого элемента ИЛИ-НЕ, а выход - с выходом знакового разряда устройства, третий вход первого элемента И соединен с первыми входами второго и третьего элементов И, четвертого элемента ИЛИ-НЕ, второго элемента РАВНОЗНАЧНОСТЬ и подключен к выходу третьего элемента РАВНОЗНАЧНОСТЬ, первый и второй входы которого соединены с входами знаковых разрядов первого и второго операндов устройства и с соответствующими управляющими входами коммутатора,а также с первым и Bt opbM входами элемента И-НЕ, выход которого подключен к второму входу второго элемента И, второй вход третьего элемента И соединен с выходом компаратора, а выход третьего элемента И соединен с выходом

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки цифровой информации, например в устройсвах нормализации изображений.

Целью изобретения является расширение функциональных возможностей устройства за счет осуществления операции вычитания операндов со своими знаками, а также передачи one- рандов на вькод устройства со своими знаками.

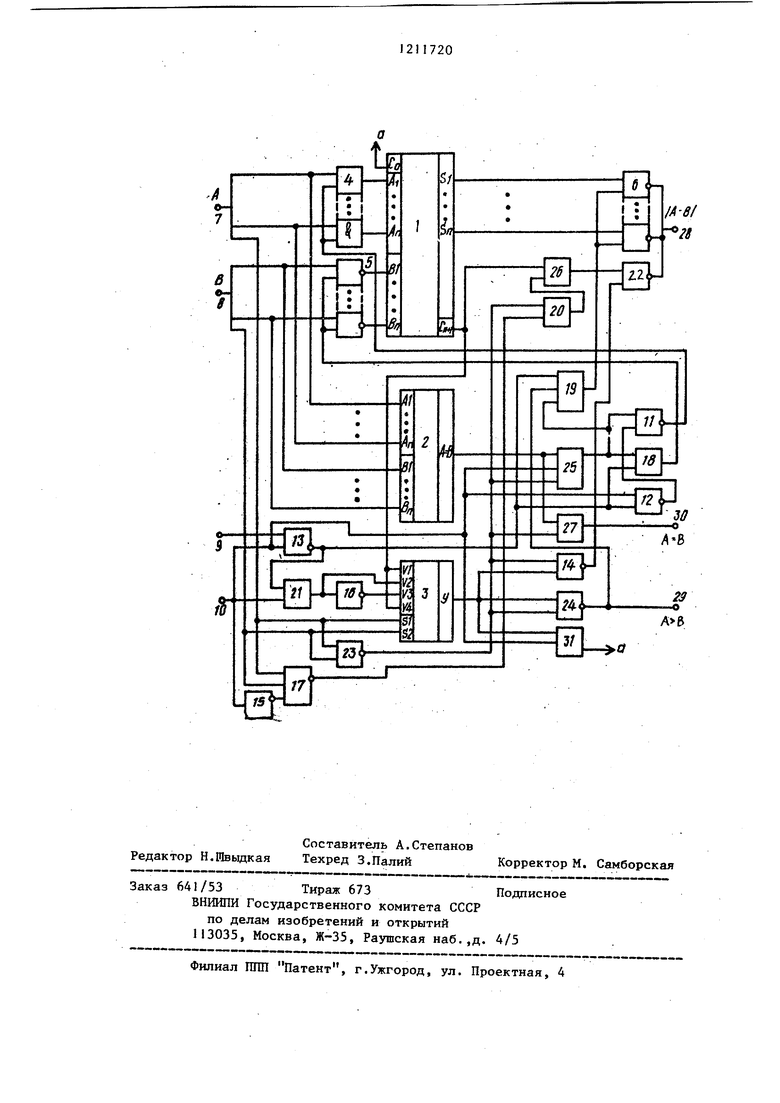

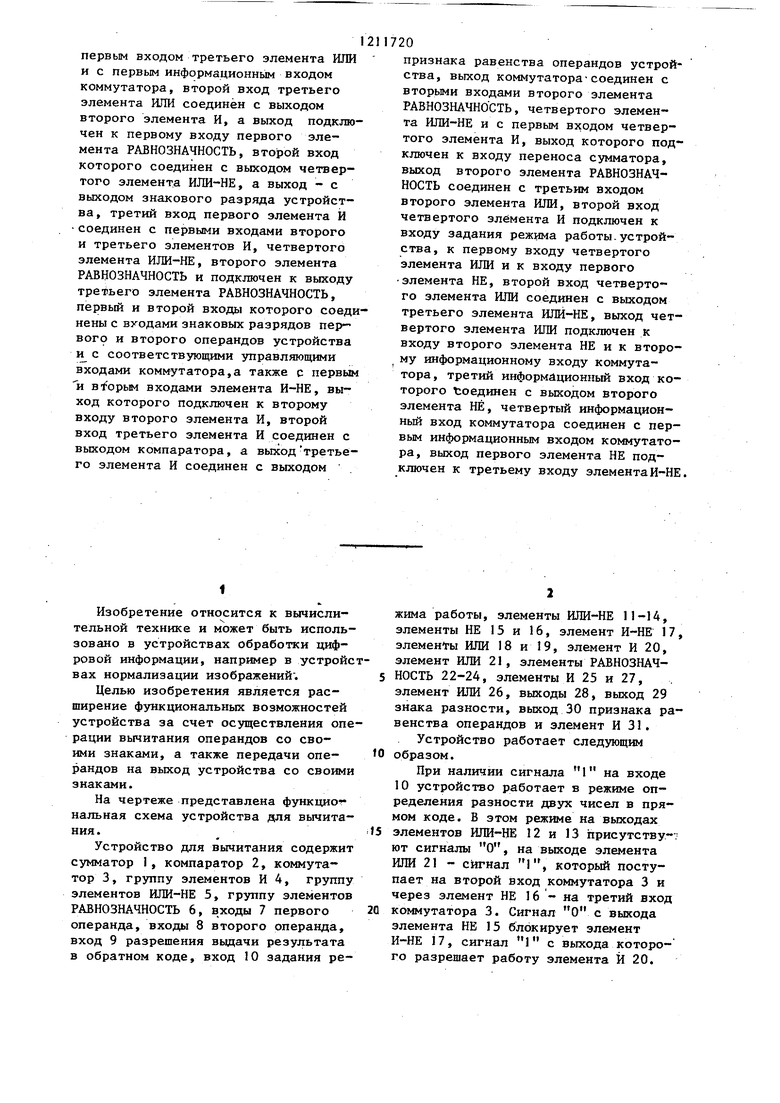

На чертеже представлена функциог нальная схема устройства для вычитания.

Устройство для вычитания содержит сумматор 1, компаратор 2, коммутатор 3, группу элементов И 4, группу элементов ИЛИ-НЕ 5, группу элементов РАВНОЗНАЧНОСТЬ 6, входы 7 первого операнда, входы 8 второго операнда, вход 9 разрешения выдачи результата в обратном коде, вход 10 задания ре720

признака равенства операндов устройства, выход коммутатора-соединен с вторыми входами второго элемента РАВНОЗНАЧНОСТЬ, четвертого элемента ИЛИ-НЕ и с первым входом четвертого элемента И, выход которого подключен к входу переноса сумматора, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом второго элемента ИЛИ, второй вход четвертого элемента И подключен к входу задания режима работы.устройства, к первому входу четвертого элемента ИЛИ и к входу первого элемента НЕ, второй вход четвертого элемента ИЛИ соединен с выходом третьего элемента ИЛИ-НЕ, выход четвертого элемента ИЛИ подключен к входу второго элемента НЕ и к второму информационному входу коммутатора, третий информационный вход которого Соединен с выходом второго элемента НЕ, четвертый информационный вход коммутатора соединен с первым информационным входом коммутатора, выход первого элемента НЕ подключен к третьему входу элемента И-НЕ.

жима работы, элементы ИЛИ-НЕ 11-14, элементы НЕ 15 и 16, элемент И-НЕ 17, элементы ИЛИ 18 и 19, элемент И 20, элемент ИЛИ 21, элементы РАВНОЗНАЧНОСТЬ 22-24, элементы И 25 и 27, элемент ИЛИ 26, выходы 28, выход 29 знака разности, выход 30 признака равенства операндов и элемент И 31.

Устройство работает следующим образом.

При наличии сигнала 1 на входе 10 устройство работает в режиме определения разности двух чисел в прямом коде. В этом режиме на выходах элементов ИЛИ-НЕ 12 и 13 присутству--.- ют сигналы О, на выходе элемента ИЛИ 21 - сигнал , который поступает на второй вход коммутатора 3 и через элемент НЕ I6 - иа третий вход коммутатора 3. Сигнал О с выхода элемента НЕ 15 блокирует элемент И-НЕ 17, сигнал 1 с выхода которо- го разрешает работу элемента И 20.

3

Сигнал О с элемента ИЛИ-НЕ -13 разрешает работу элемента ИЛИ-НЕ 12 и элементов ИЛИ 18 и 19. Сигнал О с выхода элемента ИЛИ-НЕ 12 разрешает работу элемента ИЛИ-НЕ 11.

Рассмотрим случай, когда опе ран- ды А и В положительны.

Если уменьшаемое больше вычитае- мого, то на выходе переноса сумматора 1 - сигнал 1, на выходе компаратора 2 - сигнал О. При этом на выходе элемента ИЛИ 18 и элемента ИЛИ-НЕ 11 образуются сигналы О и I соответственно, которые разрешают прохождение операндов с входов 7 и 8 через элементы И А и через элементы ИЛИ-НЕ 5 соответственно на входы сумматора,. Таким образом, на первую группу входов сумматора I поступает прямой код первого операнда, на вторую группу входов сумматора 1 т инверсный код второго операнда, а на вход переноса сумматора 1 - сигнал 1, который проходит через коммутатор 3 с выхода переноса сумматора 1. Следовательно, на выходах сумматора 1 получается разность операндов в прямом коде. На вьрсоде 29 фиксируется знак разности 1, который поступает через элемент ИЛИ 19 на входы элементов РАВНОЗНАЧНОСТЬ 6. Таким образом, на выходах 28 разность двух операндов получается в прямом коде.

Если уменьшаемое меньше вычитаемого, то на выходе переноса сумматора 1 - сигнал О, который проходит через коммутатор 3 и поступает на вход переноса сумматора 1. Как и в предьщущем случае, элементы И 4 и элементы ИЛИ-НЕ 5 не блокированы, та как на выходе элемента И 25 образуется сигнал О. В этом случае на выходах сумматора 1 образуется разность операндов в инверсном коде. На выходе 29 фиксируется знак разности О. На выходах 28 разность операндов получается в прямом коде.

Если уменьшаемое равно вычитаемому, то на выходе компаратора 2 и элемента И 25 получаются сигналы 1 На выходе элемента ИЛИ 18 и элемента ИЛИ-НЕ 11 - сигналы 1 и О соответственно, которые блокируют прохождение операндов с входов 8 и 7. На входы элементов РАВНОЗНАЧНОСТЬ 6 поступает сигнал 1.

0

5

1720

На входы сумматора 1 поступают нулевые коды. На выходе переноса сум- матора 1 - сигнал О, который формирует на выходе 29 сигнал О. На 5 выходах сумматора 1 формируется нулевой код разности, который поступает на выход 2S. На выходе 30 фиксируется равенство операндов сигналом 1. I

Рассмотрим случай, когда операнды

А и В отрицательны.

Этот случай аналогичен случаю, когда А и В положительны. На выход элемента РАВНОЗНАЧНОСТЬ 22 поступает сигнал О.

Если уменьшаемое больше вычитаемого, то на выходе переноса сумматора 1 - сигнал 1, на выходе сумматора 1 и на выходах 28 получается разность двух операндов в прямом коде, на выходе 29 - сигнал 1.

Если уменьшаемое меньше вычитаемого , то на выходе переноса сумматора 1 формируется сигнал О, на выходах сумматора 1 получается разность операндов в инверсном коде, на выходе устройства 28,- разность операндов в прямом коде, на выходе 29 - сигнал О.

Если уменьшаемое равно вычитаемому, то на выходе компаратора 2 сигнал 1, на выходе устройства 28- нулевой код, на выходе 29 - сигнал

0

5

0

О

, на выходе 30 фиксируется равенство операндов в виде сигнала 1.

Рассмотрим случай, когда операнд А отрицательный, а операнд В положительный.

На выходе элемента РАВНОЗНАЧНОСТЬ 23 и на выходе 29 формируется сигнал О. Сигнал с выхода элемента РАВНОЗНАЧНОСТЬ 23 запрещает работу элемента И 20, который в свою редь разрешает работу элемента ИЛИ

26. На вторые входы элемента РАВНОЗНАЧНОСТЬ 22 и группы 6 элементов РАВНОЗНАЧНОСТЬ поступает сигнал О, на выходе 30 фиксируется сигнал О. На выходе элемента И 25 и элемента ИЛИ 18 формируется сигнал О, а на выходе элемента ИЛИ-НЕ 11 - сигнал . Эти сигналы поступают соответственно на группы А и 5 элементов И и ИЛИ-НЕ. Таким образом, на

первую группу входов сумматора 1 операнд А поступает в инверсном, коде, на вторую группу входов сумматора I операнд В постзтает также в инверсном коде. Таким образом, на выходах сумматора 1 образуется разность двух операндов в инверсном коде. На выходе переноса сумматора I может получиться сигнал как в виде О, так и в виде I. На выходе 28 устройства получается разность операндов в .прямом коде.

Аналогично работает устройство и при положительном А н отрицательном В операндах.

При наличии нулевого сигнала на входе 10 задания режима работы устройство работает в режиме передачи на выход 28 лнбо уменьшаемого, либо вычитаемого (в зависимости от сигнала на входе 9 разрешения выдачи результата в обратном коде). В этом режиме на выходе элемента И 25 получается сигнал О, который поступает на входы элемента ИЛИ Г8 и элемента ИЛИ-НЕ 11, а также на вход элемента ИЛИ 19.

Если на входе 9 присутствует сигнал О, то на выходе элемента ИЛИ- НЕ 13 - сигнал 1, который через

элемент ИЛИ 21 поступает на второй вход коммутатора 3, на третий вход коммутатора 3 поступает сигнал О. Сигнал 1 с выхода элемента Ш1И-НЕ 13 поступает также через элемент ИЛИ 19 на вторые входы группы 6 элементов РАВНОЗНАЧНОСТЬ. На вторые входы группы 5 элементов ИЛИ-НЕ сигнал

} nocTynaet через элемент ИЛИ 18, . тем самым блокируя их работу, на второй вход элемента ШШ-НЕ 12, а с него в виде логического О - на вход элемента ИЛИ-НЕ 11, с выхода которого в виде логической 1 на вторые входы элементов И группы 4, разрешая их работу.

Таким образом, на сумматор 1 (на первую группу входов) поступает операнд А, а на вторую - нулевой код. ли оба операнда положительны, сигнал с выхода переноса сумматора 1 в виде О поступает на вход переноса сумматора 1. На выходе устройства 28 фиксируется прямой код операнда А, знаковый разряд которого сигналом О снимается с элемента РАВНОЗНАЧНОСТЬ 22.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1983 |

|

SU1133592A1 |

| Устройство для вычитания | 1985 |

|

SU1277097A1 |

| Устройство для вычитания | 1984 |

|

SU1215109A2 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для обработки телединамограмм глубинно-насосных скважин | 1988 |

|

SU1671843A1 |

| УСТРОЙСТВО КАСКАДНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ, ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА И МАКСИМАЛЬНЫХ ГРУПП | 2019 |

|

RU2701709C1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU940168A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Суммирующе-вычитающее устройство | 1986 |

|

SU1363192A1 |

| Титца У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1983, с | |||

| Ленточный тормозной башмак | 1922 |

|

SU337A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Устройство для вычитания | 1983 |

|

SU1133592A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-18—Подача