1

Изобретение относится к автоматике и вгз1числительной технике и может быть использовано в специализированных вычислительных устройствах, устройствах контроля и обработки информации ,

Цель изобретения - расширение области применения за счет возможности получения трех результатов сравнения

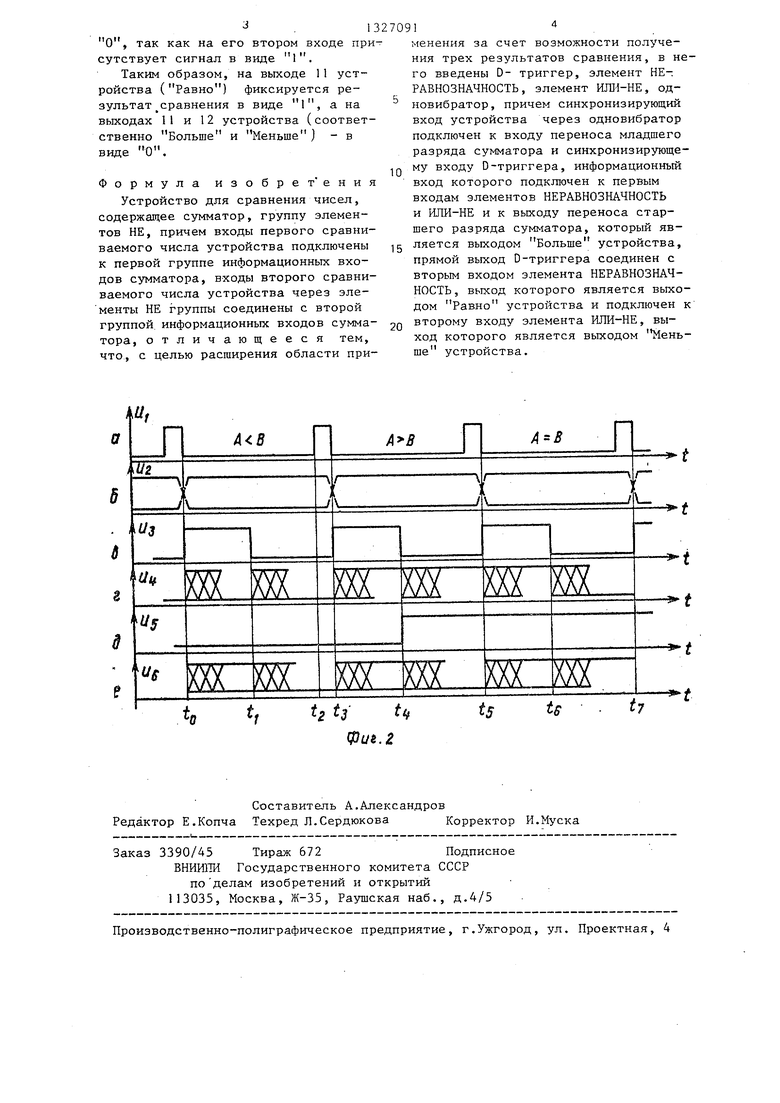

На фиг.1 изображена структурная схема устройства; на фиг.2 - эпюры напряжений, поясняющие работу пред- .лагаемого устройства.

Устройство для сравнения чисел содержит сумматор 1, одновибратор 2, группу элементов 3 НЕ, D-триггер 4, элемент 5 НЕРАВНОЗНАЧНОСТЬ,. элемент 6 ВХОДЫ 7 первого сравниваемого числа, входы 8 второго сравниваемого числа, синхронизирующий вход 9-устройства, выходы 10-12 устройства.

Устройство работает следующим образом.

В момент времени t, (см.фиг.2) происходит смена информации (эпюры и ,1)2) на входах первого 7 и второго 8 чисел. На первую группу входов сумматора I поступает прямой код первого числа. На втор-ую группу входов сумматора I поступает инверсный код второго числа с выходов элементов 3 НЕ, На вход однЪвибратора 2 с входа 9 поступает импульс (эпюра U) сопровождения входных чисел. По спаду этого импульса на выходе одновиб( эпюра и,), длительность которого выбирается больше длительности переходного процесса на выходе переноса сумматора 1 . Таким образом, в интерваое времени от t до t на вход переноса сумматора 1 поступает сигнал в виде l, а а в интервале времени от t до t, - сигнал в виде О.

Если код числа с входа 7 меньше по величине, чем код числа с входа 8, то на выходе переноса сумматора 1 в момент времени t (эпюра U) присутствует сигнал в виде О. Этот сигнал по спаду импульса с выхода од- новибратора 2 записывается в D-триггер 4. В момент времени t на выходе переноса сумматора 1 также присутствует сигнал в виде О. Таким образом, на первом и втором входах элемента 5 НЕРАВНОЗНАЧНОСТЬ к моменту фиксации результата сравнения (эпю912

ра и - интервал времени от t до tj) присутствует сигнал в виде О. Следовательно, на выходе элемента 5 НЕРАВНОЗНАЧНОСТЬ будет сигнал в виде О, а на выходе элемента 6 ИЛИг НЕ - сигнал в виде 1, так как на его первом и втором входах присутствует сигнал в виде О.

Таким образом, на выходах 10 и 11- устройства (соответственно Больше и Равно) фиксируется результат сравнения в виде О, а на выходе 2 устройства (Меньше) - в виде .

Если код числа с входа 7 больше по величине, чем код числа с входа 8, то то на выходе переноса сумматора 1 в момент времени t (эпюра U) присутствует сигнал в виде I. Этот сиг-пал по спаду импульса с выхода одно- вибратора 2 записывается в D-триггер 4. В момент времени t (эпюра U) на выходе переноса сумматора 1 также присутствует сигнал в виде 1. ТаКИМ образом, на первом и втором входах элемента. 5 НЕРАВНОЗНАЧНОСТЬ к моменту фиксации результата сравнения присутствует сигнал в виде 1. Следовательно , на выходе элемента 5

НЕРАВНОЗНАЧНОСТЬ будет сигнал в виде О. На выходе элемента 6 ИЛЙ-НЕ будет также сигнал в виде О, так как на его первом входе присутствует сигнал в виде 1.

Таким образом, на выходе 10 устройства (Больше) фиксируется результат i сравнения в виде I, а на выходах 11 и 12 устройства (соответственно Равно и Меньше) в виде О.

Если код числа с входа 7 равен по величине коду числа с входа 8, то на выходе переноса с гмматора 1 в момент времени t / (эпюра Uij) присутствует сигнал в виде . Этот сигнал по спаду импульса с выхода одно- вибратора 2 записывается в D-триггер 4. В момент времени t-j (эпюра U)

на выходе переноса сумматора 1 присутствует сигнал в виде О. Таким образом, на первом и втором входах элемента 5 НЕРАВНОЗНАЧНОСТЬ к моменту фиксации результата сравнения

присутствуют соответственно сигналы 1 и О. Следовательно, на выходе элемента 5 НЕРАВНОЗНАЧНОСТЬ будет сигнал в виде 1. На выходе элеента 6 ИЛИ-НЕ будет сигнал в виде

3

О

, так как на его втором входе присутствует сигнал в виде 1.

Таким образом, на выходе 1I устройства (Равно) фиксируется результат сравнения в виде 1, а на выходах 11 и 12 устройства (соответственно Больше и Меньше ) - в виде О.

Формула изобрет ения

Устройство для сравнения чисел, содержащее сумматор, группу элементов НЕ, причем входы первого сравниваемого числа устройства подключены к первой группе информационных входов сумматора, входы второго сравниваемого числа устройства через эле- менты НЕ группы соединены с второй группой информационных входов сумматора, отличающееся тем, что, с целью расширения области приt2 t3 Фиб.2

Составитель А.Александров Редактор Е.Копча Техред Л.Сердюкова Корректор И.Муска

Заказ 3390/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

1327091

менения за счет возможности получения трех результатов сравнения, в него введены D- триггер, элемент НЕ-; РАВНОЗНАЧНОСТЬ, элемент ИЛИ-НЕ, од- новибратор, причем синхронизирующий вход устройства через одновибратор подключен к входу переноса младшего разряда сумматора и синхронизирующеQ му входу D-триггера, информационный вход которого подключен к первым входам элементов НЕРАВНОЗНАЧНОСТЬ и ИЛИ-НЕ и к выходу переноса старшего разряда сумматора, который яв5 ляется выходом Больше устройства, прямой выход D-триггера соединен с вторым входом элемента НЕРАВНОЗНАЧНОСТЬ, выход которого является выходом Равно устройства и подключен к

Q второму входу элемента ИЛИ-НЕ, выход которого является выходом Меньше устройства.

ts

и

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1984 |

|

SU1215109A2 |

| СПОСОБ ФОРМИРОВАНИЯ КОМАНД УПРАВЛЕНИЯ НА РАКЕТЕ, ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА, РАКЕТА, ВРАЩАЮЩАЯСЯ ПО УГЛУ КРЕНА, СПОСОБ ФОРМИРОВАНИЯ ДВУХСКАТНОГО ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА | 2005 |

|

RU2283466C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для вычитания | 1984 |

|

SU1211720A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Устройство для сортировки информации | 1986 |

|

SU1386989A2 |

| Устройство для арифметической илОгичЕСКОй ОбРАбОТКи дВОичНыХчиСЕл | 1979 |

|

SU842795A1 |

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| М.: Связь, 1977, с.143, рис.5.526 | |||

| Устройство для определения экст-РЕМАльНыХ чиСЕл | 1979 |

|

SU824193A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1984-06-21—Подача