1

Изобретение относится к импульсной технике и может быть использовано в цифровых автоматических системах измерения и управления.

Цель изобретения повышение точности путем улучшения равномерности выходного частотно-импульсного сигнала.

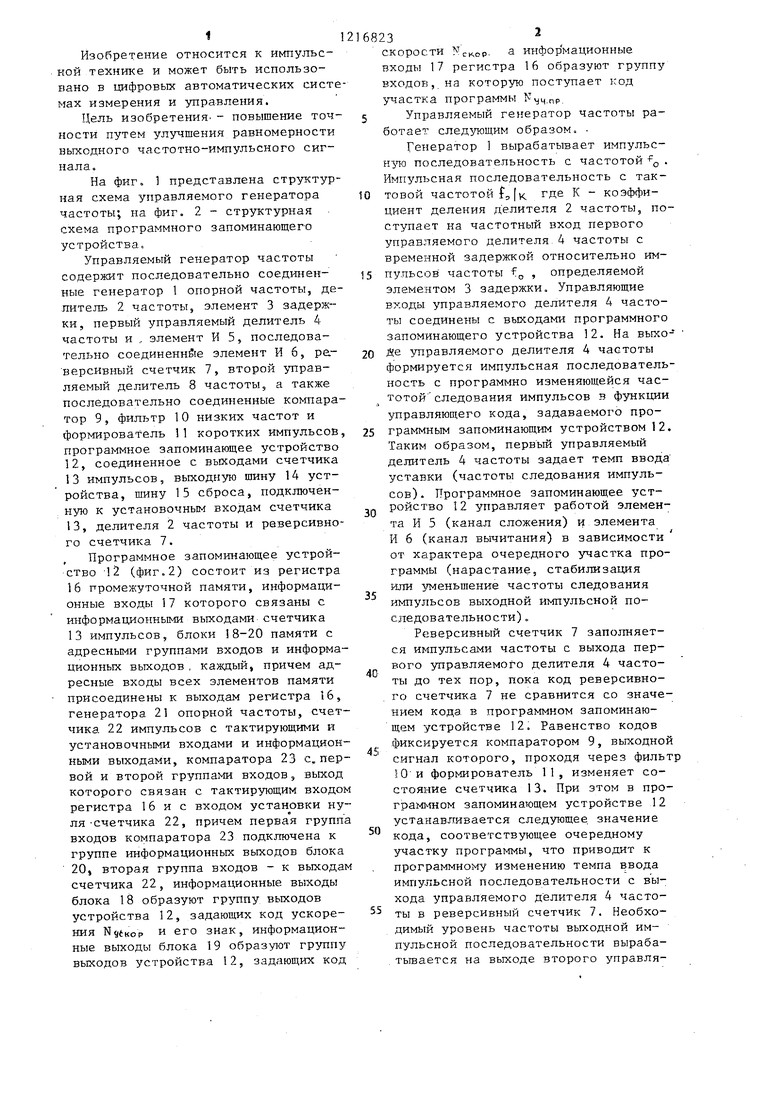

На фиг. 1 представлена структурная схема управляемого генератора частоты; на фиг. 2 - структурная схема программного запоминающего устройства.

Управляемый генератор частоты содержит последовательно соединенные генератор 1 опорной частоты, делитель 2 частоты, элемент 3 задержки, первый управляемый делитель 4 частоты и , элемент И 5, последовательно соединеннй е элемент И 6, ре- версивный счетчик 7, второй управляемый делитель 8 частоты, а также последовательно соединенные компаратор 9, фильтр 10 низких частот и формирователь 11 коротких импульсов программное запоминающее устройство

12,соединенное с выходами счетчика 13 импульсов, выходную шину 14 устройства, шину 15 сброса, подключенную к установочным входам счетчика

13,делителя 2 частоты и реверсивного счетчика 7.

Программное запоминающее устройство 12 (фиг.2) состоит из регистра 16 промежуточной памяти, информационные входы 17 которого связаны с информационными выходами счетчика 13 импульсов, блоки 8-20 памяти с адресными группами входов и информационных выходов, каждый, причем адресные входы всех элементов памяти присоединены к выходам регистра 16, генератора 21 опорной частоты, счетчика 22 импульсов с тактирующими и установочными входами и информационными выходами, компаратора 23 с, первой и второй группами входов, выход которого связан с тактирующим входом регистра 16 и с входом установки нуля-счетчика 22, причем первая группа входов компаратора 23 подключена к группе информационных выходов блока 20, вторая группа входов - к выходам счетчика 22, информационные выходы блока 18 образуют группу выходов устройства 12, задающих код ускорения N jtKop и его знак, информационные выходы блока 19 образуют группу выходов устройства 12, задающих код

68232

скорости NCKOP. а инфор мационные входы 17 регистра 16 образуют группу входов, на которую поступает код участка программы Ntj.np.

Управляемый генератор частоты работает следующим образом. .

Генератор 1 вырабатывает импульс- HiTo последовательность с частотой . Импульсная последовательность с так0 товой частотой f,, к где К - коэффициент деления д елителя 2 частоты, поступает на частотный вход первого управляемого делителя 4 частоты с време яной задержкой относительно им5 пульсов частоты f, , определяемой элементом 3 задержки. Управляющие входы управляемого делителя 4 частоты соединены с выходами программного запоминающего устройства 12. На выхо0 йе зтгравляемого делителя 4 частоты формируется импульсная последовательность с программно изменяющейся частотой следования импульсов в функции управляющего кода, задаваемого про5 граммным запоминающим устройством 12. Таким образом, первый управляемый делитель 4 частоты задает темп ввода уставки (частоты следования импульсов). Программное запоминающее уст0

5

0

ройство 12 управляет работой элемента И 5 (канал сложения) и элемента И 6 (канал вычитания) в зависимости от характера очередного участка программы (нарастание, стабилизация или уменьшение частоты следования импульсов выходной импульсной последовательности) .

Реверсивный счетчик 7 заполняется импульсами частоты с выхода первого управляемого делителя 4 частоты до тех пор, пока код реверсивно- , го счетчика 7 не сравнится со значением кода в программном запоминающем устройстве 12. Равенство кодов . фиксируется компаратором 9, выходной сигнал которого, проходя через фильтр 10 и формирователь 11, изменяет состояние счетчика 13. При этом в про- гpaмl ffloм запоминающем устройстве 12 устанавливается следующее значение кода, соответствующее очередному участку программы, что приводит к программному изменению темпа ввоц,а импульсной последовательности с выхода управляемого д елителя 4 часто- ты в реверсивный счетчик 7, Необходимый уровень частоты выходной импульсной последовательности вырабатывается на выходе второго управля0

емого делителя частоты 8, на частотный вход которого поступают импульсы опорной частоты f непосредственно с выхода генератора 1. Частота выходной последовательности пропорциональна коду числа, записанного в счетчик 7. Непосредственная связь частотного входа управляемого делителя 8 частоты с генератором позволяет произвести прямое преобразование опорной частоты по алгоритму циклически работающего преобразователя так, что количество импульсов опорной частоты, поступающее на шину 14, в каждом дикле равно значению кода, поступающего на управляю- .щие входы управляемого делителя 8 частоты с выходов реверсивного счетчика 7.

Для устранения возможных сбоев в работе устройства у которые могут возникать за счет того, что компаратор 9 и управляемый делитель 8 частоты могут ощибочно регулировать на промежуточное значение кодовых комбинаций на выходах реверсив юго счетчика 7 в моменты переходных процессов в последнем при поступлении счетных импульсов на его входы, в устройстве использован элемент 3 задержки импульсов опорной частоты в канале записи числа в счетчиках 7 и на частотном входе делителя 8 и фильтр 10 низких частот, запрещающий прохождение на вход счетчика. 13 коротких импульсов помех, которые могут иметь место на выходе компаратора 9 в момент переходного процесса в счетчике 7.

I

Программное задающее устройство

12 содержит три массива перепрограммируемой памяти - блоки 18-20, в которых записаны код ускорения ( с учетом знака), код скорости ( и код длительности участка программы (КЧЧ.ПР ) Переход к считыванию NycKop. и NCKOP очередного участка программы происходит после того, как на выходе компаратора 23, сравнивающего коды заданной и текущей длительности участка программы, появляется сигнал равенства кодов, который обнуляет счетчик 22 и дает команду переноса кода участка программы (Nt,4 пр ) в регистр 16 памяти с выходов счетчика 13. Счетчик 22 заполняется импульсами тактовой частоты генератора 21. В частном случае в

качестве задающего устройства 12 быть использована ЭВМ. В начале каждого цикла работы предлагаемого устройства подается на шине 15 импульс сброса, обнуляющий счетчики 2, 7, 13 и регистр 16.

Формула изоб ретения

1. Управляемый генератор частоты, содержаций генератор опорной частоты, первый и второй управляемые делители частоты, реверсивный счетчик, шину импульса сброса, первая группа информащ онных выходов программного запоминающего устройства подключена к информационным входам первого управляемого делителя частоты, выходы реверсивного счетчика подключены к информационным входам второго управляемого делителя частоты, счетчик импульсов, первый элемент И, о т л и- чающийся тем, что, с целью повышения точности, в него введены

делитель частоты, элемент задержки, второй элемент И и последовательно соединенные компаратор, фильтр низких частот и форьшрователь коротких импульсов, выход которого подключен

к счетному входу счетчика импульсов, установочный вход-которого подключен к ишне импульса сброса и к установочному входу программного запоминающего устройства, выходы счетчика импульсов подключены к входам программного запоминающего устройства, втр- рая группа ннфop a ;иoнньrx выходов которого подключена к первой группе входов компаратора, вторая группа

входов к.оторого соединена с выхопями

реверсивного счетчика, причем выход генератора спорной частоты соединен со счетным входом второго управляемого делителя частоты и через последовательно соединенные делитель частоты и элемент задержки со счетным входом первого управляемого делителя частоты, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых

подключены к первому и второму выходам программного запоминающего устройства, выходы первого и второго элементов И соединены с суммирующим и вычитающим входами реверсивного

счетчика соответственно, установочный вход которого подключен к шине импульса сброса и к установочному входу делителя частоты.

2. Генератор по п. 1, отличающийся тем, что программное запоминающее устройство содержит последовательно соединенные ре- ,гистр памяти, первый блок памяти, второй блок памяти, третий блок памяти и компаратор, вторые входы которого соединены через счетчик импульсов с выходом генератора опорной частоты, вьгход компаратора соединен со счетным входом регистра памяти, входы регистра памяти являются входами программного запоминающего устройства, выходы блоков памяти являются выходами программного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Цифровой фазометр | 1987 |

|

SU1458836A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

| Многоканальное устройство программного управления шаговыми двигателями | 1985 |

|

SU1320794A1 |

| Функциональный генератор | 1977 |

|

SU746581A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых автоматических системах измерения и управления. Цель изобретения - повышение точности путем улучшения равномерности выходного частотно-импульсного сигнала. Устройство содержит генератор 1 опорной частоты, делитель 2 частоты, элемент 3 задержки, управляемые делители 4 и 8 частоты, логические элементы И 5 и 6, реверсивный счетчик 7, компаратор 9, фильтр 10 низких частот, формирователь 11 корот- ; ких импульсов, программное .запоминающее устройство 12, счетчик 13 импульсов, шины - выходную 14, сброса 15. Функциональная схема программного запоминающего устройства приводится в описании изобретения. 1 з.п.- ф-лы. 2 ил. § (Л в (нА го 05 СХ) rsD 00

77

„

19

20

гЛ

| Формирователь импульсов с изменяемой частотой | 1977 |

|

SU617807A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Функциональный генератор частоты | 1978 |

|

SU758490A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-07—Публикация

1984-07-09—Подача