«

Изобретение относится к вычисли- тельной технике и может быть использовано в системах передачи цифровой информации.

Цель изобретения - повышение помехоустойчивости преобразования путем исключения сбоев.

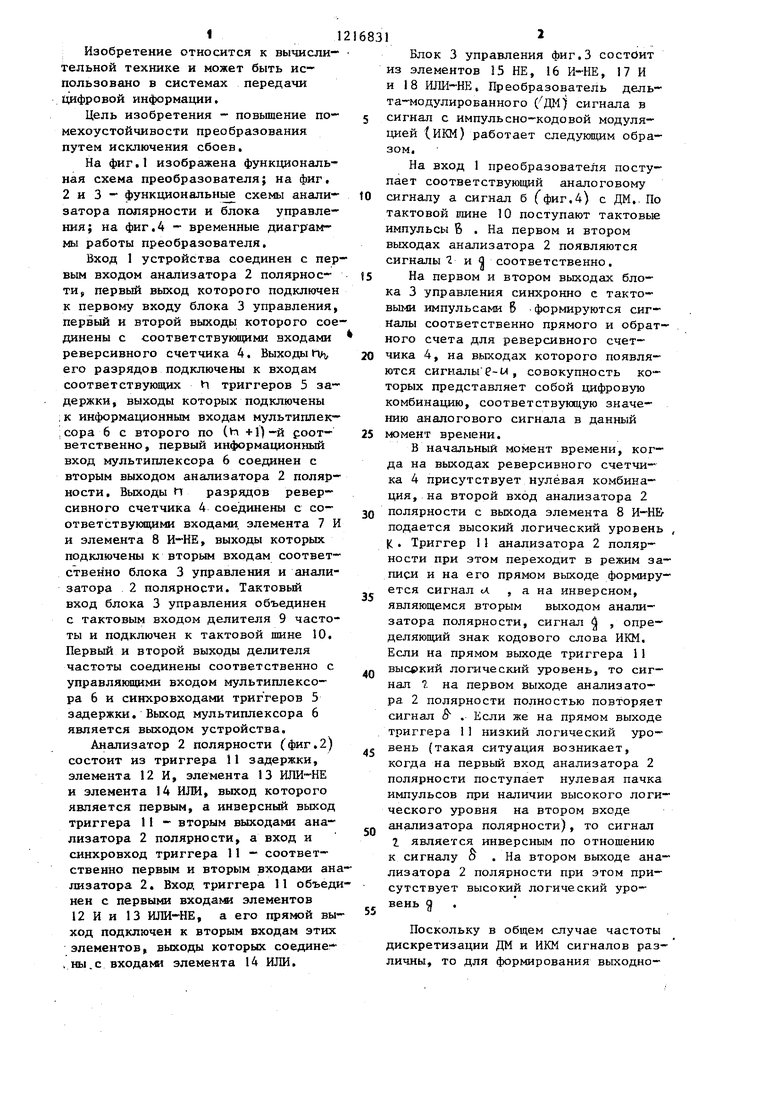

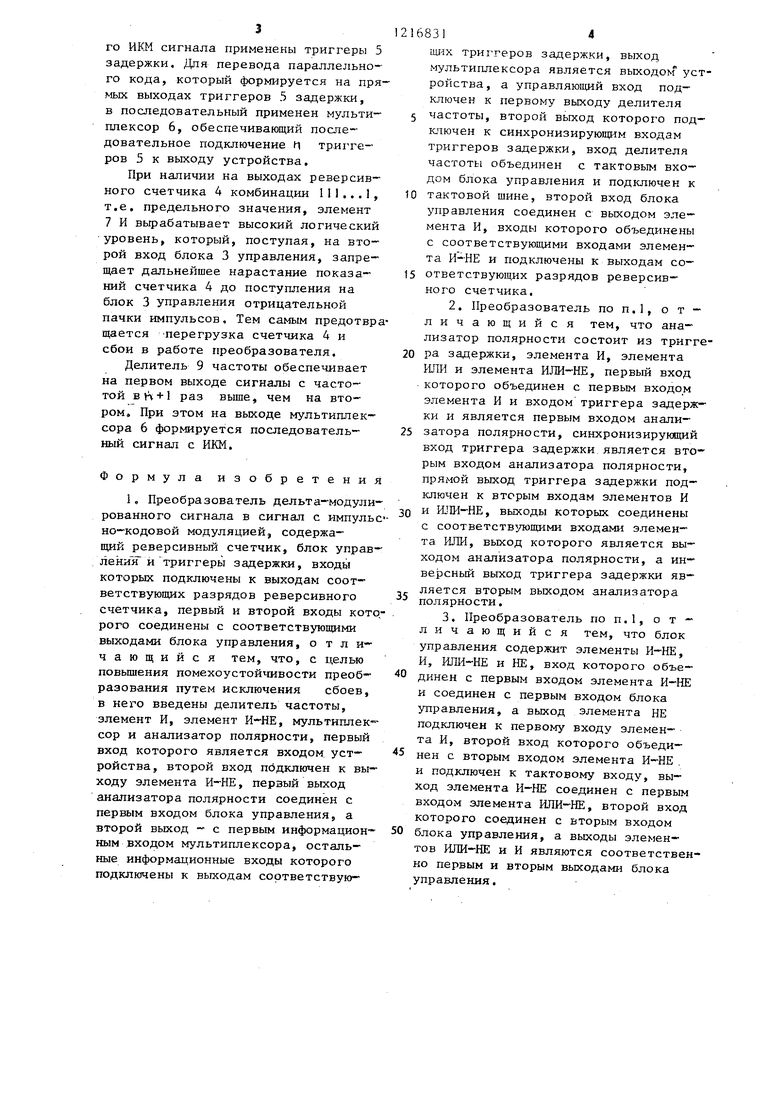

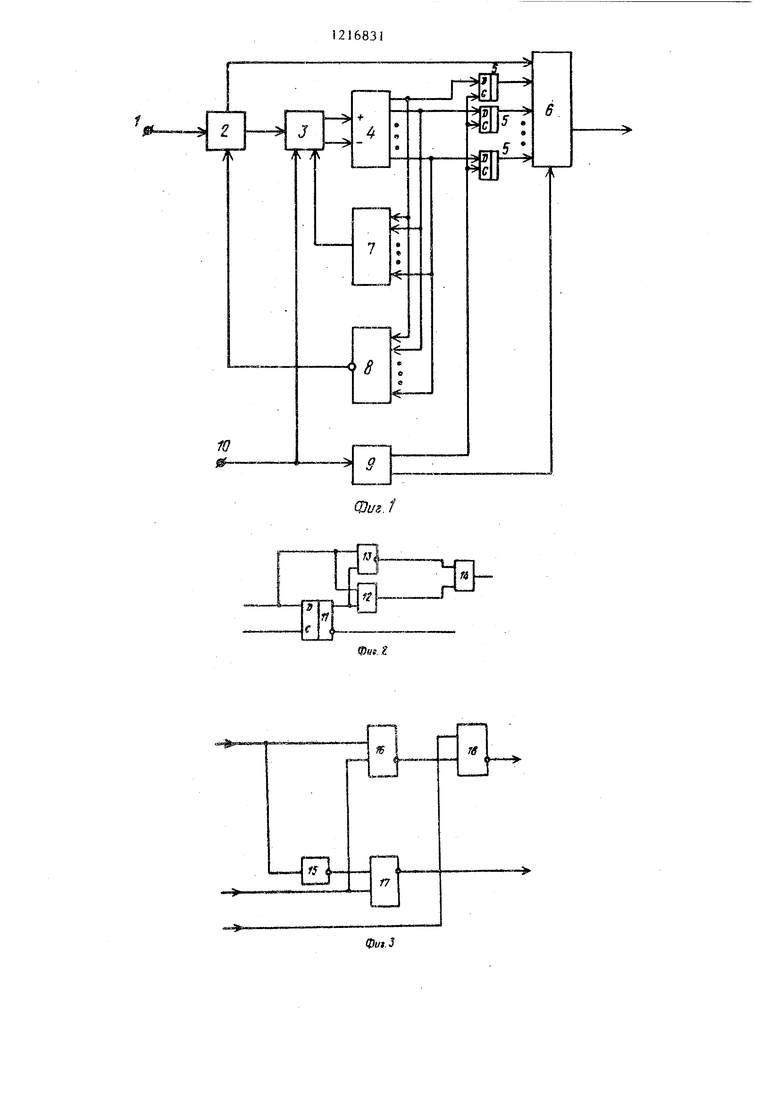

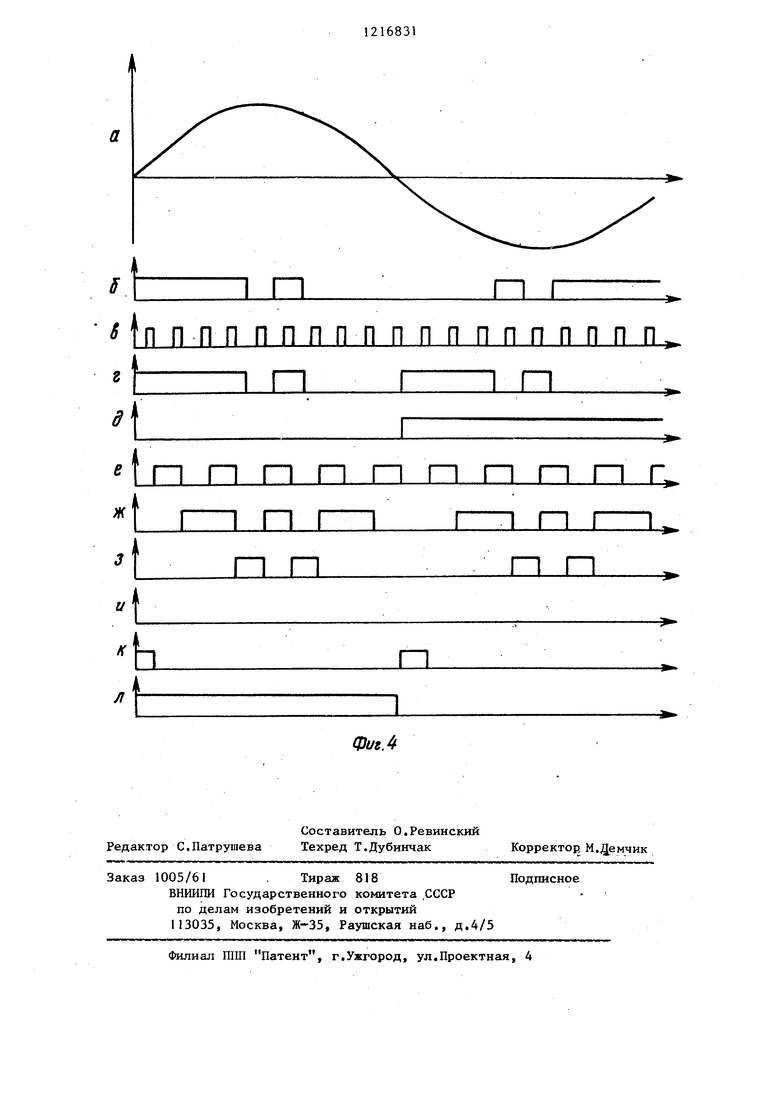

На фиг.1 изображена функциональная схема преобразователя; на фиг. 2 и 3 - функхщональные схемы анализатора полярности и блока управления; на фиг.4 - временные диаграммы работы преобразователя.

Вход 1 устройства соединен с первым входом анализатора 2 полярности, первый выход которого подключен к первому входу блока 3 управления, первый и второй выходы которого соединены с соответствукяцими входами реверсивного счетчика 4. Выходы v его разрядов подключены к входам соответствующих h триггеров 5 задержки, выходы которых подключены :к информационным входам мультиплек- j сора 6 с второго по (ь +1)-й f.ooT- ветственно, первый информационный

вход мультиплексора 6 соединен с вторым выходом анализатора 2 полярности. Выходы П разрядов реверсивного счетчика 4 соединены с соответствукяцими входами, элемента 7 И и элемента 8 И-НЕ, выходы которых подключены к вторым входам соответственно блока 3 управления и анализатора 2 полярности. Тактовый вход блока 3 управления объединен с тактовым входом делителя 9 частоты и подключен к тактовой шине 10. Первый и второй выходы делителя частоты соединены соответственно с управляющими входом мультиплексора 6 и синхровходами триггеров 5 задержки. Выход мультиплексора 6 является выходом устройства.

Анализатор 2 полярности (фиг.2) состоит из триггера 11 задержки, элемента 12 И, элемента 13 ШШ-НЕ и элемента 14 ИЛИ, выход которого является первым, а инверсный выход триггера 11 - вторым выходами анализатора 2 полярности, а вход и синхровход триггера 11 - соответственно первым и вторым входами анлизатора 2. Вход триггера 11 объеднен с первыми входа элементов 12 И и 13 ИЛИ-НЕ, а его прямой выход подключен к вторым входам этих элементов, выходы которых соедине- ны.с входаьи элемента 14 ИЛИ.

8312

Блок 3 управления фиг.З состоит из элементов 15 НЕ, 16 И-НЕ, 17 И и 18 ИЛИ-НЕ, Преобразователь дель- та-модулированного С ДМ) сигнала в

сигнал с импульсно-кодовой модуляцией (ИКМ) работает следующим образом.

На вход 1 преобразователя поступает соответствующий аналоговому

сигнапу а сигнал б (фиг.4) с ДМ.. По тактовой шине 10 поступают тактовые импульсы Б . На первом и втором выходах анализатора 2 появляются сигналы 2 и соответственно.

5 На первом и втором выходах блока 3 управления синхронно с тактовыми импульсами 6 формируются сигналы соответственно прямого и обратного счета для реверсивного счет0 чика 4, на выходах которого появляются сигналы е-И , совокупность которых представляет собой цифровую комбинацию, соответствующую значению аналогового сигнала в данный

5 момент времени.

В начальный момент времени, когда на выходах реверсивного счетчика 4 присутствует нулевая комбинация, на второй вход анализатора 2

Q полярности с выхода элемента 8 И-НЕ- подается высокий логический уровень , К. Триггер 1} анализатора 2 полярности при этом переходит в режим записи и на его прямом выходе формиру- ется сигнал а , а на инверсном, являющемся вторым выходом анализатора полярности, сигнал , определяющий знак кодового слова ИКМ. Если на прямом выходе триггера i1

.Q высркий логический уровень, то сигнал 7. на первом выходе анализатора 2 полярности полностью повторяет сигнал S . Если же на прямом выходе триггера 11 низкий логический уро-

е вень (такая ситуация возникает, когда на первый вход анализатора 2 полярности поступает нулевая пачка импульсов при наличии высокого логического уровня на втором входе

,- анализатора полярности), то сигнал 2. является инверсным по отношению к сигналу В . На втором выходе анализатора 2 полярности при этом присутствует высокий логический уро55 9

Поскольку в общем случае частоты дискретизации ДМ и ИКМ сигналов различны, то для формирования выходно-

го ИКМ сигнала применены триггеры 5 задержки. Для перевода параллельного кода, который формируется на прямых выходах триггеров 5 задержки, в последовательный применен мультиплексор 6, обеспечивающий последовательное подключение П триггеров 5 к выходу устройства.

При наличии на выходах реверсивного счетчика 4 комбинации 1 1 1 ... 1 , т.е. предельного значения, элемент 7 И вырабатывает высокий логический уровень, который, поступая, на второй вход блока 3 управления, запрещает дальнейшее нарастание показаний счетчика 4 до поступления на блок 3 управления отрицательной пачки импульсов. Тем самым предотврщается -перегрузка счетчика 4 и сбои в работе преобразователя.

Делитель 9 частоты обеспечивает на первом выходе сигналы с частотой в t4 +1 раз выше, чем на втором. При этом на выходе мультиплексора 6 формируется последовательный сигнал с ИКМ.

Формула изобретения

. Преобразователь дельта-модули рованного сигнала в сигнал с импуль но-кодовой модуляцией, содержащий реверсивный счетчик, блок управления и триггеры задержки, входы которых подключены к выходам соответствующих разрядов реверсивного счетчика, первый и второй входы кото рого соединены с соответствующими выходами блока управления, о т л и- чающийся тем, что, с целью повышения помехоустойчивости преобразования путем исключения сбоев, в него введены делитель частоты, элемент И, элемент И-НЕ, мультиплексор и анализатор полярности, первый вход которого является входом устройства, второй вход подключен к выходу элемента И-НЕ, первый выход анализатора полярности соединен с первым входом блока управления, а второй выход с первым информационным входом мультиплексора, остальные информационные входы которого подключены к выходам соответствую-

8314

auix триггеров задержки, выход мультиплексора является выходом устройства , а управляющий вход подключен к первому выходу делителя частоты, второй выход которого подключен к синхронизирующим входам триггеров задержки, вход делителя частоты объединен с тактовым входом блока управления и подключен к

тактовой шине, второй вход блока управления соединен с выходом элемента И, входы которого объединены с соответствующими входами элемента И-НЕ и подключены к выходам со-

ответствующих разрядов реверсивного счетчика.

2.Преобразователь по п.1, о т - личающийся тем, что анализатор полярности состоит из триггера задержки, элемента И, элемента ИЛИ и элемента ИЛИ-НЕ, первый вход которого объединен с первым входом элемента И и входом триггера задержки и является первым входом анали-

затора полярности, синхронизирующий вход триггера задержки является вторым входом анализатора полярности, прямой выход триггера задержки подключен к вторым входам элементов И

и ШШ-НЕ, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом анализатора полярности, а инверсный выход триггера задержки является вторым выходом анализатора полярности.

3.Преобразователь по п.1, о т - личающийся тем, что блок управления содержит элементы И-НЕ, И, ИЛИ-НЕ и НЕ, вход которого объединен с первым входом элемента И-НЕ и соединен с первым входом блока управления, а выход элемента НЕ подключен к первому входу элемента И, второй вход которого объеди-

нен с вторым входом элемента И-НЕ . и подключен к тактовому входу, выход элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с вторым входом

блока управления, а выходы элементов ШШ-НЕ и И являются соответственно первым и вторым выходами блока управления.

Wus. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией | 1983 |

|

SU1128385A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1988 |

|

SU1533006A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Преобразователь код-ШИМ | 1987 |

|

SU1462488A1 |

| Кодирующее устройство с дельтамодуляцией и импульсно-кодовой модуляцией | 1977 |

|

SU661789A1 |

| Кодирующее устройство с дельта-модуляцией и импульсно-кодовой модуляцией | 1984 |

|

SU1182681A2 |

| Устройство для измерения характеристики квантования передатчика сигналов с импульсно-кодовой модуляцией | 1980 |

|

SU946005A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Цель изобретения - повышение помехоустойчивости преобразования путем исключения сбоев. Устройство содержит анализатор полярности, вход которого является входом устройства, блок управления, СОСТОЯИ5ИЙ из элементов НЕ, И-НЕ, И и ШШ-НЕ, реверсивный счетчик, VI триггеров задержки, мультиплексор, элементы И и И-НЕ, делитель частоты, соединенный с тактовой шиной. Анализатор полярности состоит- из триггера и элементов И, ШШ-НЕ и И1Ш. 1 з.п. ф-лы, 4 ил.

«

-1 IB

re

а

I

1 n

и т

Составитель О.Ревинский Редактор С.Патрушева Техред Т.Дубинчак Корректор М.Демчик

Заказ 1005/61 . Тираж 818

ВНИИПИ Государственного комитета ,СССР по делам изобретеннй и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал П1Ш Патент, г.Ужгород, ул.Проектнаш, 4

гп г

фиг А

Подписное

| Преобразователь компандированногодЕльТА-пОТОКА B иКМ СигНАл | 1979 |

|

SU822354A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент Великобритании № 1321346, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-07—Публикация

1984-05-30—Подача