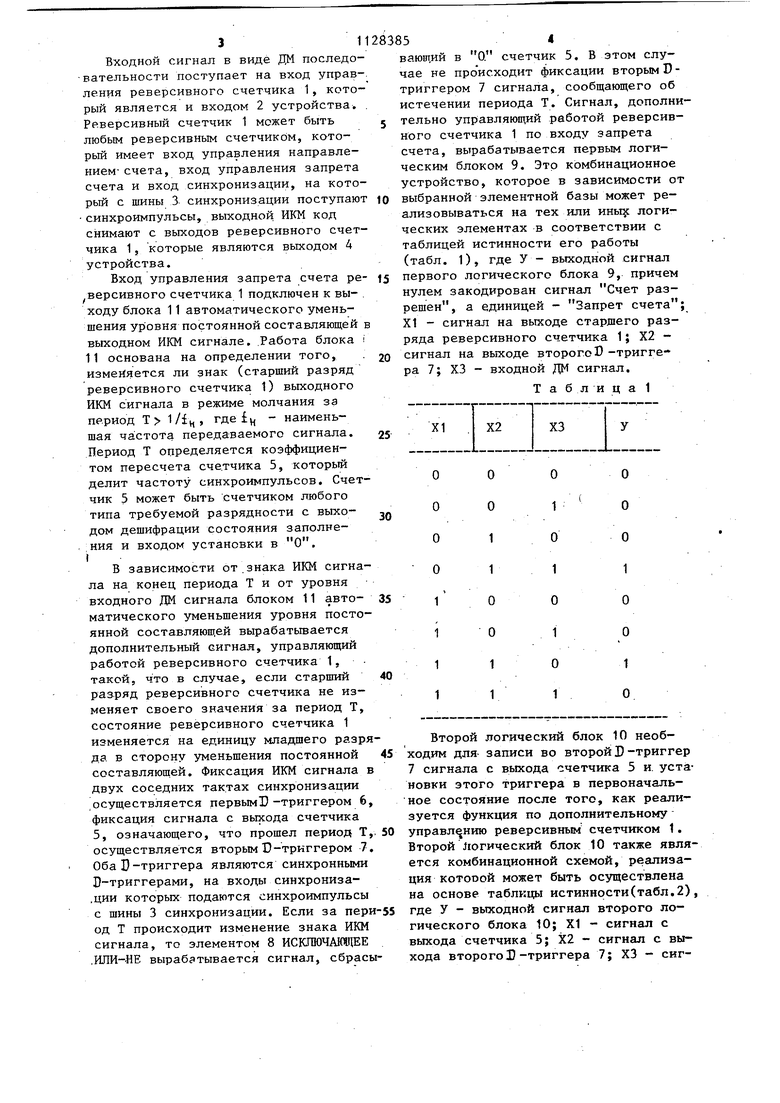

I Изобретение относится к импульсной технике и может быть- использовано в системах обработки и передачи цифровых сигналов, в которых применяется дельта-модуляция (ДМ) и импупьсно-кодовая модуляция (ИКМ). : Известно устройство для преобразования ДМ.сигналов в ИКМ, содержаще сумматоры, резисторы, умножители и постоянные запоминающие устройства Недостатком этого устройства является невысокая .помехоустойчивость Наиболее близким к изобретению техническим решением является уст-. ройство для преобразования дельтамодулированных сигналов в сигнал с ИКМ, содержащее реверсивный счетчик, D-триггер,D -вход которого соединен выходом старшего разряда реверсивного счет-чика, а вход синхронизации с шиной синхронизации, управляемый делитель частоты, например, счетчик и первый логический блок, а также высокочастотный дельта-модулятор, прямой и инверсный выходы которого через элементы И подключены к входу управления реверсивного счетчика, и генераторы тактовых импульсов 2J Недостатком известного устройства является низкая помехоустойчивость, что вызывает изменение уровня постоянной составляющей в выходном ИКМ сигнале при возникновении сбоев в ДМ сигнале и приводит к искажению передаваемых сигналов. Это обусловлено тем, что реверсивные счетчики являют ся идеальными интеграторами, вследствие чего они накапливают ошибки. Цель изобретения - повьппение помехоустойчивости. Цель достигается тем, что в преобразователь дельта-модулированно.го сигнала в сигнал с импульсно-кодовой модуляцией, содержащий реверсивный счетчик, первый Б-триггер,Dвход которого соединен с ыходом старшего разряда реверсивного счетчика, а вход синхронизации - с шиной синхронизации, счетчик и первый логический блок, введены второй логический блок, элемент ИСКЛЮЧАЩЕЕ ИЛИ-НЕ и второйD-триггер, вход синхронизации которого соединен с шиной синхронизации, входом синхронизации реверсивного счетчика и входом счетчика, выход которого соединен с первым входом второго логического блока .а вход установки в О счетчика - с 852 выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый вход которого соединен с выходом первогоD-триггера, а второй вход подключен к D -входу первогоD-триггера и первому входу первого логического блока, второй вход которого соединен с вторым входом второго логического блока и выходом второго D-триггера, третий вход первого блока соединен с входом устройства и входом управления реверсивного счетчика, а выход - с входом запрета счета реверсивного счетчика и третьим входом второго логического блока, выход которого соединен сD -входом второго -триггера. На чертеже представлена функциональная схема устройства. Устройство содержит реверсивный счетчик 1, вход управления которого соединен с входом 2 устройства, вход синхронизации соединен с шиной 3 синхронизации, выходы реверсивного счетчика 1 являются выходом 4 устройства, счетчик 5, первый и второйDтриггеры 6 и 7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый и второй логические блоки 9 и 10, причем шина 3 синхронизации соединена с входом счетчика 5 и входами синхронизации первого и второгоD-триггеров 6 и 7, а выход старшего разряда реверсивного счетчика 1 подключен к первому входу первого логического блока. 9, к первому входу элемента 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и к входу первогоD-триггера 6, выход которого соединен с вторым входом элемента 8 ИСКЛЮЧАЮЩЕЕ ИЖ-НЕ, выход которого подключен к входу установки в О счетчика 5, а выход счетчика 5 - к первому входу второго логического блока 10, вьпсод которого соединен с D-входом второго Dтриггера 7, выход которого подключен к вторым входам первого и второго логических блоков 9 и 10, третий вход первого логического блока 9 подключен к входу 2 устройства, а выход - к входу запрета счета реверсивного счетчика 1 и третьему входу второго логического блока 10. Счетчик 5,D-триггеры 6 и-7, элемент 8 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, блоки 9 и 10 образуют блок 11 автоматического уменьшения уровня постоянной составляющей в вькодном ИКМ сигнале. Устройство работает .следующим образом.

Входной сигнал в виде ДМ последовательности поступает на вход управления реверсивного счетчика 1, который является и входом 2 устройства, Реверсивный счетчик 1 может быть любым реверсивным счетчикЬм, который имеет вход управления направлением- счета, вход управления запрета счета и вход синхронизации, на который с шины 3 синхронизации поступают синхроимпульсы, выходной ИКМ код снимают с выходов реверсивного счетчика 1, которые являются выходом 4 устройства.

Вход управления запрета счета ре версивного счетчика 1 подключен к вы- . ходу блока 11 автоматического уменьшения уровня постоянной составляющей в выходном ИКМ сигнале. .Работа блока 11 основана на определении того, . изменяется ли знак (старший разряд реверсивного счетчика 1) выходного ИКМ сигнала в режиме молчания за период Т /(,, где ц - наименьшая ча стота передаваемого сигнала. Период Т определяется коэффициентом пересчета сче.тчика 5, который делит частоту синхроимпульсов. Счетчик 5 может быть счетчиком любого типа требуемой разрядности с выходом дешифрации состояния заполнения и входом установки в О. I

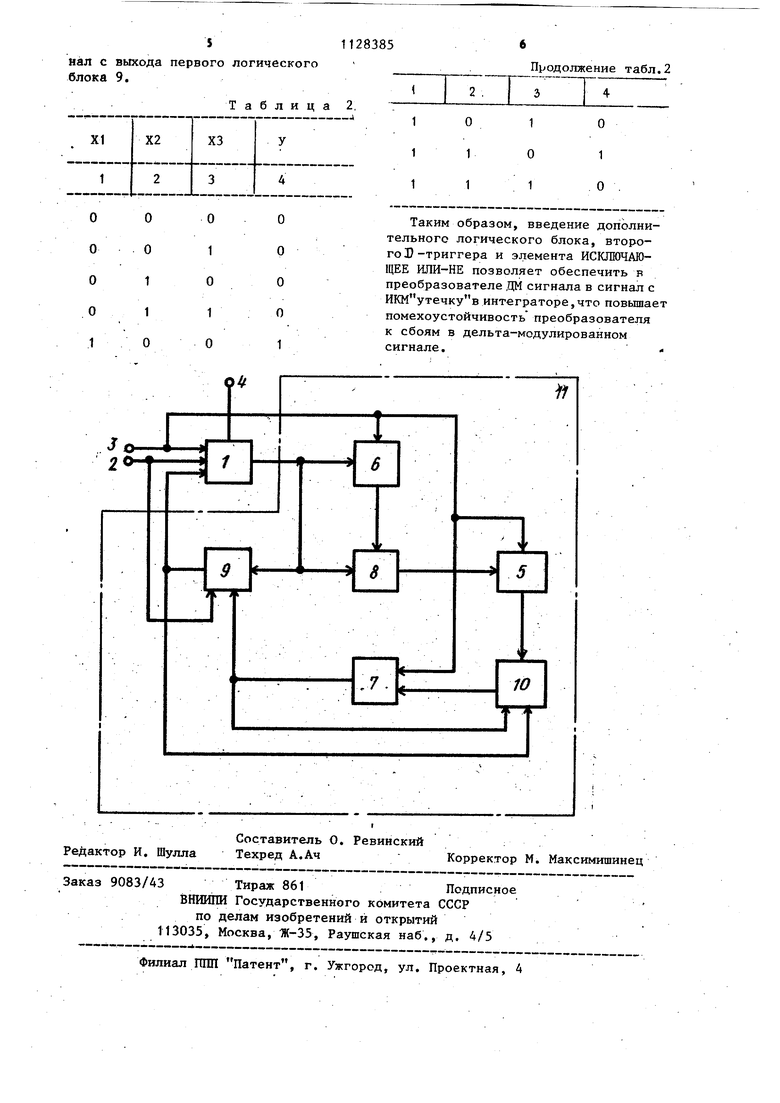

В зависимости от.знака ИКМ сигнала на конец периода Т и от уровня входного ДМ сигнала блоком 11 автоматического уменьшения уровня постоянной составляющей вырабатьшается дополнительный сигнал, управляющий работой реверсивного счетчика 1. такой, что в случае, если старший разряд реверсивного счетчика не изменяет своего значения за период Т, состояние реверсивного счетчика 1 изменяется на единицу младшего разряда в сторону уменьшения постоянной составляющей. Фиксация ИКМ сигнала в двух соседних тактах синхронизации , осуществляется первымБ-триггером 6, фиксация сигнала с выхода счетчика 5, означающего, что прошел период Т, осуществляется вторымD-триггером 7. Оба D-триггера являются синхронными D-триггерами, на входы синхрониза.ции которых подаются синхроимпульсы с шины 3 синхронизации. Если за пери од Т происходит изменение знака ИКМ сигнала, то элементом 8 ИСКЛЮЧАМЦЕЕ ,ИЛИ--НБ вырабатывается сигнал, сбрасывающий в 0. счетчик 5, В этом случае не происходит фиксации вторым D триггером 7 сигнала, сообщающего об истечении периода Т. Сигнал, дополнительно управляющий работой реверсивного счетчика 1 по входу запрета счета, вырабатывается первым логическим блоком 9. Это комбинационное устройство, которое в зависимости от выбранной элементной базы может реализовываться на тех или иныу логических элементах в соответствии с таблицей истинности его работы (табл. 1), где У - выходной сигнал первого логического блока 9, причем нулем закодирован сигнал Счет разрешен, а единицей - Запрет счета XI - сигнал на выходе старшего разряда реверсивного счетчика 1; Х2 сигнал на выходе второго)-тригге- ра 7; ХЗ - входной ДМ сигнал,

Т а б л и ц а 1

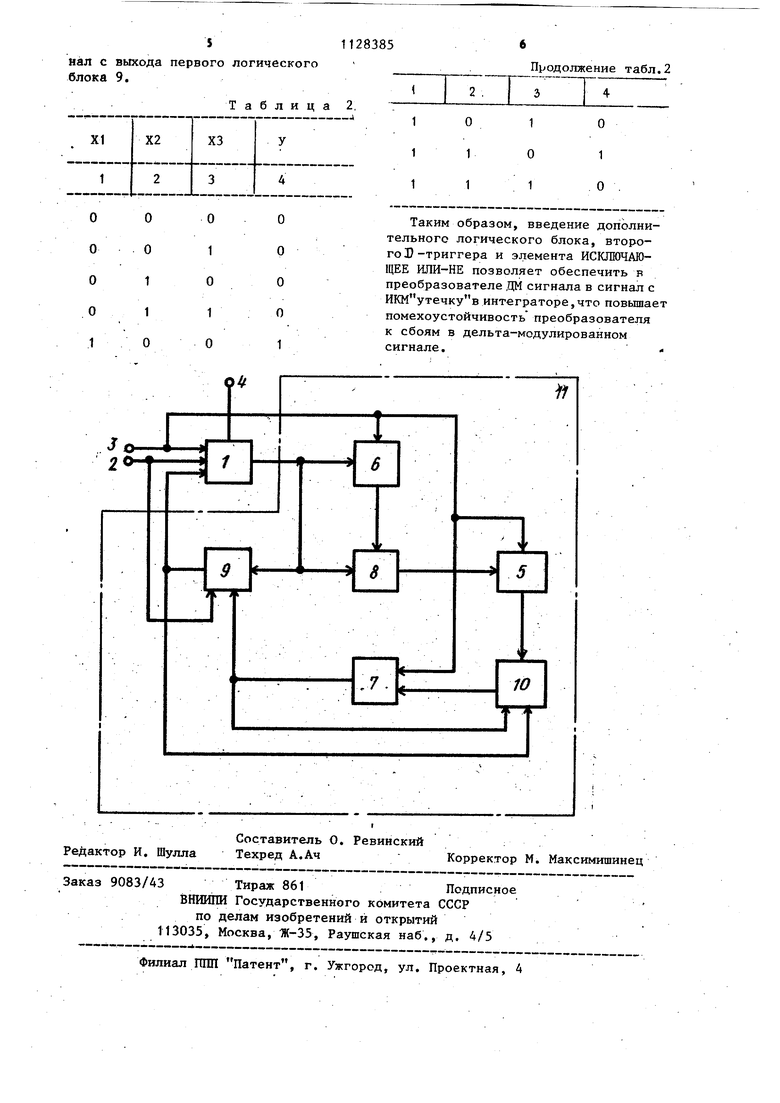

Второй логический блок 10 необходим для записи во второй)-триггер 7 сигнала с выхода счетчика 5 и установки этого триггера в первоначальное состояние после того, как реализуется функция по дополнительному управлению реверсивным счетчиком 1, Второй югический блок 10 также является комбинационной схемой, реализация котооой может быть осуществлена на основе таблицы истинности(табл.2), где У - вьтходной сигнал второго логического блока 10; XI - сигнал с выхода счетчика 5; Х2 - сигнал с выхода второго)-триггера 7; ХЗ - сигиал с выхода первого логического блока 9.

Таблица 2,

О О 1 1 О

О 1 О 1 О

О О

о о 1

продолжение табл.2

о 1 1

1

О 1 О

О 1

Таким образом, введение дополнительного логического блока, второго) -триггера и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ позволяет обеспечить в преобразователе ,ЦМ сигнала в сигнал с ИКМ утечку в интеграторе,что повышает помехоустойчивость преобразователя к сбоям в дельта-модулированном сигнале.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией | 1984 |

|

SU1216831A1 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1988 |

|

SU1533006A1 |

| Устройство преобразования сигналов с дельта-сигма модуляцией в сигналы с импульсно-кодовой модуляцией | 1985 |

|

SU1279073A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Устройство для приема и передачи дельта-модулированного сигнала | 1980 |

|

SU866735A1 |

ПРЕОБРАЗОВАТЕЛЬ ДЕЛЬТАМОДУЛИРОВАННОГО СИГНАЛА В СИГНАЛ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ, содержащий реверсивный счетчик, первый Б-триггер,Р-вход которого соединен с выходом старшего разряда реверсивного счетчика, a вход синхронизациис шиной синхронизации, счетчик и первый логический блок, о т л и ч a ю щ и и с я тем, что, с целью повы-v шения помехоустойчивости, s него введены второй логический блок, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и второйD-триггер, вход синхронизации которого соединен с шиной синхронизации, входом синхронизации реверсивного счетчика и входом счетчика, выход кбторого соединен с первьщ входом второго логического блока,,a вход установки в О счетчика - с выходом элемента ИСКЛЮЧАЮЩЕЕ ЙЛИ-НЕ, первый вход которого соединен с выходом первогоD-триггера, a второй вход подключен кD-входу первогоD-триггера и первому входу первого логического блока, второй вход которого соединен с вторым входом второго ло(Л гического блока и выходом второго D-триггера, третий вход первого логического блока соединен с входом устройства и входом управлейия ревер§ сивного счетчика, a выход - с входом запрета счета реверсивного счетчика и третьим входом второго лоЮ гического блока, выход которого сое00 динен с D-входом второго D-триггера, со сх ел

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| IEEE | |||

| Transactions on SolidState Circuits | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Устройство дельта-модуляции с цифровой адаптацией | 1980 |

|

SU930664A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-12-07—Публикация

1983-05-06—Подача