1

Изобретение относится к радиотехнике и может использоваться для синтеза частот и формирования сигналов, в частности, с частотной и фазовой модуляцией в различных par диотехнических устройствах техники связи и измерительной техники.

Целью изобретения является снижение уровня побочных составляющих в спектре выходного сигнала.

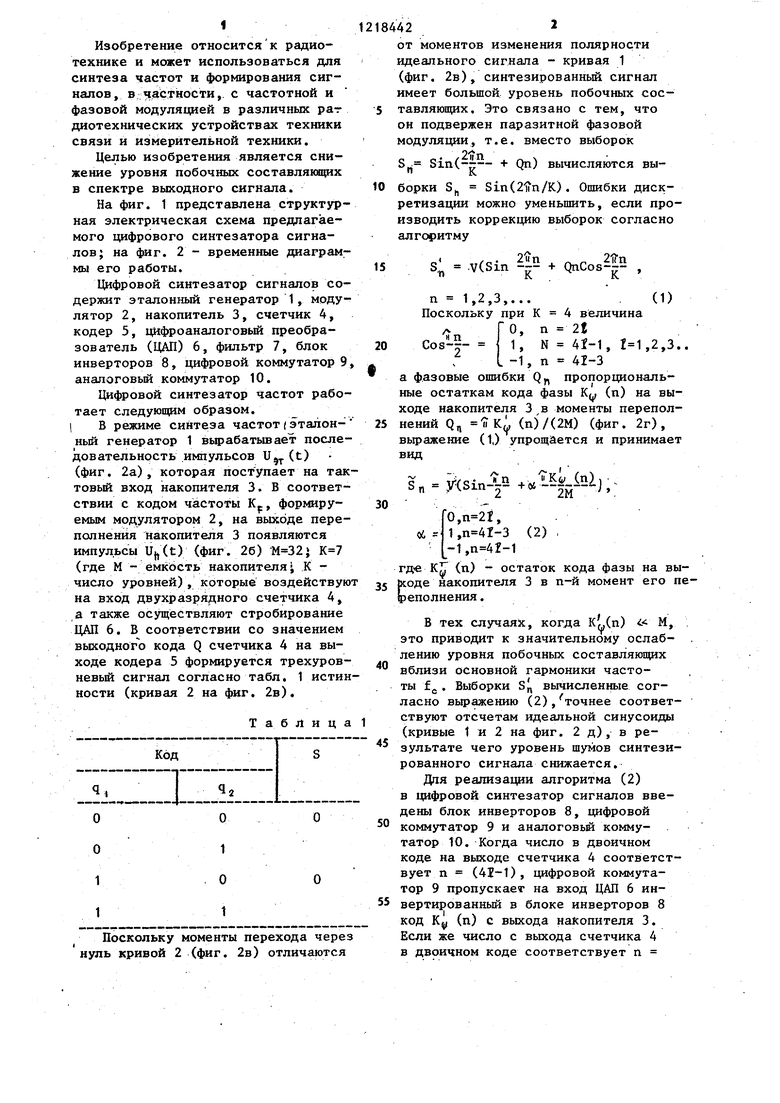

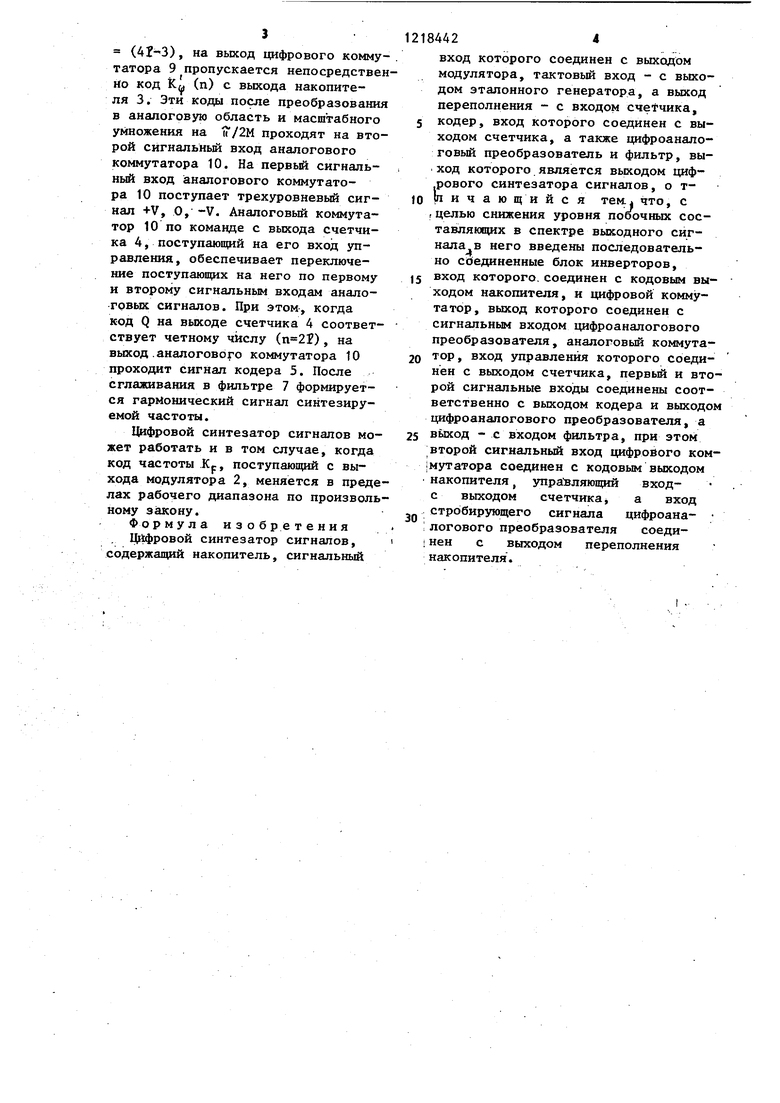

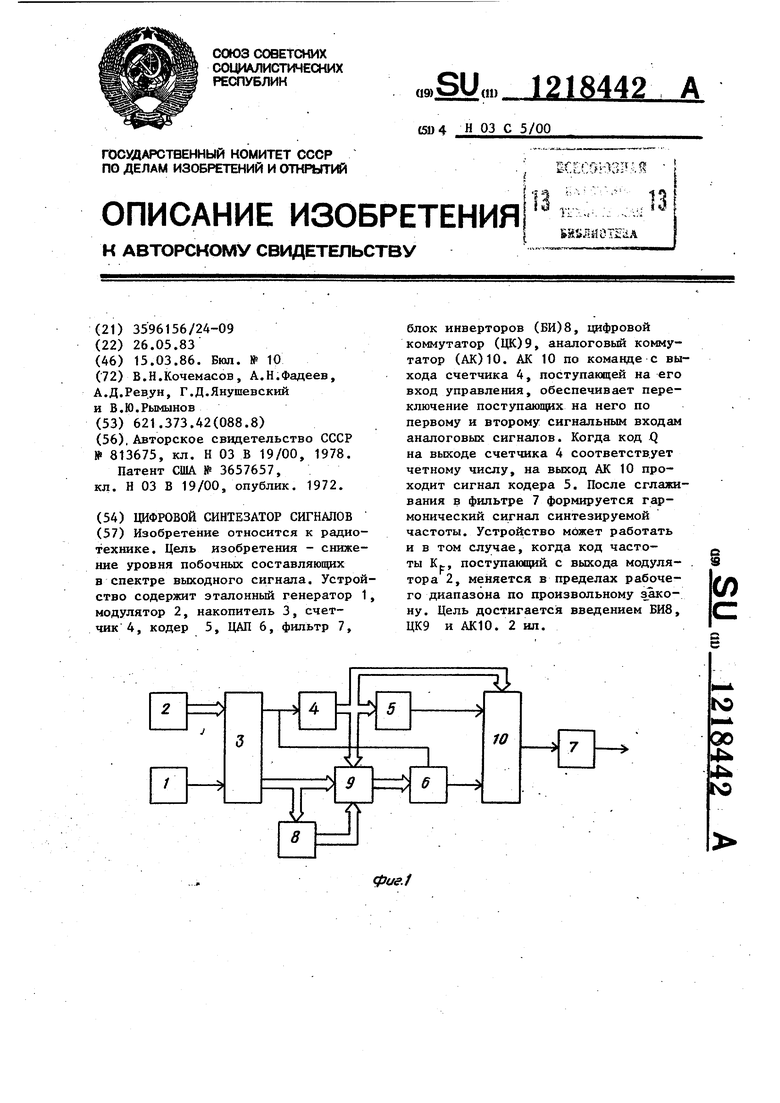

На фиг. 1 представлена структурная электрическая схема предлагаемого цифрового синтезатора сигналов; на фиг. 2 - временные диаграммы его работы.

Цифровой синтезатор сигналов содержит эталонный генератор 1, модулятор 2, накопитель 3, счетчик 4, кодер 5, цифроаналоговый преобразователь (ЦАП) 6, фильтр 7, блок инверторов 8, цифровой коммутатор 9 аналоговый коммутатор 10.

Цифровой синтезатор частот работает следующим образом. 1 В режиме синтеза частот(эталон- вый генератор 1 вьфабатьшает последовательность импульсов и (t) (фиг. 2а), которая пост упает на тактовый вход накопителя 3. В соответствии с кодом частоты К-, формируемым модулятором 2, на выходе переполнения накопителя 3 появляются импульсы и,,(t) (фиг. 26) (где М - ёмкбсть накопителяj К - число уровней), которые воздействую на вход двухразрядного счетчика 4, а также осуществляют стробирование ЦАП 6. В соответствии со значением выходного кода Q счетчика 4 на выходе кодера 5 формируется трехуровневый сигнал согласно табл. 1 истинности (кривая 2 на фиг. 2в).

Таблица 1

Код

Поскольку моменты перехода через нуль кривой 2 (фиг. 2в) отличаются

2184422

от моментов изменения полярности идеального сигнала - кривая 1 (фиг. 2в), синтезированньй сигнал имеет большой уровень побочных сос- 5 тавляющих. Это связано с тем, что он подвержен паразитной фазовой модуляции, т.е. вместо выборок

5/ч

S Sin(- + Qn) вычисляются вы- К.

10 борки 8„ Sin(2)i n/K). Ошибки дискретизации можно уменьшить, если производить коррекцию выборок согласно алгоритму

15

.v(sin 1 Qncos fa ,

(1)

Р

Cos-2-

,2,3,... Поскольку при К 4 величина

0,п 2t

1,N 4Ы, ,2,3.. L -1, п 42-3

а фазовые ошибки Q,, пропорциональные остаткам кода фазы К (п) на выходе накопителя моменты переполнений Q, «K(j, (п)/(2М) (фиг. 2г), вьфажение (1,) упрощается и принимает вид

Sn .« 5|ji2ij,;

об

0,,

1, (2)

-1,

гд-е Кщ (п) - остаток кода фазы на вы- {ходе накопителя 3 в п-й момент его переполнения .

В тех случаях, когда к ,,(п) i- М, это приводит к значительному ослаб- . лению уровня побочных составляющих вблизи основной гармоники частоты

fg . Выборки Sf вычисленные сог5

0

5

ласно выражению (2) , точнее соответствуют отсчетам идеальной синусоиды (кривые 1 и 2 на фиг. 2 д), в результате чего уровень шумов синтезированного сигнала снижается.

Для реализации алгоритма (2) в цифровой синтезатор сигналов введены блок инверторов 8, цифровой коммутатор 9 и аналоговьй коммутатор 10. Когда число в двоичном коде на выходе счетчика 4 соответствует п (41-1), цифровой коммутатор 9 пропускает на вход ЦАП 6 инвертированный в блоке инверторов 8 код К (п) с выхода накопителя 3. Если же число с выхода счетчика 4 в двоичном коде соответствует п

(АГ- З), на вькод цифрового коммутатора 9 пропускается непосредственно код Кл, (п) с выхода накопителя 3. Эти коды после преобразования в аналоговую область и масштабного умножения на м /2М проходят на второй сигнальньй вход аналогового коммутатора 10. На первьй сигнальный вход ;аналогового коммутатора 10 поступает трехуровневый сигнал +V, О, -V. Аналоговый коммутатор 10 по команде с выхода счетчика 4, поступающий на его вход управления, обеспечивает переключение поступающих на него по первому и второму сигнальным входам аналоговых сигналов. При этом, когда код Q на выходе счетчика 4 соответствует четному числу (), на выход .аналогового коммутатора 10 проходит сигнал кодера 5. После сглаживания в фильтре 7 формируется гармонический сигнал синтезируемой частоты.

Цифровой синтезатор сигналов может работать и в том случае, когда код частоты Кр, поступающий с выхода модулятора 2, меняется в пределах рабочего диапазона по произвольному закону.

Формула изобретения Ц1 ровой синтезатор сигналов, содержащий накопитель, сигнальный

218442Л

вход которого соединен с выходом модулятора, тактовый вход - с выходом эталонного генератора, а выход переполнения - с входом счетчика, 5 кодер, вход которого соединен с выходом счетчика, а также цифроанало- говый преобразователь и фильтр, выход которого является выходом цифрового синтезатора сигналов, о т10 Ьичающийся тем. что, с ,целью снижения уровня побочных составляющих в спектре выходного сигнала в него введены последовательно соединенные блок инверторов,

15 вход которого, соединен с кодовым выходом нгисопителя, и цифровой коммутатор, выход которого соединен с сигнальным входом цифроаналогового преобразователя, аналоговый коммута20 управления которого соединен с выходом счетчика, первый и второй сигнальные входы соединены соответственно с выходом кодера и выходом цифроаналогового преобразователя, а

25 выход - с входом фильтра, при этом второй сигнальный вход цифрового ком- |мутатора соединен с кодовым выходом накопителя, упра вляющий вход- с выходом счетчика, а вход стробирующего сигнала цифроана- , логового преобразователя соеди- ней с выходом переполнения накопителя.

d 5

III 11IIII I I ill

T 5W

/5

I . I , I

3i7

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор сигналов | 1984 |

|

SU1224949A1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2580444C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Цифровой вычислительный синтезатор для адаптивных систем связи с ППРЧ | 2020 |

|

RU2757413C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

Изобретение относится к радиотехнике. Цель изобретения - снижение уровня побочных составляющих в спектре выходного сигнала. Устройство содержит эталонный генератор 1, модулятор 2, накопитель 3, счетчик 4, кодер 5, ЦАП 6, фильтр 7, блок инверторов (БИ)8, цифровой коммутатор (ЦК)9, аналоговый коммутатор (АК)10. АК 10 по команде с выхода счетчика 4, поступающей на его вход управления, обеспечивает переключение поступающих на него по первому и второму сигнальным входам аналоговых сигналов. Когда код Q на выходе счетчика 4 соответствует четному числу, на выход АК 10 проходит сигнал кодера 5. После сглаживания в фильтре 7 формируется гармонический сигнал синтезируемой частоты. Устройство может работать и в том слу;чае, когда код частоты К.., поступающий с выхода модулятора 2, меняется в пределах рабочего диапазона по произвольному закону. Цель достигается введением БИ8, ЦК9 и АК10. 2 ил. (Л

Редактор Т.Парфенова

Составитель Г.Захарченко .Техред А.Бабинец Корректор М.Максимишинец

Заказ 1137/59Тираж 818 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий . 113035 Москва, Ж-35, Раушская йаб., д. 4/5

Филиал ПШ1 Патент, г.Ужгород, ул.Проектная, 4

(t/5.2

| , Авторское свидетельство СССР № 813675, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3657657, кд | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

Авторы

Даты

1986-03-15—Публикация

1983-05-26—Подача