11

Изобретение относится к области радиотехгтики и может быть сипользо- вано для формирования сигналов и синтеза частот в радиолокагу онных и связных системах.

Цель изобретения - снижение уровня паразитных составляющих выходных сигналов.

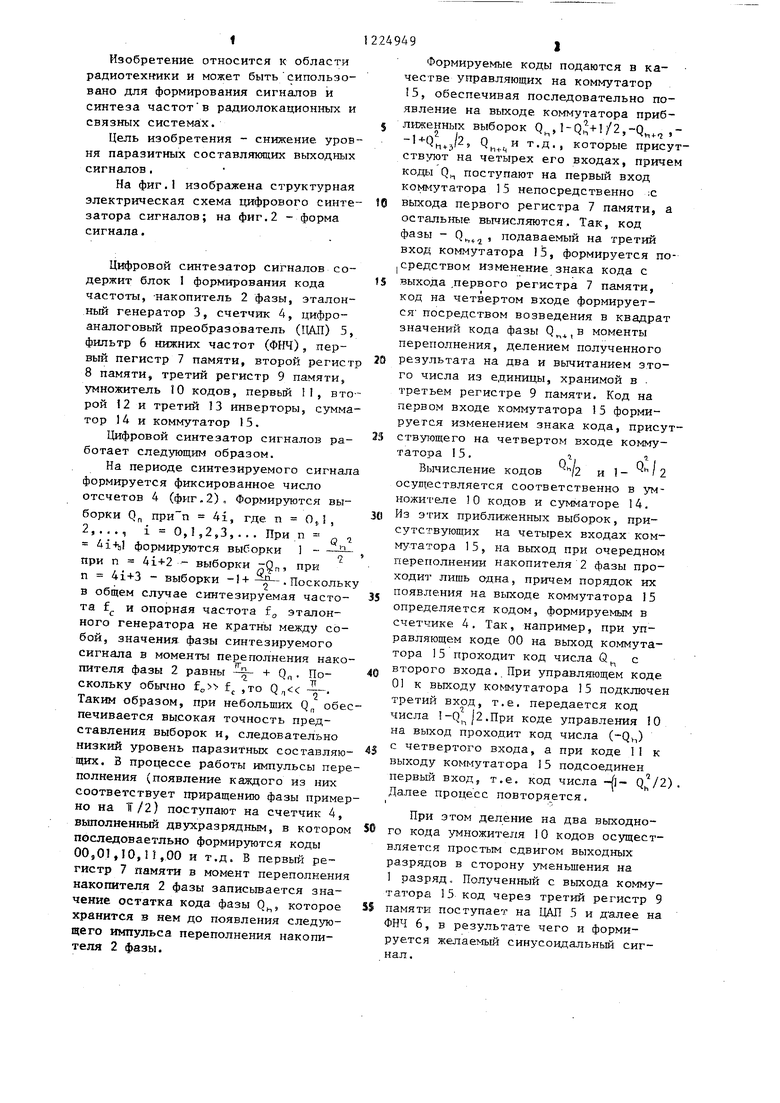

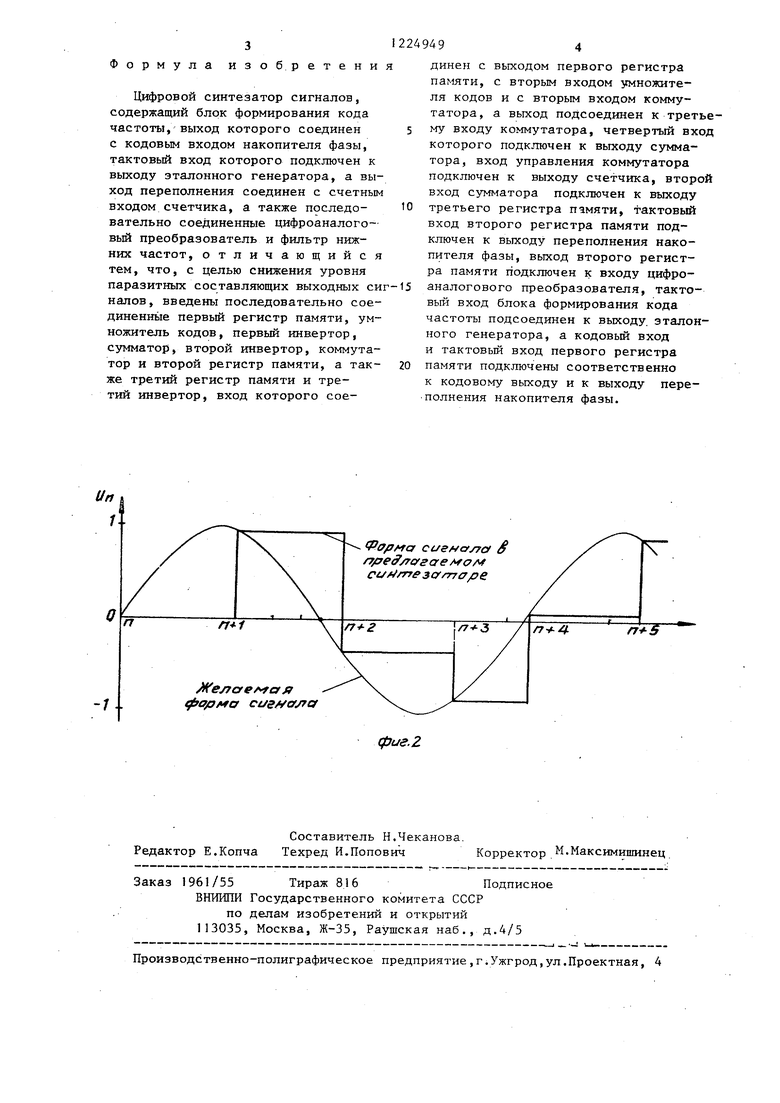

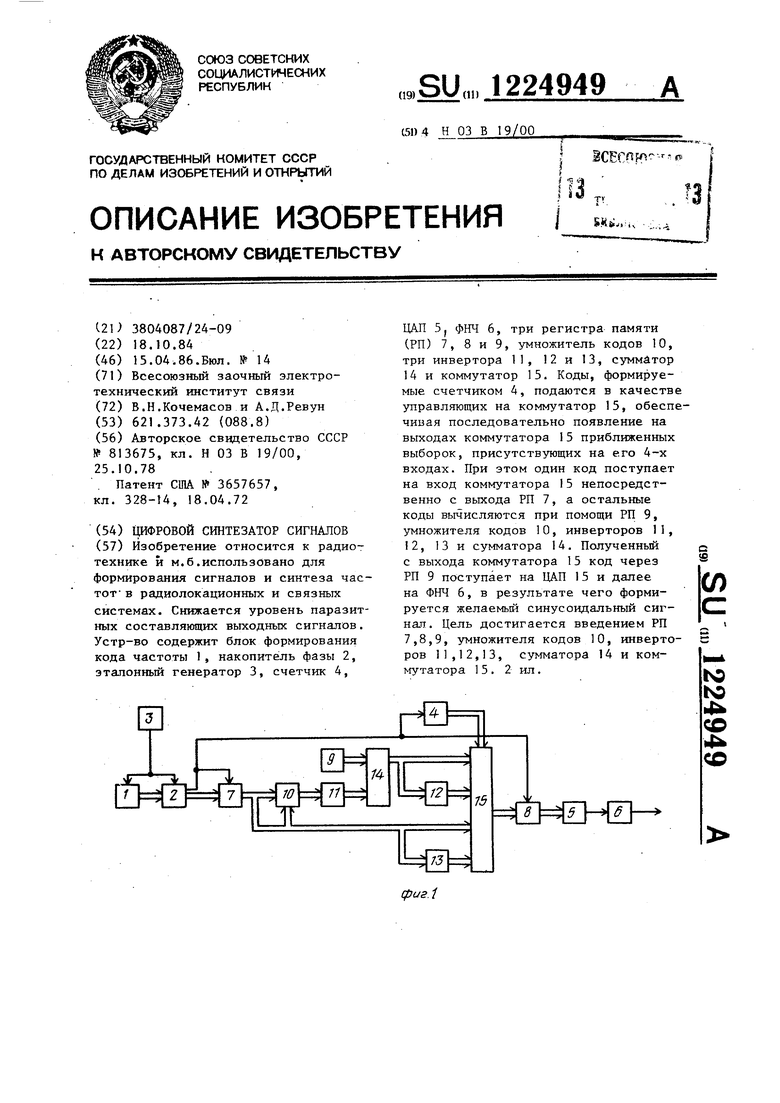

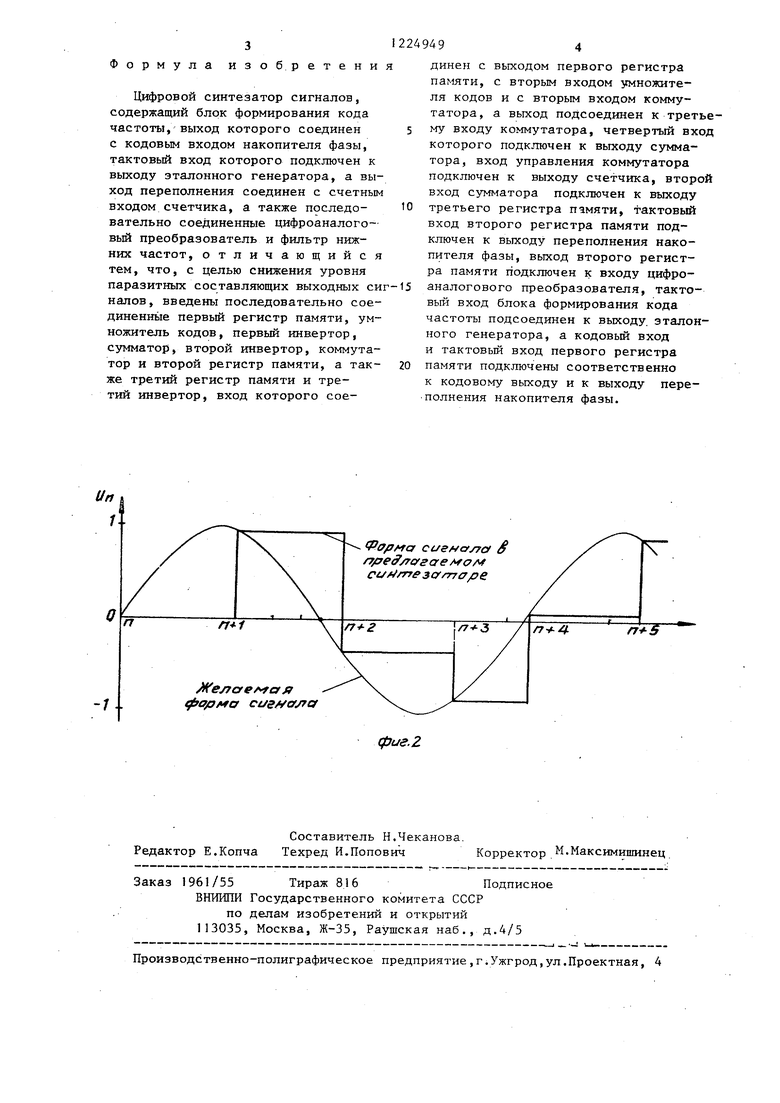

На фиг.1 изображена структурная электрическая схема цифрового синтезатора сигналов; на фиг,2 - форма сигнала.

Цифровой синтезатор сигналов содержит блок 1 формирования кода частоты, -накопитель 2 фазы, эталонный генератор 3, счетчик 4, цифро- аналоговый преобразователь (ПАП) 5, фильтр 6 нижних частот (ФНЧ), первый пегистр 7 памяти, второй регистр 8 памяти, третий регистр 9 памяти, умножитель 10 кодов, первьш П, второй 12 и третий 13 инверторы, сумматор 14 и коммутатор 15.

Цифровой синтезатор сигналов работает следующим образом.

На периоде синтезируемого сигнала формируется фиксированное число отсчетов 4 (фиг,2), Формируются выборки Qr, 4i, где п 0,1 , 2,.,., i 0,1,2,3,... При п 7 4i-h)l формируются выборки 1 - - при п - выборки rQn прк( п 41+3 - выборки .Поскольку в общем случае синтезируемая частота f и опорная частота f эталонного генератора не кратны между собой, значения фазы синтезируемого сигнала в моменты переполнения накопителя фазы 2 равны - + Q. Поскольку обычно fc, f ,то --. Таким образом, при небольших р„ обеспечивается высокая точность представления выборок и, следовательно низкий уровень паразитных составляющих. В процессе работы импульсы переполнения (появление каждого из них соответствует приращению фазы примерно на 1/2) поступают на счетчик 4, вьшолненный двухразрядным, в котором последоваетльно формируются коды 00,01,10,1,00 и т.д. В первый регистр 7 памяти в момент переполнения накопителя 2 фазы записьшается значение остатка кода фазы 0,, которое хранится в нем до появления следующего импульса переполнения накопителя 2 фазы.

49I

Формируемые коды подаются в качестве управляющих на коммутатор 5, обеспечивая последовательно появление на выходе коммутатора приближенных выборок QI, ,-Q ,- - -Qн -з/2 Qh+ т.д., которые присут- СТВ1ЛОТ на четырех его входах, причем кодь. Qi поступают на первый вход комь1утатора 15 непосредственно ;с

выхода первого регистра 7 памяти, а остгшьные вычисляются. Так, код фазы - Q,,J , подаваемый на третий вход коммутатора l5, формируется по- I средством изменение знака кода с

выхода .первого регистра 7 памяти, код на четвертом входе формируется посредством возведения в квадрат значений кода фазы Q,B моменты переполнения, делением полученного

результата на два и вычитанием зто- го числа из единицы, хранимой в . третьем регистре 9 памяти. Код на первом входе коммутатора 15 формируется изменением знака кода, присутствугощего на четвертом входе коммутатора 15.-г г

Вычисление кодов и 1 - 2 осуществляется соответственно в умножителе О кодов и сумматоре 14.

Из этих приближенных выборок, присутствующих на четырех входах коммутатора 15, на выход при очередном переполнении накопителя 2 фазы проходит лишь одна, причем порядок их появления на выходе коммутатора 15 определяется кодом, формируемым в счетчике 4. Так, например, при управляющем коде 00 на выход коммутатора 15 проходит код числа Q, с

второго входа. При управляющем коде 01 к выходу коммутатора 15 подключен третий вход, т.е, передается код числа .npH коде управления 10 на выход проходит код числа (-Q)

с четвертого входа, а при коде 1 к выходу коммутатора 15 подсоединен первый вход, т.е. код числа -/1- ) . Далее процесс повторя ется.

При этом деление на два выходно- го кода : ножителя 10 кодов осуществляется ПРОСТЬМ сдвигом ВЫХОДНЬ1Х

разрядов в сторону уменьшения на 1 разряд. Полученный с выхода коммутатора 15 код через третий регистр 9 памяти поступает на ЦАП 5 и далее на ФНЧ 6, в результате чего н формируется желаемый синусоидальньш сигнал.

31224949

ормула изобретения

ди па ля та 5 му ко то под вх

Цифровой синтезатор сигналов, содержащий блок формирования кода частоты, выход которого соединен с кодовые входом накопителя фазы, тактовый вход которого подключен к выходу эталонного генератора, а выход переполнения соединен с счетным входом счетчика, а также последовательно соединенные цифроаналого- вый преобразователь и фильтр нижних частот, отличающийся тем, что, с целью снижения уровня паразитных составляющих выходных си налов, введены последовательно сое- диненньш первый регистр памяти, умножитель кодов, первый инвертор, сумматор, второй инвертор, коммутатор и второй регистр памяти, а также третий регистр памяти и третий инвертор, вход которого соединен с выходом первого регистра памяти, с вторым входом умножителя кодов и с вторым входом коммутатора, а выход подсоединен к третье- 5 му входу коммутатора, четвертый вход которого подключен к выходу сумматора, вход управления коммутатора подключен к выходу счетчика, второй вход сумматора подключен к выходу

10 третьего регистра памяти, тактовый вход второго регистра памяти подключен к выходу переполнения накопителя фазы, выход второго регистра памяти подключен к входу цифро- 15 аналогового преобразователя, тактовый вход блока формирования кода частоты подсоединен к выходу, эталонного генератора, а кодовый вход и тактовый вход первого регистра

20 памяти подключены соответственно к кодовому выходу и к выходу переполнения накопителя фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385238A2 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство формирования кода фазы сигнала с линейной частотной модуляцией | 1984 |

|

SU1265986A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1517016A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1626314A1 |

Изобретение относится к радиотехнике и м.б.использовано для формирования сигналов и синтеза частот в радиолокационных и связных системах. Снижается уровень паразитных составляющих выходных сигналов. Устр-во содержит блок формирования кода частоты 1, накопитель фазы 2, эталонный генератор 3, счетчик 4, ЦАП 5| фНЧ 6, три регистра памяти (РП) 7, 8 и 9, умножитель кодов 10, три инвертора 11, 12 и 13, сумматор 14 и коммутатор 15. Коды, формируемые счетчиком 4, подаются в качестве управляющих на коммутатор 15, обеспечивая последовательно появление на выходах коммутатора I5 приближенных выборок, присутствующих на его 4-х входах. При этом один код поступает на вход коммутатора I5 непосредственно с выхода РП 7, а остальные коды вычисляются при помощи РП 9, умножителя кодов 1 О, инверторов 11, 12, 13 и сумматора 14. Полученный с выхода коммутатора 15 код через РП 9 поступает на ЦАП 15 и далее на ФНЧ 6, в результате чего формируется желаемый синусоидальный сигнал. Цель достигается введением РП 7,8,9, умножителя кодов 10, инверторов 11,12,13, сумматора 14 и коммутатора 15. 2 ил. (Л to N9 4 CD 4ib ;о

-/.

CLfe cf/7cf

Составитель Н.Чеканова. Редактор Е.Копча Техред И.Попович Корректор.-Максимишинец.

Заказ 1961/55 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгрод,ул.Проектная, 4

фиг. 2

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3657657, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1986-04-15—Публикация

1984-10-18—Подача