(21)4236261/24-24

(22)27.04.87

8. Бюл, № 45

Завод Термопластавтоьтат Хмель- нш;кого производственного объединения Прессмаш

(72) В,А, Федорчук; . Фитькал, В,В, Кзпссов и В,.Л. Павлов

(53)621,503,55(088.8)

(56)Авторс :ое свидетельство СССР № 1231488, кл, G 05 В 19/18, 1985

Авторское свидетельство СССР № 1208536, кл. G 05 В 19/18, J98/4.

(54)ПРОГРА ШИРУЕМЫЙ КОНТРОЛЛЕР,

(57)Изобретение относится к автоматическим дискретным управляющим системам, в частности, может быть использовано для управления литьевыми

машинами по переработке термопластич- ньпс материалов. Цель изобретения - упроа ение программируемого контроллера, повышение надежности и расширение его функциональных возможностей. Программируемый контроллер, содержащий генератор тактовых импульсов, счетчик, блок постоянной памяти, блок оперативной памяти, дешифратор кода операции, входной блок, выходной блок, дополнительно содержит

второй дещлфрато р, пять элементов И-ИЕ; один элемент 1Ш11, коммутатор каналов,, блок сравнения, регистр, триггер. Вся рабочая программа делится на. управляющие слова (УС),состоящие из условной и исполнительной частей, и выполняется только после выполнения условий условной части. Каж,дое УС начинается с микроинструг-сции Начало управлягощего слова (НУС) .Триггер переводится в активное состояние ка;кдый раз при чтении с блока по стоянной памяти микроинструкции НУС, а в пассивное состояние - при невыполнении хотя бы одного условия условной части УС. Если к моменту чтения с блока постоянной памяти микроинструкций исполнительной части триггер остается в активном состоянии, микроинструкции выполняются, в противном случае только читаются. УС могут быть увязаны в подпрограммы или отдельные программы с помощью промежуточных переменных, хранящихся в, блоке оперативной памяти. Данный принцип обработки информации позволяет упростить .программируемый контроллер. 5 ил.

(О

|ВК.

ц

ч

Изобрет м-1ие. относится к автоматическим дискретным управляющим системам и может быть использовано для управления промьшшенным оборудова- HpiBM к механизмами, в частности литьевыми мак1инами и манютуляторами..

Целью изобретения является упрощение контроллера, повьшгение надежности работы и расширение его функциональных возмолшостей за счет одновременного независимого управления произвольным числом объектов.

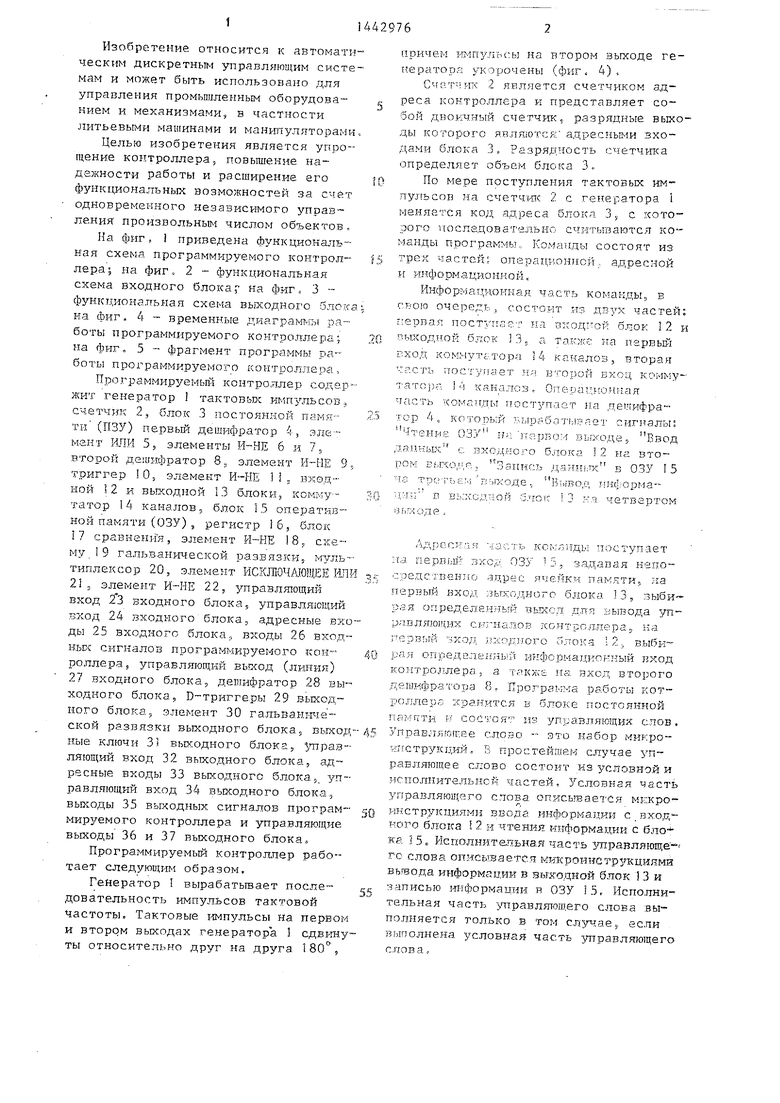

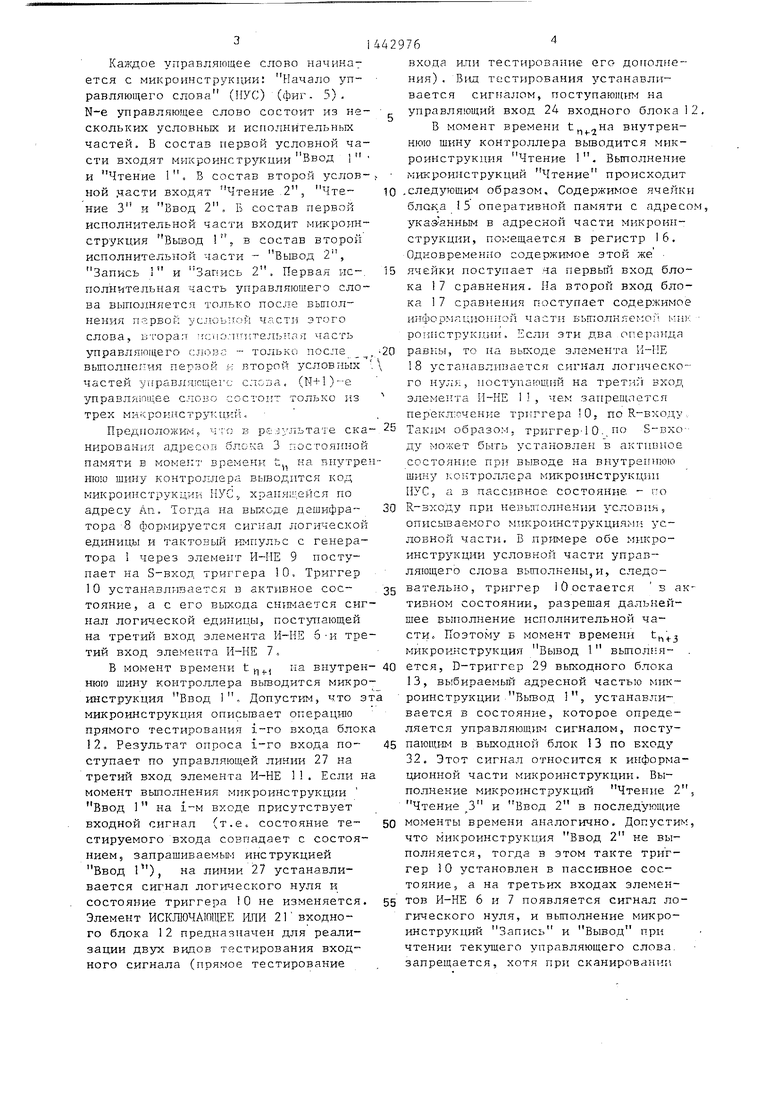

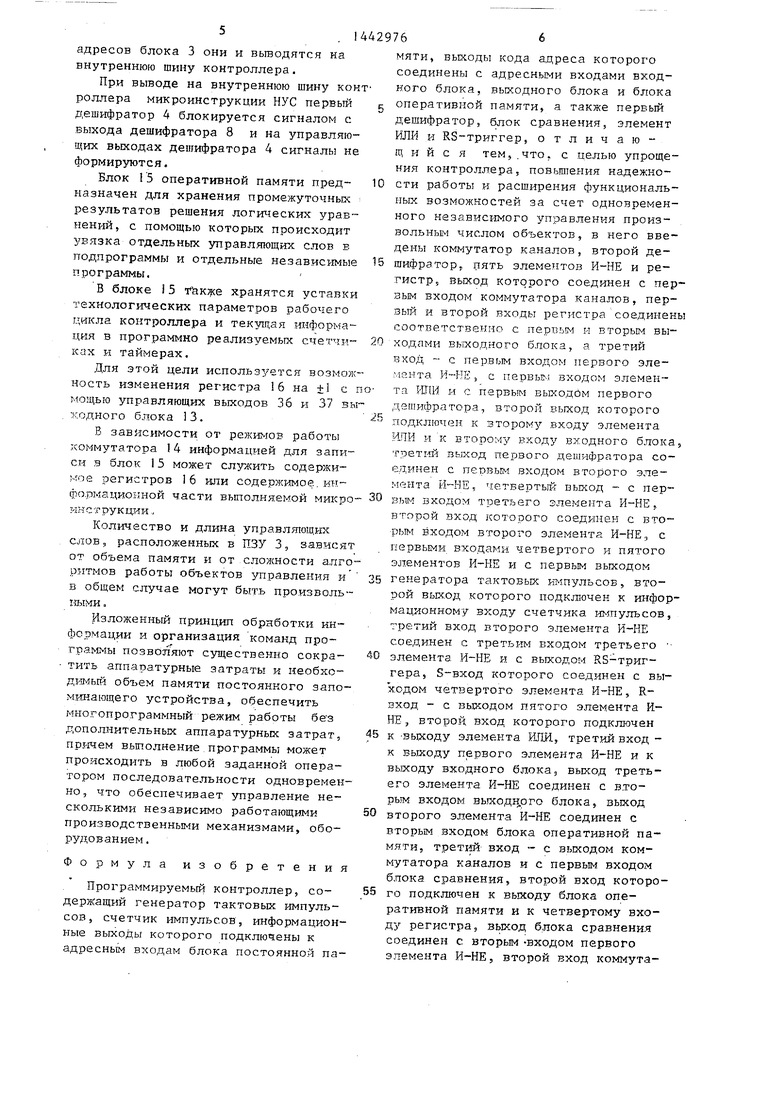

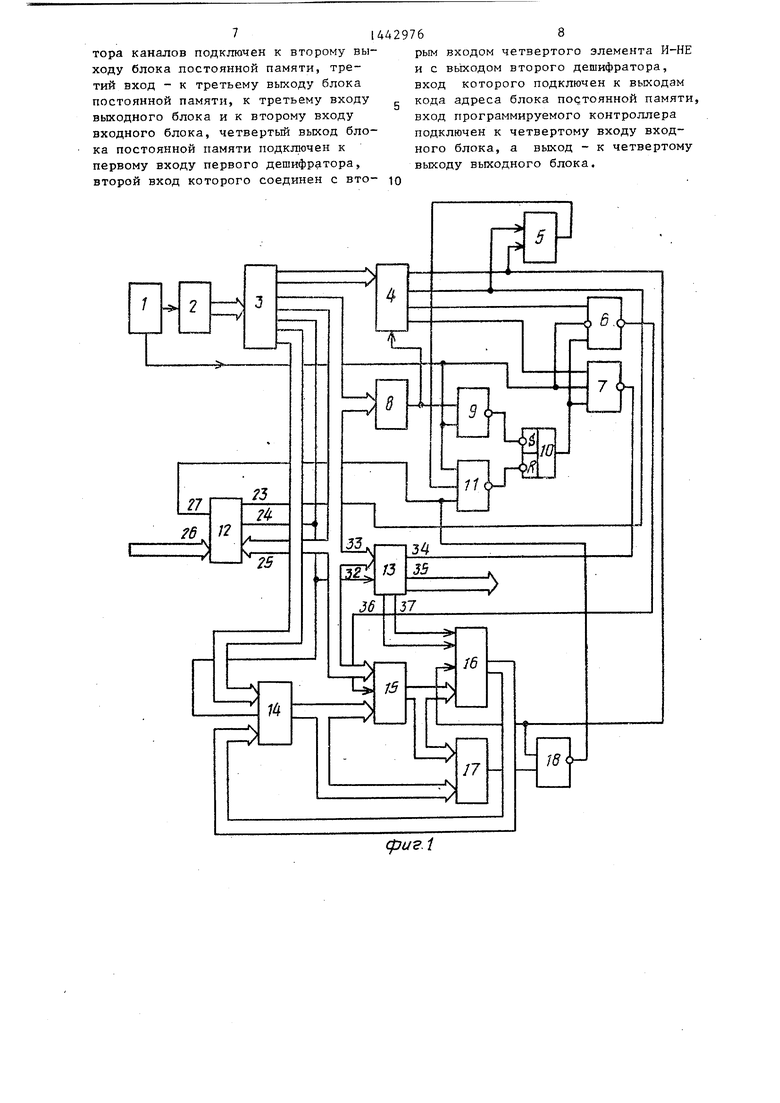

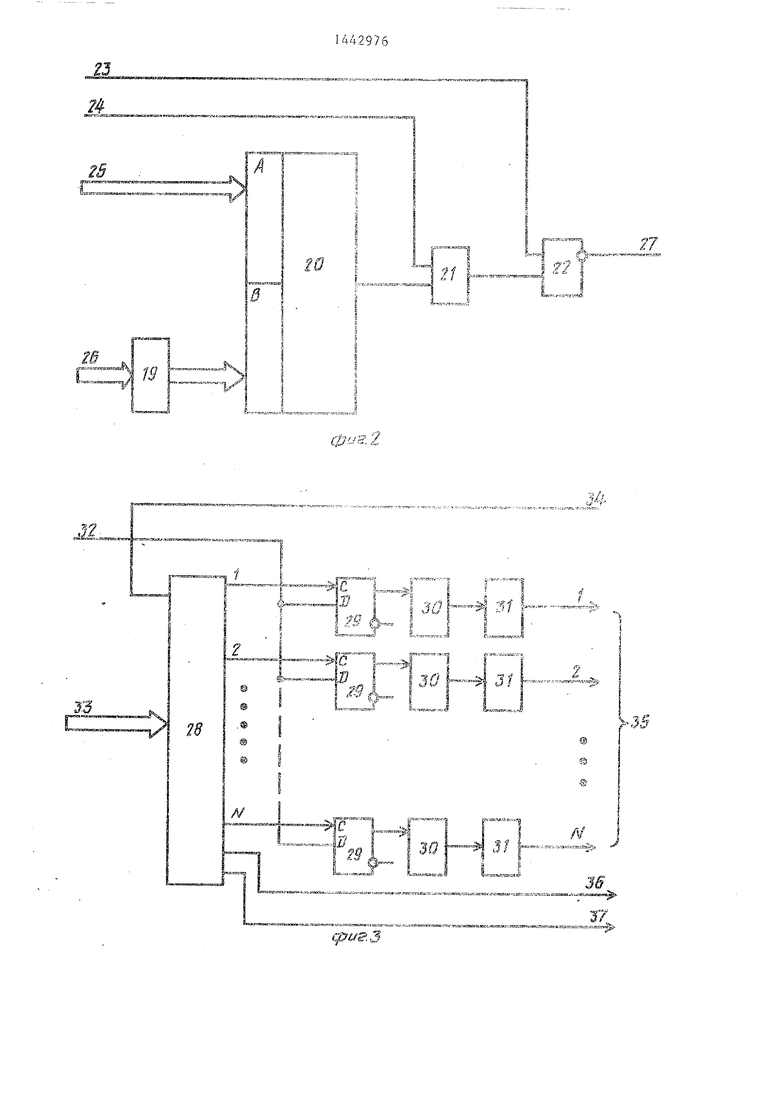

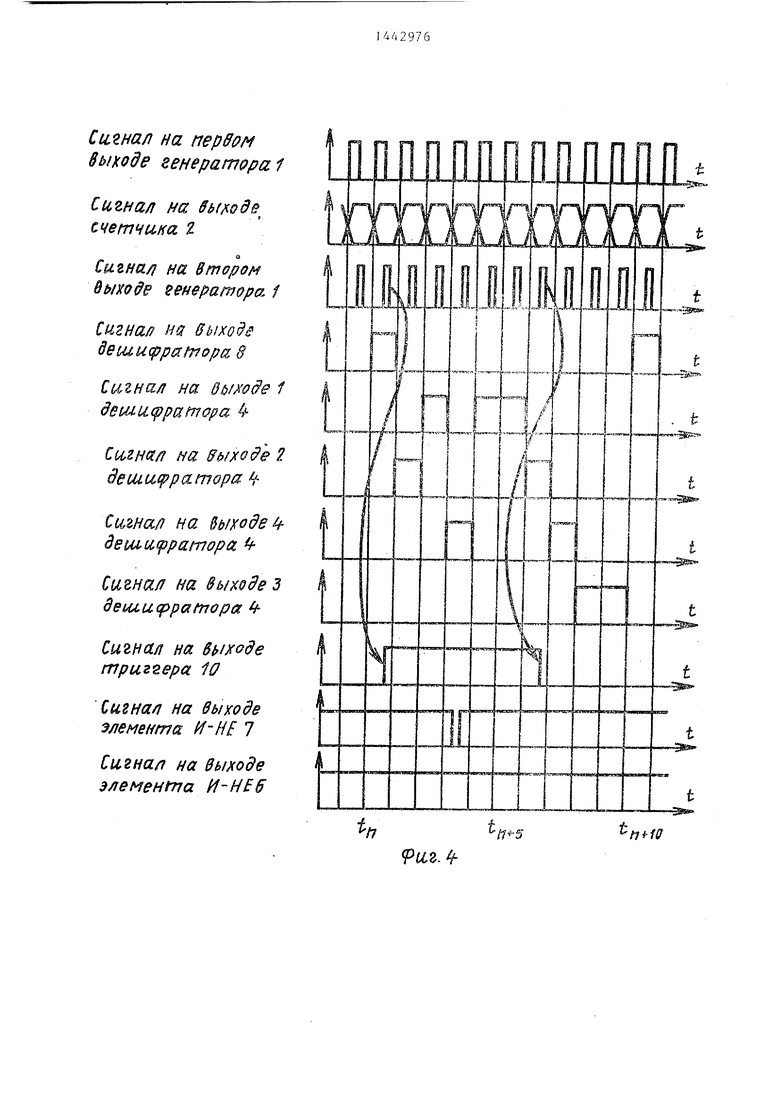

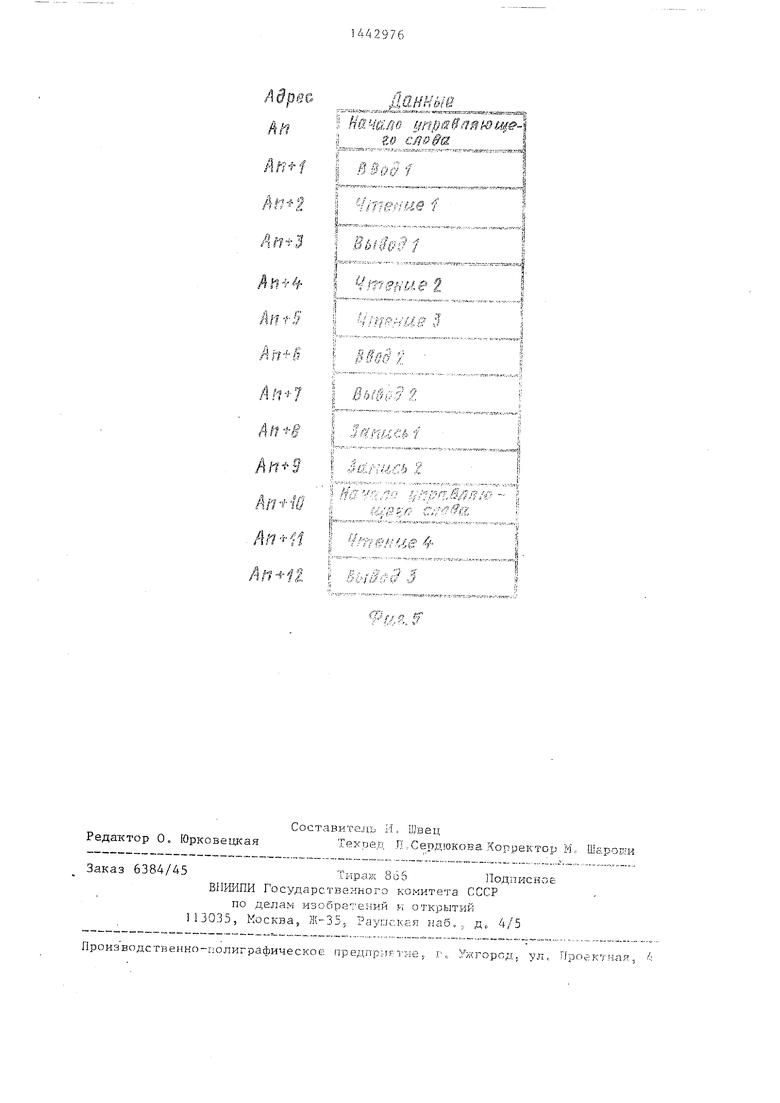

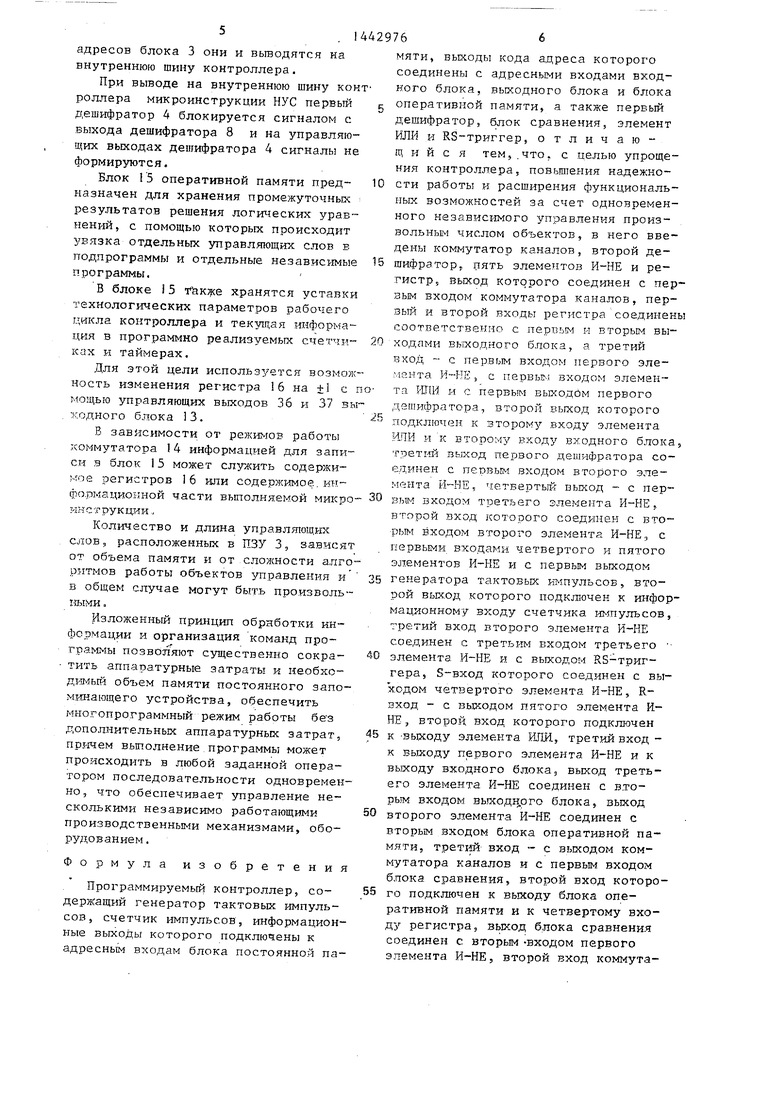

На фиг, 1 приведена функциональная схема программируемого контроллера; на фиг, 2 - функциональная схема входного блока на фиг 3 -- функциональная схема выходного блока на фиг. 4 - временные диаграмт-зы работы программируемого контроллера; на фиг. 5 - фрагмент программы работы программируемого контроллера.

Программируемый контроллер содержит генератор 1 тактовьк импульсов, счетчик 2, блок 3 постоянной памяти (ПЗУ) первьй дешифратор 4, элемент ИЛИ 5, элементы И--НЕ 6 и 1 ,j второй дешифратор Q,, элемент И-НЕ 9, триггер 10; элемент П. входной 12 и выходной 13 блоки, коммутатор 14 каналов, блок 15 оперативной памяти (ОЗУ) э регистр 16, блок 17 сравнени я, элемент Й-НЕ 18, схему 19 гальванической развязкИ; мультиплексор 20, элемент HCKJlOHAIOHifEE ИЛИ 21. элемент 22, управляющий вход 23 входного блока управляющий вход 24 входного блока, адресные входы 25 входного блока, входы 26 вход- ньк сигналов программируемого тсон- роллера, управляющий вькод (линия) 27 входного блока, дешифратор 28 выходного блока, П триггеры 29 выходного блока, элемент 30 гальвант-ме- ской развязки выходного блока, выходные ключи 3i выходного блока, управляющий вход 32 вьтходного блока, адресные входы 33 выходного блока., управляющий вход 34 выходного блока, вьпюды 35 выходных сигналов нрограм- мирз емого контроллера и управляющие выходы 36 и 37 выходного блока,

Программируемьм контрол,пер работает следуювл-м образом.

Генератор 1 вырабатьшает последовательность импульсов тактовой частоты. Тактовые 1дапульсы на первом и втором выходах генератора сдвинуты относительно друг на друга 180 ,

0

0

-:

.

Причем импз ЛЬ .:ы на втором выходе ге- f-шраторз укорочены (фиг. 4),

Счр-тчик 2 является счетчиком адреса контроллера и представляет собой двоичный счетчик,, разрядные выходы которого ЯВЛЯЮТСЯ адресньйчи входами блока 3, Разрядность счетчика определяет объем блока 3,

По мере поступления тактовых им- nyjtbcoB на счетчшс 2 с генератора 1 меняется код адреса блокл 3, с кото- эого последовательно с п-гтываются команды программы,. Команды состоят из трех частей; операционной, адресной ,и информационной,

Информат.тионная часть команды., в свою очередь, состоит ,из двух частей: -ерпа,г; поступает на вхоцт ой блок 12 и яьжодпой блок IS; а так;ке па первьй рход 14 каналов, вторая частъ пос гуиает на второй вход комму- тата); 1ч каналов, Операциопкая часть тсомапды постз паст на дечгифра- тор 4, кс торкй ,:1ТГ;1эае1 сигналы Чтепив ОЗУ пярпом выходе, Ввод данных с, вкодиого блока 1 2 на втором Еыходр, Запись даггтпж в ОЗУ 15 ча Tpf.ri bei i 1 - Ходе, Вь/БОл пнс/орма- ,г-1К л вь;хсд : ой йпо К . D кя четвертом :3,/ходе .

Адресная часть кокяиды поступ,зет ла первьш: вход ОЗУ З, за,цавая непо- редственпо адрес ячейки памяти, яа первый вход ;зыходного блока 13, зыби-рая определенный -выход д,пя вывода уп- уанляюнгих ,1лов контроллера. ка г ерзг гй зход входного 2,, выби ;;ая определенный ннформацкокный вход контроллера, а также на вход второго депшфратора 8, Программа работы кот- хзоллерд хранится в блоке постоянной ггймггти I- состоят из управляющих слов. Управлягоп-ее слово - это набор мир:рО инструкций, В простейшем случае управляющее слово состоит из условной и исполнительной частей. Условная часть управляющего слова описывается микроинструкциями ввода ннфор-мацк -; с, ного блока I 2 и чтения Г пгформации с бло- КВ. 15, ИсполнитеХ Ьная часть з равляюще - го слова описывается кикроинструкциями вывода информации в выходной блок 13 и записью информации в ОЗУ 15, Иенолни- те,льная часть Т равлят.эщего слова выполняется только в том случаеJ если выполнена условная часть управляющего с,пова..

Калодое управляющее слово начинается с микроинструкции: Начало управляющего слова (ПУС) (фиг. 5). N-e управляющее слово состоит из нескольких условных и исполнительных частей. В состав первой условной части входят микроинструкции Ввод 1 и Чтение 1. В состав второй условной .части входят Чтение ,2, Чтение 3 и Ввод 2, Б состав первой исполнительной части входит микроинструкция Вьпзод 1. в состав BTOpoii исполнительной части Вывод 2, Запись Г и Запись 2. Первая ис-. полнительная часть управляющего слова выполняется только после выполнения парной услоьпой части этого слова, 1ггора;т ис11олтп;тельпля часть управляю1цего слова - только после выполнения первой и второй условных частей управля сщегс слеза. (N+l)--e управля1Г)1цее слово только из трех ми Хрор.нструта1ий.,

Предположим, что в ра .-Г; Л7 тате сканирования адресов блока 3 постоянной памяти в момент времени t на внутрен нюш шину контроллера вьшо/дится код микроинструкцик НУС, хранящейся по адресу Аи. Тогда на выходе дешифратора -8 формируется сигнал логической единицы и тактовый иг тульс с генератора I через элемент И-НЕ 9 поступает на S-вход триггера 10, Триггер 10 устанавливается в активное состояние, а с его выхода снимается сигнал логической единицы, поступающей на третий вход элемента И-НЕ 6-и третий вход элемента И-НЕ 7,,

В момент времени tj, на внутреннюю шину контроллера вьшодится микроинструкция Ввод, 1. Допустим, что эт микроинструкция описывает операцию прямого тестирования входа блока 12. Результат опроса i-ro входа поступает по управляющей линии 27 на третий вход элемента И-НЕ 11. Если на момент вьшолнения микроинструкции Ввод 1 на L-M входе присутствует входной сигнал (т.е. состояние тестируемого входа совпадает с состоянием, запращиваемьи инструкцией Ввод ), на линии 27 устанавливается сигнал логического нуля и состояние триггера 10 не изменяется. Элемент ИСКЛЮЧАЮЩЕЕ ВДИ 2Г входного блока 12 предназначен для реализации двух видов тестирования входного сигнала (прямое тестирование

976

входа или тестирование его дог1ОЛР1е- ния). Вид тестирования устанавливается сигналом, поступаюиигм на управляющий вход 24 входного блока 12,

В момент времени внутреннюю шину контроллера выводится микроинструкция Чтение 1. Выполнение

микроинструкций Чтение происходит

.следующим образом. Содержимое ячейки 15 оперативной памяти с адресом, укаэ анным в адресной части микроинструкции, помещается в регистр 16, Одновременно содержимое этой же

ячейки поступает на первьш вход блока 17 сравнения. На второй вход блока 17 сравнения поступает содержимое ипформлционной части вьгполнпег-:ом ми)-; роипструкц11п, Если эти два операнда равны, то на вьгходе элемента И-НЕ

устанавливается сигнал логического нуля, постуиз ощий на TpeTiifr вход

элемента И-НЕ 11, чем запрещается перекл;очение трмггера Ю, по R-входу .

TaKiLM образом, триггер-10. по S-BXO- ду может быть установлен в актппное состояние при выводе на внутрепттюю шину -.оь:троллсра мшсроинструкцггл ПУС, а в пассивное состояние. - по

R-входу при невьшолнении условия, описываемого мпкроинструкциядми условной части, В примере обе микроинструкции условной части управляющего слова выполнены,и, следовательно, триггер 1 О остается в активном состоянии, разрешая дальнейшее рьтолнение исполнительной части. Поэтому Б момент времени

МИКрОРПтСТруКЦИЯ Вывод 1 ВЫПОЛ Яется, D-триггер 29 выходного блока 13, выбираемьп адресной частью мпк - роинструкции Вьгоод 1, устанавливается в состояние, которое определяется управляюш.гм сигналом, поступающим в выходной блок 13 по входу 32. Этот сигнал относится к информационной части микроинструкции. Выполнение микроинструкции Чтение 2, Чтение 3 и Ввод 2 в последующие

моменты времени аналогично. Допустим, что микроинстрз кция Ввод 2 не выполняется, тогда в этом такте триггер 10 установлен в пассивное состояние, а на третьих входах элементов И-НЕ 6 и 7 появляется сигнал логического нуля, и вьшолнение микро- инструкщ-ш Запись и Вывод при чтении текущего управляющего слова, запрещается, хотя при сканирован ;; ,

51

адресов блока 3 они и вьшодятся на внутреннюю шину контроллера.

При выводе на внутреннюю шину кок роллера микроинструкции НУС первый дешифратор 4 блокируется сигналом с выхода дешифратора 8 и на управляющих выходах дешифратора 4 сигналы не формируются.

Блок I5 оперативной памяти предназначен для хранения промежуточных результатов решения логических урав- неН1-щ, с помощью которых происходит увязка отдельных управляющих слов в

мяти, выходы кода адреса которого соединены с адресными входами входного блока, выходного блока и блока

оперативной памяти, а также первый дешифратор, блок сравнения, элемент ИЛИ и КЗ-триггер, отличающийся тем,.что. с целью упрощения контроллера, повьштения надежносги работь и расширения функциональных возможностей за счет одновременного независимого управления произ- вольньЕм числом объектов, в него введены комм7утатор каналов, второй де

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарно-резервированная управляющая система | 1984 |

|

SU1221658A1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Программируемый контроллер | 1983 |

|

SU1238032A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

подпрограммы и отдельные независимые 15 шифратор, пять элементов И-НЕ и репрограммы.

В блоке i 5 хранятся уставки технологических параметров рабочего цикла контроллера и текугцая информация в программно реализуемых счетчиках и таймерах.

Для этой дели используется возможность изменения регистра 16 на +1 с помощью управляющих выходов 36 и 37 выходного блока 13.

В зависимости от режимов работы коммутатора 14 информацией для записи э блок 15 может служить содержи- тое регистров 16 или содержимое.. ин сро.рг.тационной части выполняемой микро 1НС ГруКЦ.ИИ.,

Количество и длина управляющих слов 5 расположенных в ПЗУ 3, зависят от объема памяти и от сложности алгоритмов работы объектов управления и в общем случае могут быть произволь1Ш1МИ .

Изложенный принцип обрнботки информации и организация команд про

позволяют существенно сократить аппаратурные затраты и необхо- Д1-мьй объем памяти постоянного запоминающего устройства, обеспечить многопрограммный режим работы бе з дополнительных аппаратурных затрат, примем выполнение.программы может происходить в любой заданной оператором последовательности одновременно, что обеспечивает управление несколькими независимо работающими производственными механизмами, оборудованием.

Формула изобретения

Программируемый контроллер, содержащий генератор тактовых импульсов, счетчик импульсов, информационные выходы которого подключены к адресным входам блока постоянной па

гистр, вьосод которого соединен с первым входом коммутатора каналов, первый и второй входы регистра соединены соответственно с первьм и вторым выходами выходного блока, а третий вход - с nepBFjiM входом первого элемента , с первьЕ-л входом элемента ИПИ и с первым выходом первого дешифратора, второй выход которого подключен к второму входу элемента ИЛИ и к второму входу входного блока, TpeTi-rfi выход первого дешифратора соединен с первым входом второго элемента И--НЕ, четвертый выход с пер- Bbtt-5 входом третьего элемента И-НЕ. второй вход которого соединен с вто- р)1м входом второго элемента И-НЕ, с первыми входами четвертого и пятого элементов И-НЕ и с первым выходом

генератора тактовых импульсов, второй выход которого подктаочен к информационному входу счетчика ш-шульсов, третий вход второго элемента И-НЕ соединен с треты м входом третьего элемента И-НЕ и с выходом RS-триг- гера, S-вход которого соединен с выходом четвертого элемента И-НЕ, R- вход - с выводом пятого элемента И- НЕ, второй вход которого подключен

к -выходу элемента ИДИ, третий вход - к первого элемента И-НЕ и к выходу входного блока, выход третьего элемента И-НЕ соединен с в-то- рьм входом выходз ого блока, выход второго элемента И-НЕ соединен с BTOpbiM входом блока оперативной памяти, трет1€й вход - с выходом коммутатора каналов и с первым входом блока сравнения, второй вход которого подключен к выходу блока оперативной памяти и к четвертому входу регистра, вькод блока сравнения соединен с вторьм -входом первого элемента И-НЕ, второй вход icoMi-iyTa

го

1

1

t;j.OT-.-- „I.I ,

II J

33

Ij- -

«™

г L .L,.,&l

s

«p-i/a J

f

Ii

IL.r,.,:,,-..

r L

V

- J,

Л

,т-,

Си,гнал на первом выводе генератора 1

Сигнал на счетчи/(а Z

о

с иг и а/1 на Второй Вы)1оде генератора 1

tii2Hafi на деш,и(рра пора8

C(4ZHu/i на Oh/ходе 1 деши,(ррап7ора /

С(гн«/ на Sbf)( 2 дешисрратора

Сц,гнаи на Вь1)оде Веш щратора

Сигнал на Вы коде 3 дец и р&тор«

Сигнй/ на Bifixode т риг 2 ер а 10

Сигна/j на выходе элемента И-НЕ 1

Сигнал на выходе элемен1па И-НЕ5

9viг.

Л/f

/Ifftf

., о

S

Л/tt-f

Л/fTf

йиНИЫ&

/f i /r Aia

Авторы

Даты

1988-12-07—Публикация

1987-04-27—Подача