Изобретение относится к области бумагоделательной и металлообрабатывающей техники, может найти применение при регулировании скорости вращения валков бумагоделательных машин и прокатных станов и в станках с числовым программным управлением и является усоверщен- ствованием известного регулятора по авт. св. № 883864.

Целью изобретения является повышение быстродействия регулятора.

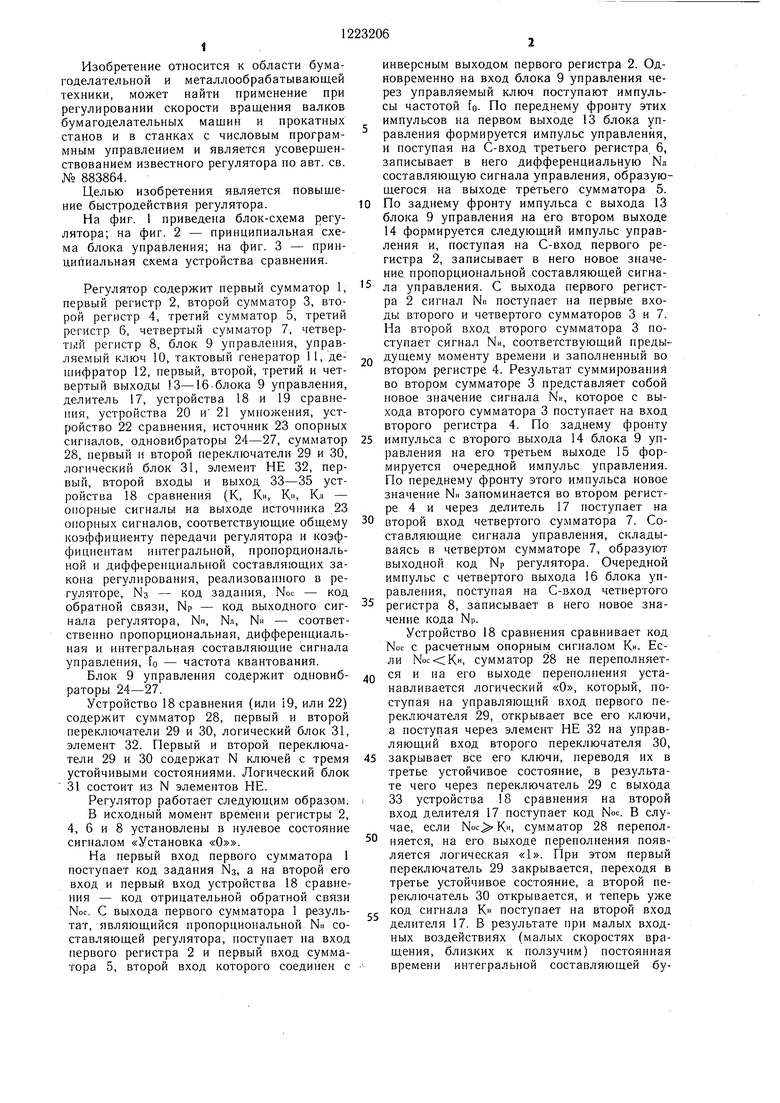

На фиг. 1 приведена блок-схема регулятора; на фиг. 2 - принципиальная схема блока управления; на фиг. 3 - принципиальная схема устройства сравнения.

ние пропорциональной составляющей сигнаРегулятор содержит первый сумматор 1, ла управления. С выхода первого регист- первый регистр 2, второй сумматор 3, второй регистр 4, третий сумматор 5, третий регистр 6, четвертый сумматор 7, четвертый регистр 8, блок 9 управления, управляемый ключ 10, тактовый генератор 11, дешифратор 12, первый, второй, третий и чет20

вертый выходы 3-16-блока 9 управления, делитель 17, устройства 18 и 19 сравнения, устройства 20 и 21 умножения, устройство 22 сравнения, источник 23 опорных

ра 2 сигнал Nn поступает на первые входы второго и четвертого сумматоров 3 и 7. На второй вход второго сумматора 3 поступает сигнал NH, соответствующий предыдущему моменту времени и заполненный во втором регистре 4. Результат суммирования во втором сумматоре 3 представляет собой новое значение сигнала NH, которое с выхода второго сумматора 3 поступает на вход второго регистра 4. По заднему фронту

сигналов, одновибраторы 24-27, сумматор 25 импульса с второго выхода 14 блока 9 уп28, первый и второй переключатели 29 и 30, логический блок 31, элемент НЕ 32, первый, второй входы и выход 33-35 устройства 18 сравнения (К, К, К, Кд - опорные сигналы на выходе источника ,23

равления на его третьем выходе 15 формируется очередной импульс управления. По переднему фронту этого импульса новое значение Nn запоминается во втором регистре 4 и через делитель 17 поступает на

40

опорных сигналов, соответствующие общему 30 второй вход четвертого сумматора 7. Co- коэффициенту передачи регулятора и коэффициентам интегральной, пропорциональной и дифференциальной составляющих закона регулирования, реализованного в регуляторе, NS - код задания, Noc - код обратной связи, Np - код выходного сигнала регулятора, Nn, Nд, N - соответственно пропорциональная, дифференциальная и интегральная составляющие сигнала управления, fo - частота квантования.

Блок 9 управления содержит одновибраторы 24-27.

Устройство 18 сравнения (или 19, или 22) содержит сумматор 28, первый и второй переключатели 29 и 30, логический блок 31, элемент 32. Первый и второй переключатели 29 и 30 содержат N ключей с тремя устойч)1выми состояниями. Логический блок 31 состоит из N элементов НЕ.

Регулятор работает следующим образом.

В исходный момент времени регистры 2, 4, 6 и 8 установлены в нулевое состояние сигналом «Установка «О.

На первый вход первого сумматора 1 поступает код задания NS, а на второй его вход и первый вход устройства 18 сравнения - код отрицательной обратной связи NOC. С выхода первого сумматора 1 результат, являющийся пропорциональной Nn составляющей регулятора, ностунает на вход первого регистра 2 и первый вход сумматора 5, второй вход которого соединен с

ставляющие сигнала управления, складываясь в четвертом сумматоре 7, образуют выходной код NP регулятора. Очередной импульс с четвертого выхода 16 блока управления, поступая на С-вход четвертого регистра 8, записывает в него повое значение кода N|).

Устройство 18 сравнения сравнивает код NOC с расчетным опорным сигналом Ки. Если , сумматор 28 не переполняется и на его выходе переполнения устанавливается логический «О, который, поступая на управляющий вход первого переключателя 29, открывает все его ключи, а поступая через элемент НЕ 32 па управляющий вход второго переключателя 30, закрывает все его ключи, переводя их в третье устойчивое состояние, в результате чего через переключатель 29 с выхода 33 устройства 18 сравнения на второй вход делителя 17 поступает код NOC. В случае, если NOC.K, сумматор 28 переполняется, на его выходе переполнения появляется логическая «1. При этом первый переключатель 29 закрывается, переходя в третье устойчивое состояние, а второй переключатель 30 открывается, и теперь уже код сигнала К поступает на второй вход делителя 17. В результате при малых входных воздействиях (малых скоростях вращения, близких к ползучим) постоянная времени интегральной составляющей бу45

50

55

инверсным выходом первого регистра 2. Одновременно на вход блока 9 управления через управляемый ключ поступают импульсы частотой fo. По переднему фронту этих импульсов на первом выходе 13 блока управления формируется импульс управления, и поступая на С-вход третьего регистра 6, записывает в него дифференциальную К д составляющую сигнала управления, образующегося на выходе третьего сумматора 5. По заднему фронту импульса с выхода 13 блока 9 управления на его втором выходе 14 формируется следующий импульс управления и, поступая на С-вход первого регистра 2, записывает в него новое значела управления. С выхода первого регист-

ра 2 сигнал Nn поступает на первые входы второго и четвертого сумматоров 3 и 7. На второй вход второго сумматора 3 поступает сигнал NH, соответствующий предыдущему моменту времени и заполненный во втором регистре 4. Результат суммирования во втором сумматоре 3 представляет собой новое значение сигнала NH, которое с выхода второго сумматора 3 поступает на вход второго регистра 4. По заднему фронту

импульса с второго выхода 14 блока 9 управления на его третьем выходе 15 формируется очередной импульс управления. По переднему фронту этого импульса новое значение Nn запоминается во втором регистре 4 и через делитель 17 поступает на

второй вход четвертого сумматора 7. Co-

0

0 второй вход четвертого сумматора 7. Co-

ставляющие сигнала управления, складываясь в четвертом сумматоре 7, образуют выходной код NP регулятора. Очередной импульс с четвертого выхода 16 блока управления, поступая на С-вход четвертого 5 регистра 8, записывает в него повое значение кода N|).

Устройство 18 сравнения сравнивает код NOC с расчетным опорным сигналом Ки. Если , сумматор 28 не переполняется и на его выходе переполнения устанавливается логический «О, который, поступая на управляющий вход первого переключателя 29, открывает все его ключи, а поступая через элемент НЕ 32 па управляющий вход второго переключателя 30, закрывает все его ключи, переводя их в третье устойчивое состояние, в результате чего через переключатель 29 с выхода 33 устройства 18 сравнения на второй вход делителя 17 поступает код NOC. В случае, если NOC.K, сумматор 28 переполняется, на его выходе переполнения появляется логическая «1. При этом первый переключатель 29 закрывается, переходя в третье устойчивое состояние, а второй переключатель 30 открывается, и теперь уже код сигнала К поступает на второй вход делителя 17. В результате при малых входных воздействиях (малых скоростях вращения, близких к ползучим) постоянная времени интегральной составляющей бу5

0

5

дет изменяться прямо пропорционально коду Noc.Пpи этом время реакции регулятора существенно сокращается, т. е. быстродействие возрастает. С целью исключения переполнения второго сумматора 3 между его выходом и входом второго регистра 4 необходимо установить устройство 19 сравнения, ограничивающее код с выхода сумматора 3 на заданном уровне. Устройство 20 и 21 умножения необходимы для возможности изменения параметров регулятора, т. е. коэффициентов Кп и Кд соответственно при порциональной Nn и дифференциальной Nfl составляющих сигнала управления регулятора. Устройство 22 сравнения служит для ограничения выходного кода Np.

Источник 23 опорных сигналов может представлять собой источник питания и набор ключей и предназначен для задания коэффициентов и величины ограничений в регуляторе.

Описанный процесс повторяется с приходом последующего импульса частоты fo. В блоке 9 управления могут быть использованы одновибраторы из серии интегральных схем К155, например К155АГ1 или К155АГЗ.

В переключателях 29 и 30 в качестве ключей с тремя устойчивыми состояниями на выходе могут быть использованы интегральные схемы К589АП16.

Описанный алгоритм работы регулятора может быть реализован программными средствами на базе микропроцессора или микро-ЭВМ.

По сравнению с известным применение данного регулятора в электроприводе позволяет повысить его быстродействие при малых (ползучих) скоростях вращения, что определяется кратностью изменения постоянной интегрирования регулятора и границей устойчивости электропривода. Расчетное время реверса при номинальном токе и скорости 0,1 об/мин в электроприводе, использующем известный регулятор, превышает 4 с. Расчетное время реверса в таком же режиме при использовании предлагаемого регулятора снижается до 0,4-

5

0,5 с, т. е. быстродействие регулятора повышается примерно в десять раз.

При использовании данного электропривода, например, в металлорежущих станках, может быть получен экономический эффект за счет повышения точности и скорости обработки деталей, т. е. повышения производительности станка.

Формула изобретения

0I. Цифровой пропорционально-интегрально-дифференциальный регулятор по авт. св. № 883864, отличающийся тем, что, с целью повышения быстродействия регулятора, в нем дополнительно установлены делитель, третье устройство сравнения и источник опорных сигналов, причем выход второго регистра соединен с вторым входом четвертого сумматора через делитель, подключенный вторым входом к выходу третьего устройства сравнения, соединенного вхо0 дами соответственно с первым входом первого сумматора и выходом источника опорных сигналов.

2.Регулятор по п. 1, отличающийся тем, что блок yпpaвJ eния содержит четыре последовательно соединенных одновибратора,

5 причем вход первого одновибратбра и выходы первого, второго, третьего и четвертого одновибраторов являются входом и первым, вторым, третьим и четвертым выходами блока управления.

3.Регулятор по п. 1, отличающийся тем, что устройство сравнения содержит сумматор, два переключателя, логический блок и элемент НЕ, причем первый вход сумматора соединен с информационным входом первого переключателя, второй вход - с выходом логического блока, а выход - с управляющим входом первого переключателя и входом элемента НЕ, подключенного выходом к управляющему входу второго переключателя, информационным входом соединенного с входом логического блока, а

выходом - с выходом первого переключателя, информационные входы первого и второго переключателей и их соединенные выходы являются первым, вторым входами и выходом устройства сравнения.

0

Фиг. г

18(19.22)

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1979 |

|

SU883864A1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Установка для присоединения проволочных выводов | 1991 |

|

SU1773643A1 |

| Устройство для оценки функционального состояния головного мозга | 1989 |

|

SU1814871A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство сопряжения функциональных блоков систем управления | 1986 |

|

SU1441347A1 |

| Привод | 1977 |

|

SU732806A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

Изобретение относится к бумагоделательной и металлообрабатывающей технике, может найти применение при регулировании скорости вращения валов бумагоделательных мащин и прокатных станов и в станках с числовым программным управлением и является усоверщенствованием известного регулятора по авт. св. № 883864. В регуляторе решается задача изменения коэффициента передачи интегральной составляющей регулятора в зависимости от сигнала обратной связи и опорного сигнала. Коды сигналов задания и обратной связи поступают на вход первого сумматора (С), который вместе с первым регистром формирует пропорциональную составляющую управляющего сигнала, которая поступает иа первый вход четвертого С и на первый вход второго и третьего С. Третий С и третий регистр формируют дифференциальную составляющую сигнала управления, которая подается на третий вход четвертого С. Второй С и второй регистр формируют интегральную составляющую сигнала управления, который, пройдя через делитель, суммируется с сигналом управления. Выходной сигнал четвертого § С через четвертый регистр поступает на выход регулятора. Код сигнала обратной /Л связи сравнивается с опорным сигналом, а результат сравнения подается на второй вход делителя и осуществляет изменение величины интегральной составляющей сигнала управления. 2 з.п ф-лы, 3 ил. to to оо to о О5

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1979 |

|

SU883864A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-04—Подача