Изобретение относится к вычислительной технике и может быть использовано . при реализации быстродействующих арифметических устройств ЭВМ и специализированных вычислителей.

Цель изобретения - повышение быстродействия устройства.

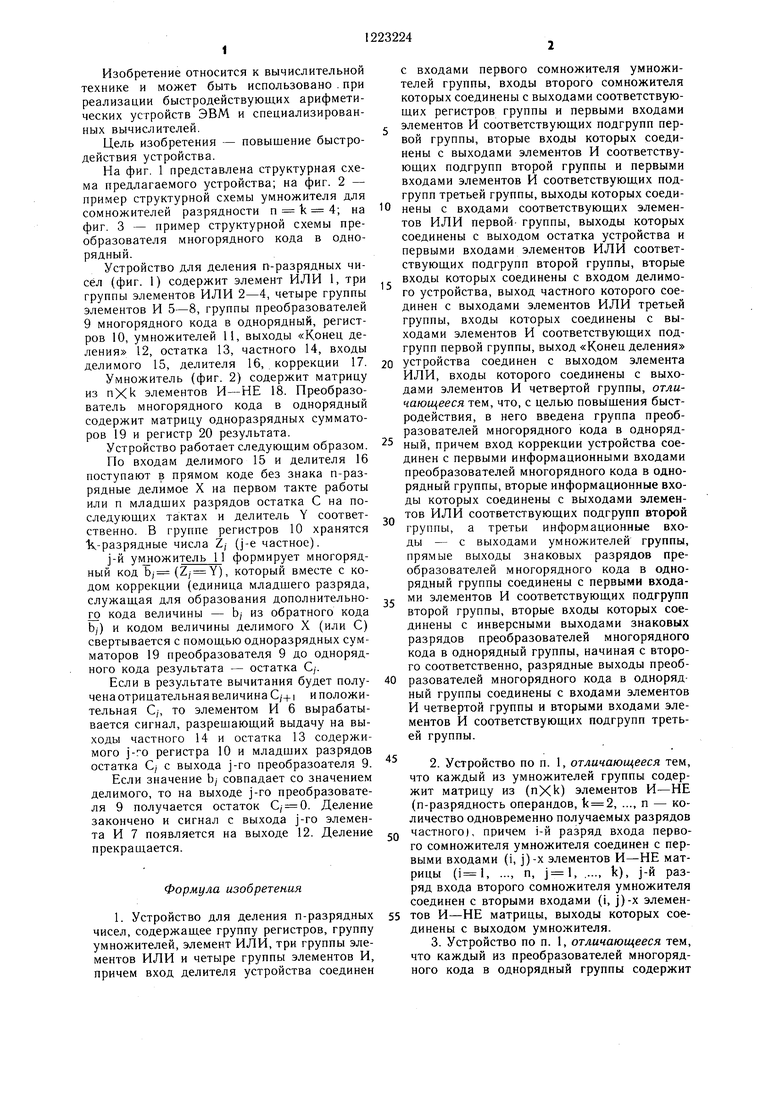

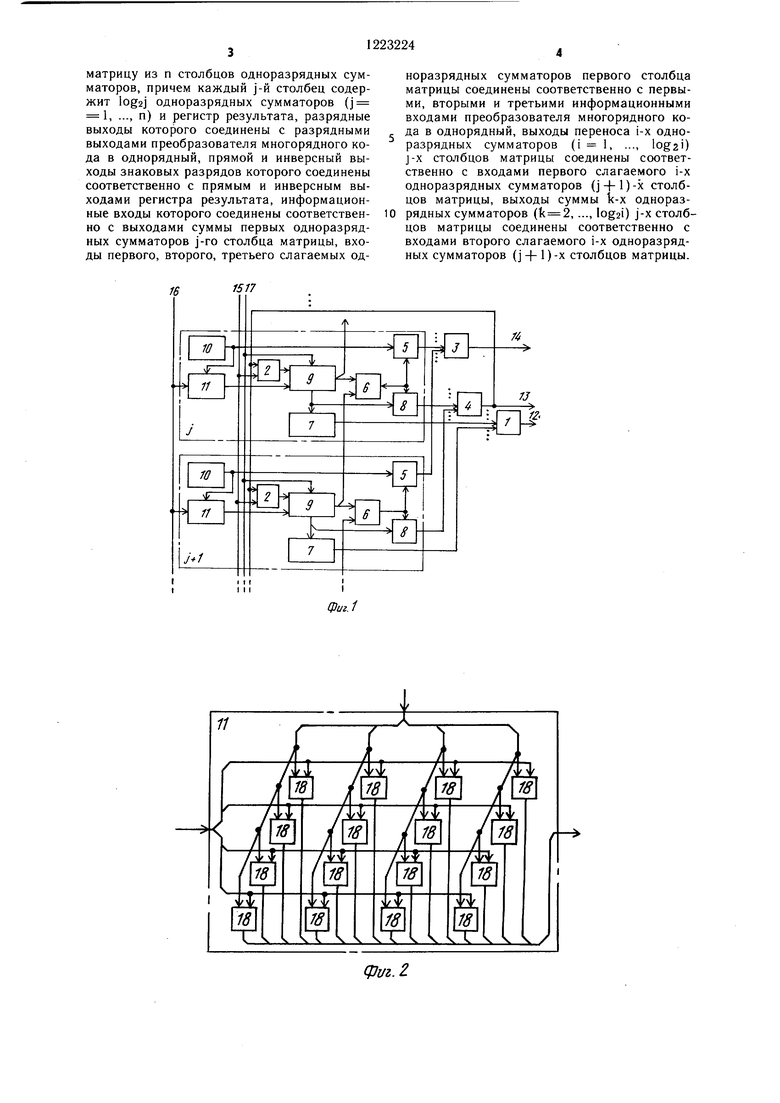

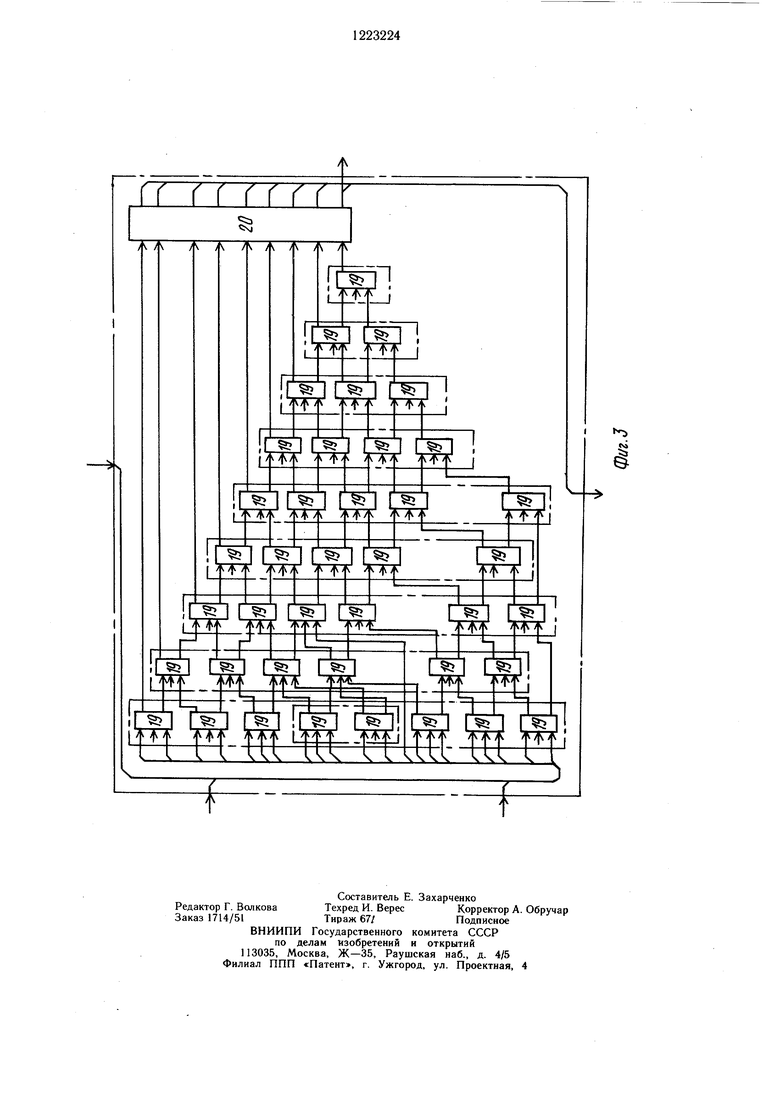

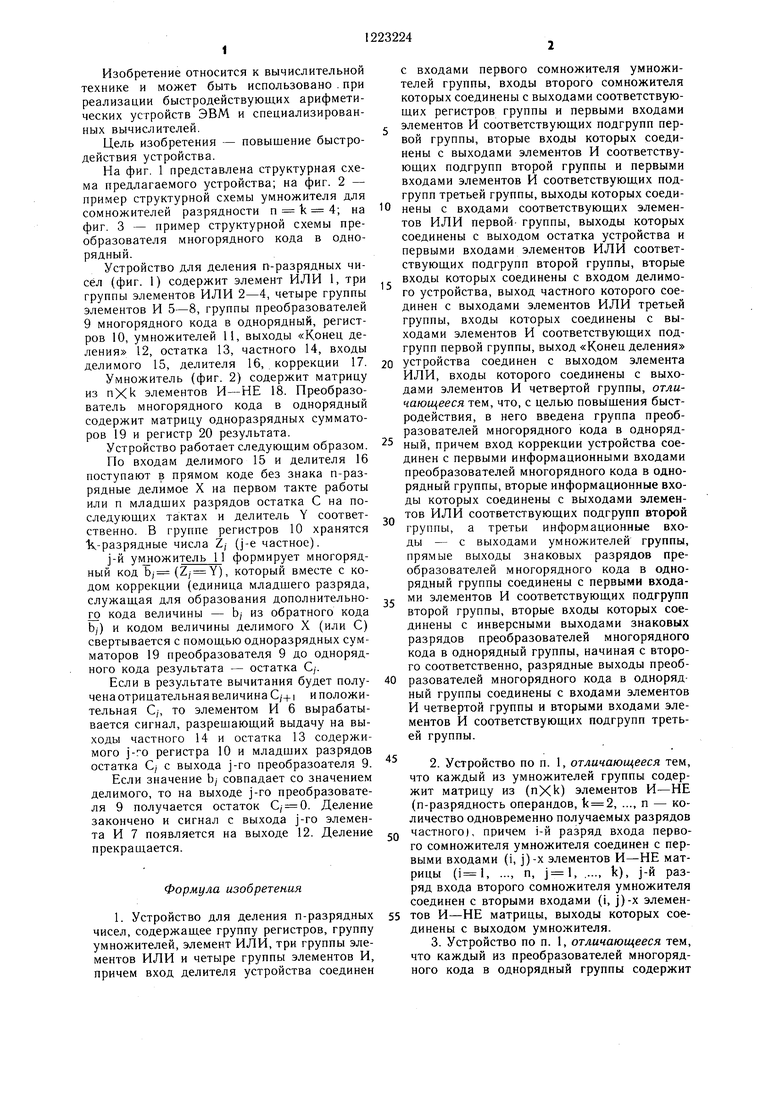

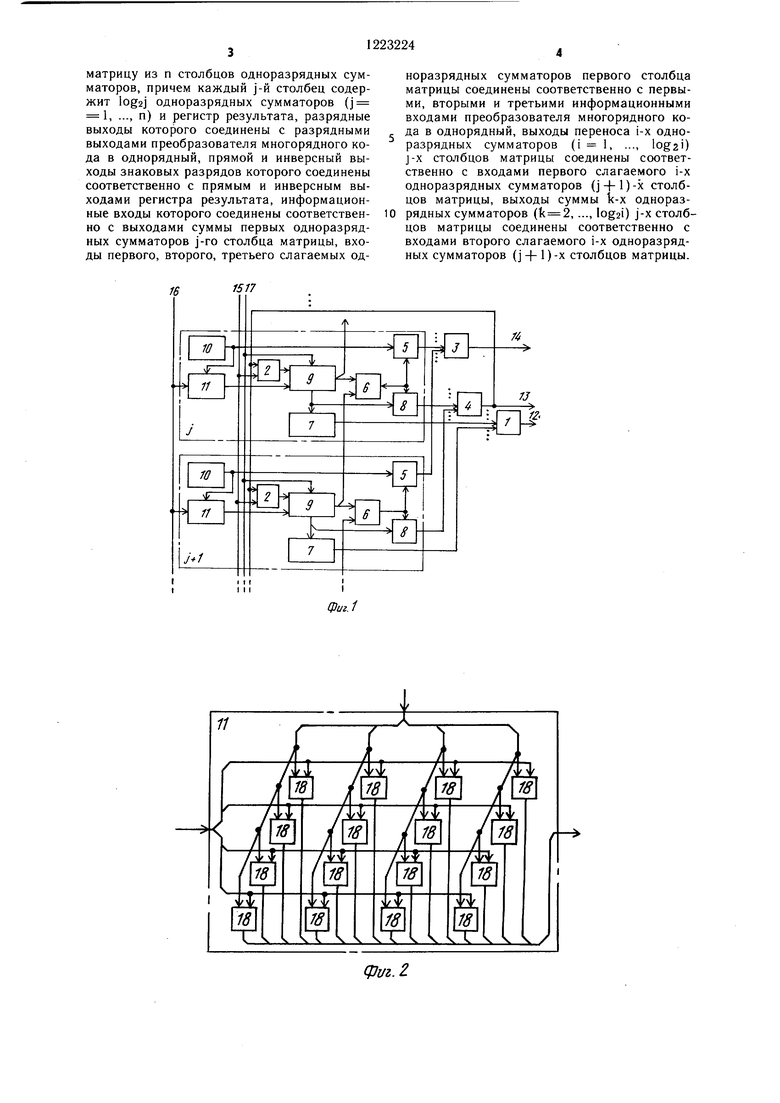

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - пример структурной схемы умножителя для сомножителей разрядности п k 4; на фиг. 3 - пример структурной схемы преобразователя многорядного кода в однорядный.

Устройство для деления п-разрядных чисел (фиг. 1) содержит элемент ИЛИ 1, три группы элементов ИЛИ 2-4, четыре группы элементов И 5-8, группы преобразователей 9 многорядного кода в однорядный, регистров 10, умножителей 11, выходы «Конец деления 12, остатка 13, частного 14, входы делимого 15, делителя 16, коррекции 17.

Умножитель (фиг. 2) содержит матрицу из nXk элементов И-НЕ 18. Преобразователь многорядного кода в однорядный содержит матрицу одноразрядных сумматоров 19 и регистр 20 результата.

Устройство работает следующим образом.

По входам делимого 15 и делителя 16 поступают в прямом коде без знака п-раз- рядные делимое X на первом такте работы или п младших разрядов остатка С на последующих тактах и делитель Y соответственно. В группе регистров 10 хранятся К-разрядные числа Z/ (j-e частное).

j-й умножитель 11 формирует многорядный код bj (Z/ Y), который вместе с кодом коррекции (единица младщего разряда, служащая для образования дополнительного кода величины - Ь,- из обратного кода by) и кодом величины делимого X (или С) свертывается с помощью одноразрядных сумматоров 19 преобразователя 9 до однорядного кода результата - остатка С,-.

Если в результате вычитания будет получена отрицательная величина C/+i и положительная С/, то элементом И 6 вырабатывается сигнал, разрешающий выдачу на выходы частного 14 и остатка 13 содержимого регистра 10 и младших разрядов остатка С; с выхода j-го преобразоателя 9.

Если значение Ь, совпадает со значением делимого, то на выходе j-ro преобразователя 9 получается остаток С/ 0. Деление закончено и сигнал с выхода j-ro элемента И 7 появляется на выходе 12. Деление прекращается.

Формула изобретения

1. Устройство для деления п-разрядных чисел, содержащее группу регистров, группу умножителей, элемент ИЛИ, три группы элементов ИЛИ и четыре группы элементов И, причем вход делителя устройства соединен

с входами первого сомножителя умножителей группы, входы второго сомножителя которых соединены с выходами соответствующих регистров группы и первыми входами

элементов И соответствующих подгрупп первой группы, вторые входы которых соединены с выходами элементов И соответствующих подгрупп второй группы и первыми входами элементов И соответствующих подгрупп третьей группы, выходы которых соединены с входами соответствующих элементов ИЛИ первой группы, выходы которых соединены с выходом остатка устройства и первыми входами элементов ИЛИ соответствующих подгрупп второй группы, вторые входы которых соединены с входом делимого устройства, выход частного которого соединен с выходами элементов ИЛИ третьей группы, входы которых соединены с выходами элементов И соответствующих подгрупп первой группы, выход «Конец деления

0 устройства соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И четвертой группы, отличающееся тем, что, с целью повыщения быстродействия, в него введена группа преобразователей многорядного кода в одноряд

ныи, причем вход коррекции устройства соединен с первыми информационными входами преобразователей многорядного кода в однорядный группы, вторые информационные входы которых соединены с выходами элементов ИЛИ соответствующих подгрупп второй группы, а третьи информационные входы - с выходами умножителей группы, прямые выходы знаковых разрядов преобразователей многорядного кода в однорядный группы соединены с первыми входами элементов И соответствующих подгрупп второй группы, вторые входы которых соединены с инверсными выходами знаковых разрядов преобразователей многорядного кода в однорядный группы, начиная с второго соответственно, разрядные выходы преоб0 разователей многорядного кода в однорядный группы соединены с входами элементов И четвертой группы и вторыми входами элементов И соответствующих подгрупп третьей группы.

2.Устройство по п. 1, отличающееся тем, что каждый из умножителей группы содержит матрицу из (nXk) элементов И-НЕ (п-разрядность операндов, , ..., п - количество одновременно получаемых разрядов

Q частного), причем i-й разряд входа первого сомножителя умножителя соединен с первыми входами (i, j)-x элементов И-НЕ матрицы (, ..., п, , ...., k), j-й разряд входа второго сомножителя умножителя соединен с вторыми входами (i, j)-x элемен5 тов И-НЕ матрицы, выходы которых соединены с выходом умножителя.

3.Устройство по п. 1, отличающееся тем, что каждый из преобразователей многорядного кода в однорядный группы содержит

матрицу из п столбцов одноразрядных сумматоров, причем каждый j-й столбец содержит log2J одноразрядных сумматоров (j 1, ..., п) и регистр результата, разрядные выходы которого соединены с разрядными выходами преобразователя многорядного кода в однорядный, прямой и инверсный выходы знаковых разрядов которого соединены соответственно с прямым и инверсным выходами регистра результата, информационные входы которого соединены соответственно с выходами суммы первых одноразрядных сумматоров j-ro столбца матрицы, входы первого, второго, третьего слагаемых од16

1517

норазрядных сумматоров первого столбца матрицы соединены соответственно с первыми, вторыми и третьими информационными входами преобразователя многорядного кода в однорядный, выходы переноса i-x одноразрядных сумматоров (i 1, ..., loggi) j-x столбцов матрицы соединены соответственно с входами первого слагаемого i-x одноразрядных сумматоров (j-|-l)-x столбцов матрицы, выходы суммы 1с-х одноразрядных сумматоров (, ..., Iog2i) j-x столбцов матрицы соединены соответственно с входами второго слагаемого i-x одноразрядных сумматоров (J + 1)-х столбцов матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| МНОГОУРОВНЕВАЯ M-МЕРНАЯ МАТРИЧНАЯ ВЫЧИСЛИТЕЛЬНАЯ СТРУКТУРА ВЕРТИКАЛЬНОЙ АРИФМЕТИКИ В.М. ТАРАНУХИ | 2003 |

|

RU2265239C2 |

| Устройство для умножения двоичных чисел в дополнительном коде | 1983 |

|

SU1191907A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

Изобретение относится к вычислительной технике и может быть использовано при реализации быстродействующих арифметических устройств ЭВМ и специализированных вычислителей. Цель изобретения - повышение быстродействия устройства. Устройство содержит группу умножителей, элемент ИЛИ, три группы элементов ИЛИ, четыре группы элементов, группу регистров. В него введена группа преобразователей многорядного кода в однорядный, изменяется коммутация элементов устройства, а каждый из умножителей группы содержит матрицу из (nXk) элементов И-НЕ. 2з. п. ф-лы; 3 нл. to 1C со to ю

18 ТЧ

1ч ЧТ

фиг. 2.

| Карцев М: А | |||

| и Брик В | |||

| А | |||

| Вычислительные системы и синхронная арифметика М.: Радио и связь, 1981 | |||

| Авторское свидетельство СССР № 1097999, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1984-09-11—Подача