I 1-Й

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке арифметических устройств ЭВМ. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистры 1, 2 множимого и множителя, блок 5 вычисления разрядного значения произведения, буферный регистр 3 и регистр 4 частичного произведения. 3 ил.

I mi -р i in I

JWчо

lifts

с

Фиг. 1

Изобретение относится к вычисли-- тыльной технике и может быть исполь- зфвано при построении арифметических устройств ЭВМ,

Цель изобретения - повышение быстродействия устройства о

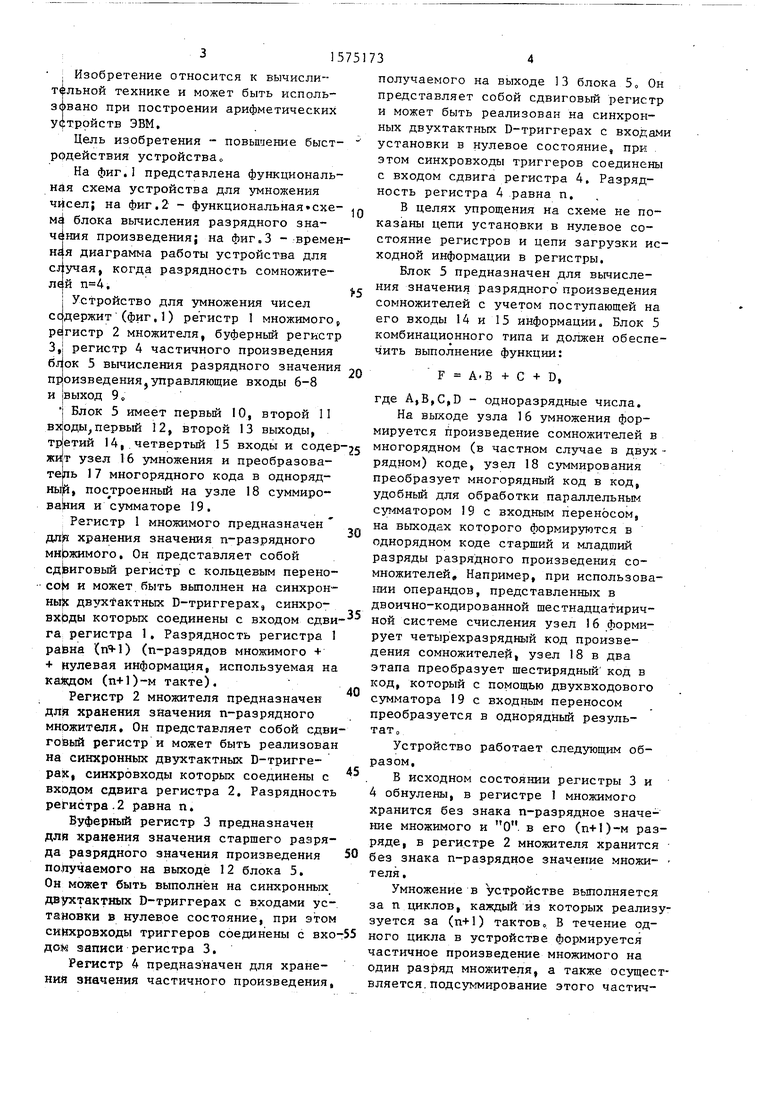

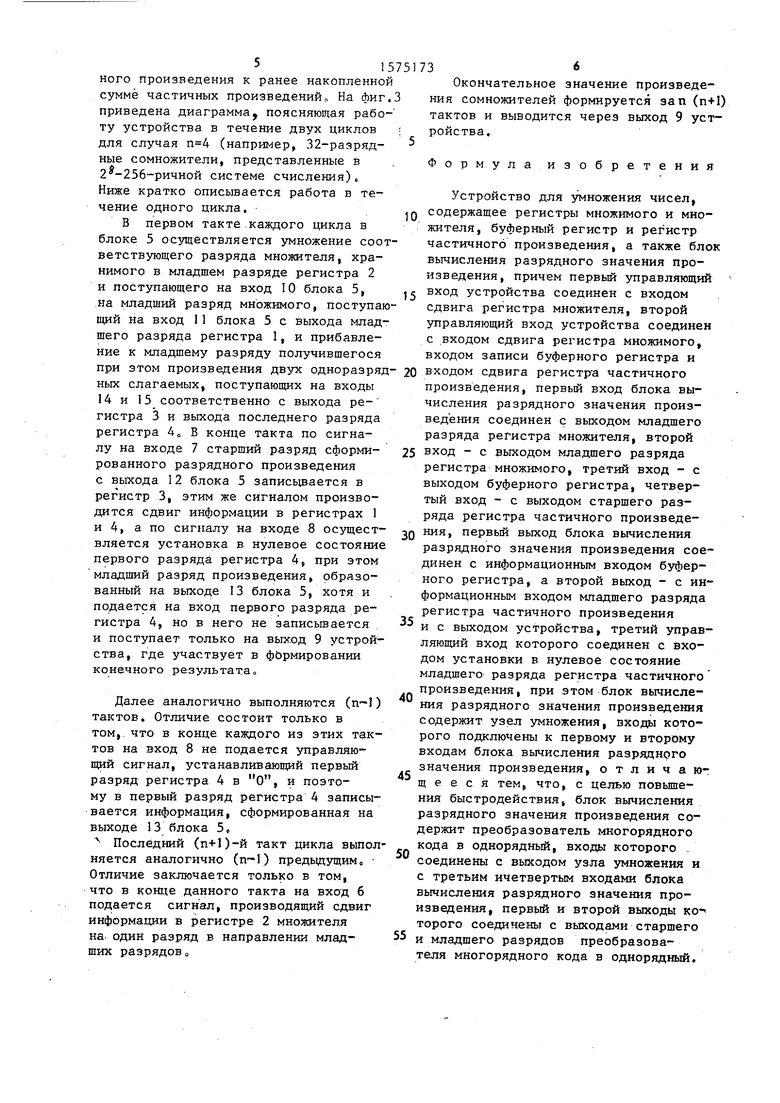

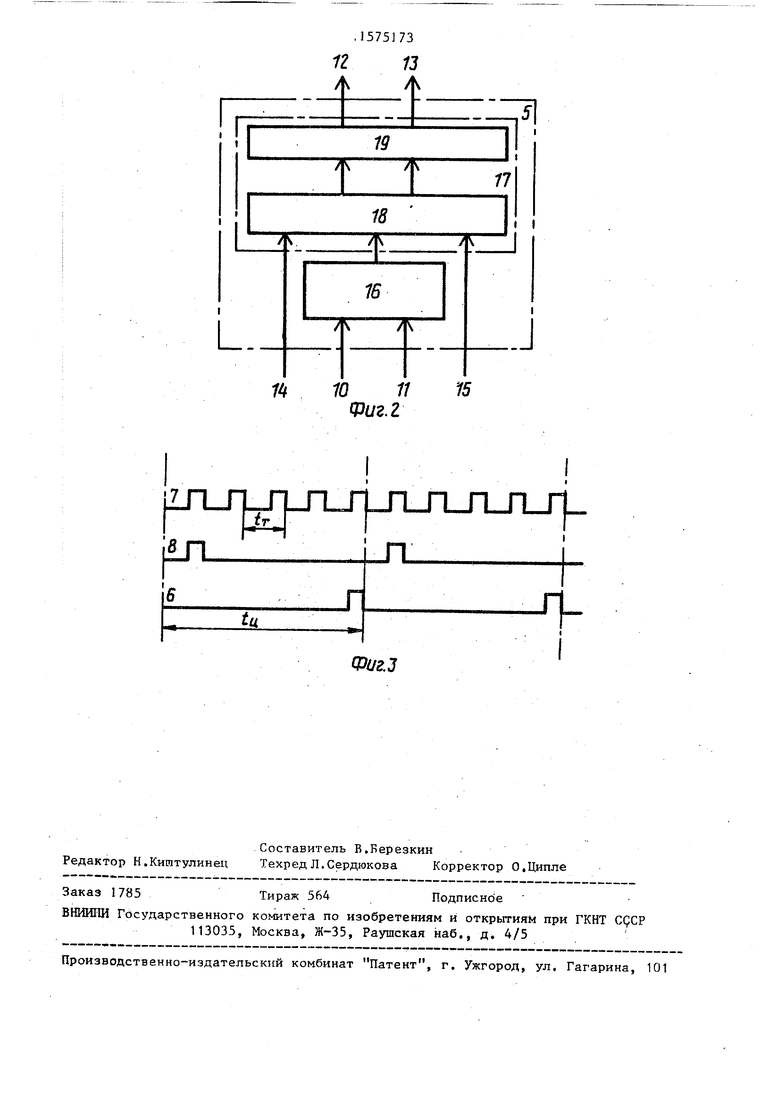

На фиг.1 представлена функциональная схема устройства для умножения чисел; на фиг.2 - функциональная«схема блока вычисления разрядного значения произведения; на фиг.З - временная диаграмма работы устройства для случая, когда разрядность сомножителей ,

, Устройство для умножения чисел содержит (фиг,1) регистр 1 множимого, регистр 2 множителя, буферный регистр 3, регистр 4 частичного произведения 5 вычисления разрядного значения произведения управляющие входы 6-8 и выход 90

Блок 5 имеет первьй 10, второй II входы,первый 12, второй 13 выходы,

10

«5

20

получаемого на выходе 13 блока 5„ Он представляет собой сдвиговый регистр и может быть реализован на синхронных двухтактных D-триггерах с входами установки в нулевое состояние, при этом синхровходы триггеров соединены с входом сдвига регистра 4, Разрядность регистра 4 равна п.

В целях упрощения на схеме не показаны цепи установки в нулевое состояние регистров и цепи загрузки исходной информации в регистры,

Блок 5 предназначен для вычисления значения разрядного произведения сомножителей с учетом поступающей на его входы 14 и 15 информации. Блок 5 комбинационного типа и должен обеспечить выполнение функции:

F А.В + С + D,

где A,B,C,D - одноразрядные числа.

На выходе узла 16 умножения формируется произведение сомножителей в

третий 14, четвертый 15 входы и содер- многорядном (в частном случае в двух ,-35

40

узел 16 умножения и преобразователь 17 многорядного кода в однорядны, построенный на узле 18 суммиро- и сумматоре 19.

Регистр 1 множимого предназначен пда хранения значения п-разрядного мнЬжимого, Он представляет собой сдЬиговый регистр с кольцевым переносов и может быть выполнен на синхронных двухтактных D-триггерах, синхровходы которых соединены с входом сдви га регистра 1, Разрядность регистра 1 равна (пЧ-1) (n-разрядов множимого + + нулевая информация, используемая на каждом (п+1)-м такте).

Регистр 2 множителя предназначен для хранения значения п-разрядного множителя. Он представляет собой сдвиговый регистр и может быть реализован на синхронных двухтактных D-триггерах, синхровходы которых соединены с входом сдвига регистра 2, Разрядность регистра 2 равна п.

Буферный регистр 3 предназначен для хранения значения старшего разряда разрядного значения произведения получаемого на выходе 12 блока 5. Он может быть выполнен на синхронных двухтактных D-триггерах с входами установки в нулевое состояние, при этом сийхровходы триггеров соединены с вхо-55 дон записи регистра 3.

Регистр 4 предназначен для хранения значения частичного произведения,

45

50

рядном) коде, узел 18 суммирования преобразует многорядный код в код, удобньй для обработки параллельным сумматором 19 с входным переносом, на выходах которого формируются в однорядном коде старший и младший разряды разрядного произведения сомножителей. Например, при использовании операндов, представленных в двоично-кодированной шестнадцатиричной системе счисления узел 16 формирует четырехразрядный код произведения сомножителей, узел 18 в два этапа преобразует шестирядный код в код, который с помощью двухвходового сумматора 19 с входным переносом преобразуется в однорядный результат

Устройство работает следующим образом,

В исходном состоянии регистры 3 и 4 обнулены, в регистре 1 множимого хранится без знака n-разрядное значение множимого и О в его (п+1)-м разряде, в регистре 2 множителя хранится без знака n-разрядное значение множи- теля.

Умножение в устройстве выполняется за п циклов, каждый из которых реализу зуется за (п+1) тактов В течение одного цикла в устройстве формируется частичное произведение множимого на один разряд множителя, а также осущест вляется подсуммирование этого частич0

5

0

получаемого на выходе 13 блока 5„ Он представляет собой сдвиговый регистр и может быть реализован на синхронных двухтактных D-триггерах с входами установки в нулевое состояние, при этом синхровходы триггеров соединены с входом сдвига регистра 4, Разрядность регистра 4 равна п.

В целях упрощения на схеме не показаны цепи установки в нулевое состояние регистров и цепи загрузки исходной информации в регистры,

Блок 5 предназначен для вычисления значения разрядного произведения сомножителей с учетом поступающей на его входы 14 и 15 информации. Блок 5 комбинационного типа и должен обеспечить выполнение функции:

F А.В + С + D,

где A,B,C,D - одноразрядные числа.

На выходе узла 16 умножения формируется произведение сомножителей в

многорядном (в частном случае в двух 5

0

5

5

0

рядном) коде, узел 18 суммирования преобразует многорядный код в код, удобньй для обработки параллельным сумматором 19 с входным переносом, на выходах которого формируются в однорядном коде старший и младший разряды разрядного произведения сомножителей. Например, при использовании операндов, представленных в двоично-кодированной шестнадцатиричной системе счисления узел 16 формирует четырехразрядный код произведения сомножителей, узел 18 в два этапа преобразует шестирядный код в код, который с помощью двухвходового сумматора 19 с входным переносом преобразуется в однорядный результат

Устройство работает следующим образом,

В исходном состоянии регистры 3 и 4 обнулены, в регистре 1 множимого хранится без знака n-разрядное значение множимого и О в его (п+1)-м разряде, в регистре 2 множителя хранится без знака n-разрядное значение множи- - теля.

Умножение в устройстве выполняется за п циклов, каждый из которых реализу- зуется за (п+1) тактов В течение одного цикла в устройстве формируется частичное произведение множимого на один разряд множителя, а также осуществляется подсуммирование этого частич10

15

51575173

него произведения к ранее накопленной сумме частичных произведений. На фиг.З приведена диаграмма, поясняющая работу устройства в течение двух циклов для случая (например, 32-разрядные сомножители, представленные в 2 -256 ричной системе счисления). Ниже кратко описывается работа в течение одного цикла.

В первом такте каждого цикла в блоке 5 осуществляется умножение соответствующего разряда множителя, хранимого в младшем разряде регистра 2 и поступающего на вход 10 блока 5, на младший разряд множимого, поступающий на вход 11 блока 5 с выхода младшего разряда регистра 1, и прибавление к младшему разряду получившегося при

ных слагаемых, поступающих на входы 14 и 15 соответственно с выхода регистра 3 и выхода последнего разряда регистра 4„ В конце такта по сигналу на входе 7 старший разряд сформированного разрядного произведения с выхода 12 блока 5 записывается в регистр 3, этим же сигналом производится сдвиг информации в регистрах 1 и 4, а по сигналу на входе 8 осуществляется установка в нулевое состояние первого разряда регистра 4, при этом младший разряд произведения, образованный на выходе 13 блока 5, хотя и подается на вход первого разряда регистра 4, но в него не записывается и поступает только на выход 9 устройства, где участвует в формировании конечного результата

Окончательное значение произведения сомножителей формируется зап (п+1) тактов и выводится через выход 9 устройства.

Формула изобретения

Устройство для умножения чисел, содержащее регистры множимого и множителя, буферный регистр и регистр частичного произведения, а также блок вычисления разрядного значения произведения, причем первый управляющий вход устройства соединен с входом сдвига регистра множителя, второй управляющий вход устройства соединен с входом сдвига регистра множимого, входом записи буферного регистра и этом произведения двух одноразряд- 20 входом сдвига регистра частичного

25

30

35

произведения, первый вход блока вычисления разрядного значения произведения соединен с выходом младшего разряда регистра множителя, второй вход - с выходом младшего разряда регистра множимого, третий вход - с выходом буферного регистра, четвертый вход - с выходом старшего разряда регистра частичного произведения, первый выход блока вычисления разрядного значения произведения соединен с информационным входом буферного регистра, а второй выход - с информационным входом младшего разряда регистра частичного произведения и с выходом устройства, третий управляющий вход которого соединен с входом установки в нулевое состояние младшего разряда регистра частичного произведения, при этом блок вычисления разрядного значения произведения содержит узел умножения, входы которого подключены к первому и второму входам блока вычисления разрядного значения произведения, о т л и ч a rant e e с я тем, что, с целью повышения быстродействия, блок вычисления разрядного значения произведения содержит преобразователь многорядного кода в однорядный, входы которого соединены с выходом узла умножения и с третьим ичетвертым входами блока вычисления разрядного значения произведения, первый и второй выходы ко торого соединены с выходами старшего и младшего разрядов преобразователя многорядного кода в однорядный.

Далее аналогично выполняются (п-1) тактов. Отличие состоит только в том, что в конце каждого из этих тактов на вход 8 не подается управляющий сигнал, устанавливающий первый разряд регистра 4 в О, и поэтому в первый разряд регистра 4 записывается информация, сформированная на выходе 13 блока 5,

Л Последний (п+1)-й такт цикла выполняется аналогично (п-1) предыдущим. Отличие заключается только в том, что в конце данного такта на вход б подается сигнал, производящий сдвиг информации в регистре 2 множителя на один разряд в направлении младших разрядов„

10

20

15

20

5

0

5

0

5

0

5

произведения, первый вход блока вычисления разрядного значения произведения соединен с выходом младшего разряда регистра множителя, второй вход - с выходом младшего разряда регистра множимого, третий вход - с выходом буферного регистра, четвертый вход - с выходом старшего разряда регистра частичного произведения, первый выход блока вычисления разрядного значения произведения соединен с информационным входом буферного регистра, а второй выход - с информационным входом младшего разряда регистра частичного произведения и с выходом устройства, третий управляющий вход которого соединен с входом установки в нулевое состояние младшего разряда регистра частичного произведения, при этом блок вычисления разрядного значения произведения содержит узел умножения, входы которого подключены к первому и второму входам блока вычисления разрядного значения произведения, о т л и ч a rant e e с я тем, что, с целью повышения быстродействия, блок вычисления разрядного значения произведения содержит преобразователь многорядного кода в однорядный, входы которого соединены с выходом узла умножения и с третьим ичетвертым входами блока вычисления разрядного значения произведения, первый и второй выходы ко торого соединены с выходами старшего и младшего разрядов преобразователя многорядного кода в однорядный.

Г4 10 11 15 Фиг, Z

plJbJUTJlJTJTJ

|«П1 П

Фиг.З

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-06-30—Публикация

1988-02-29—Подача