Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях.

Цель изобретения - уменьшение аппаратурных затрат.

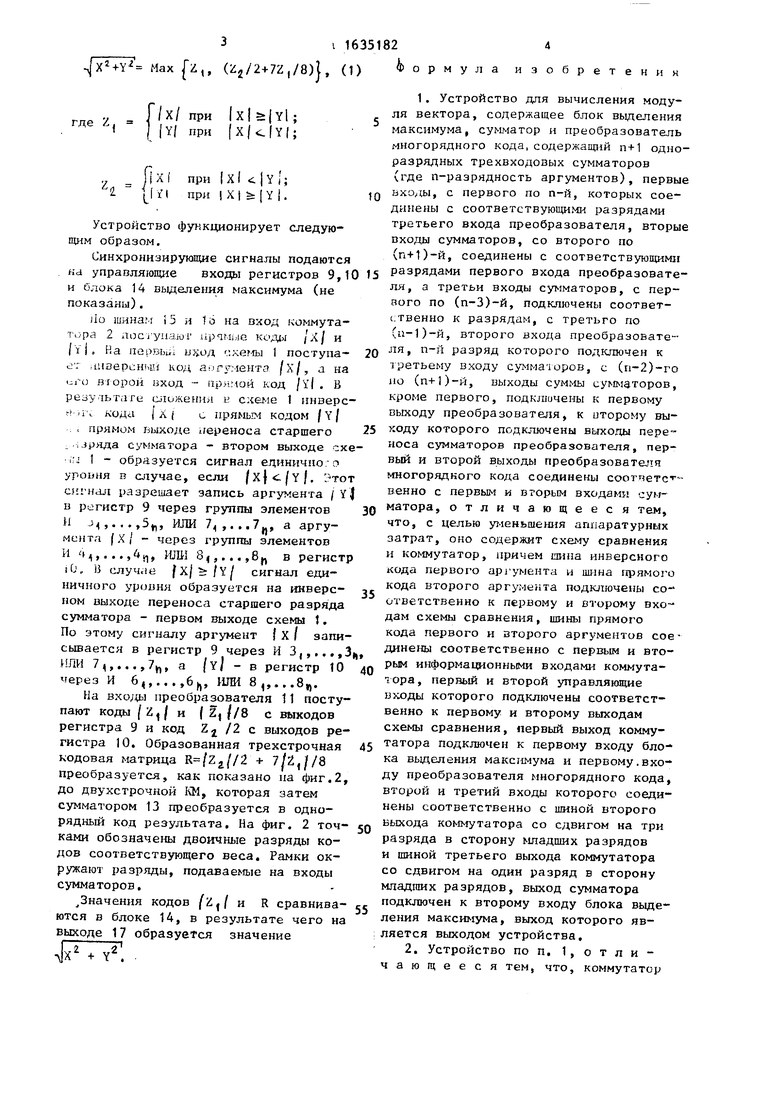

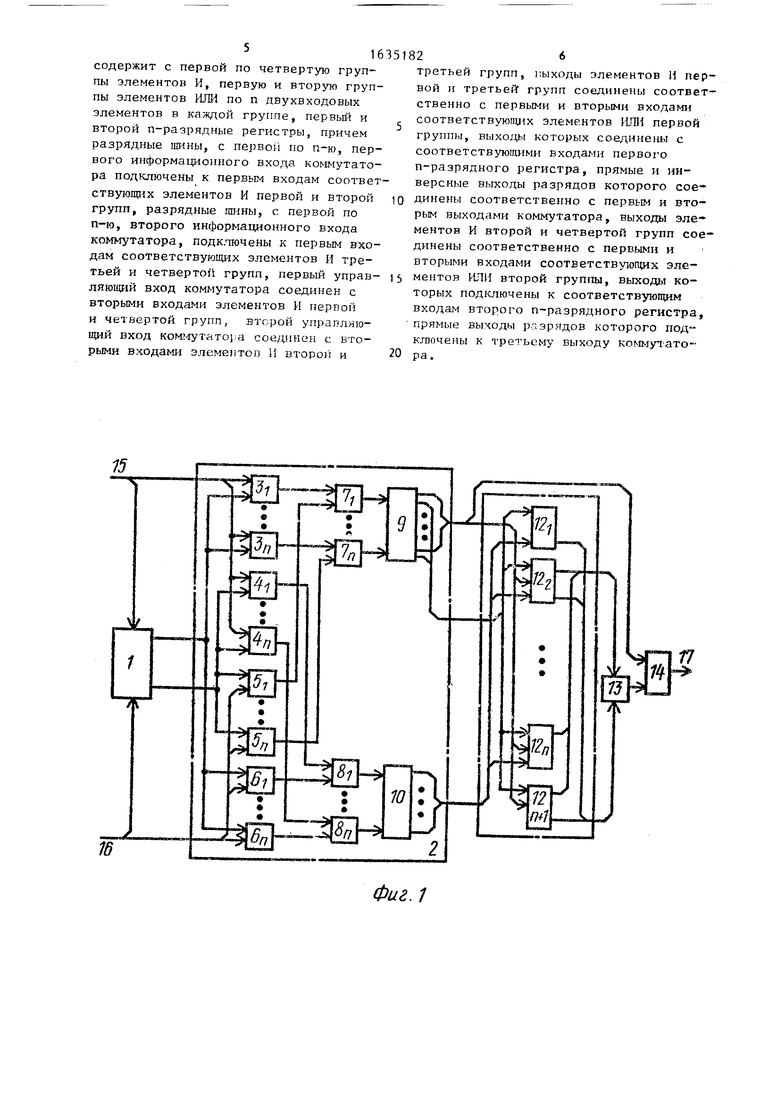

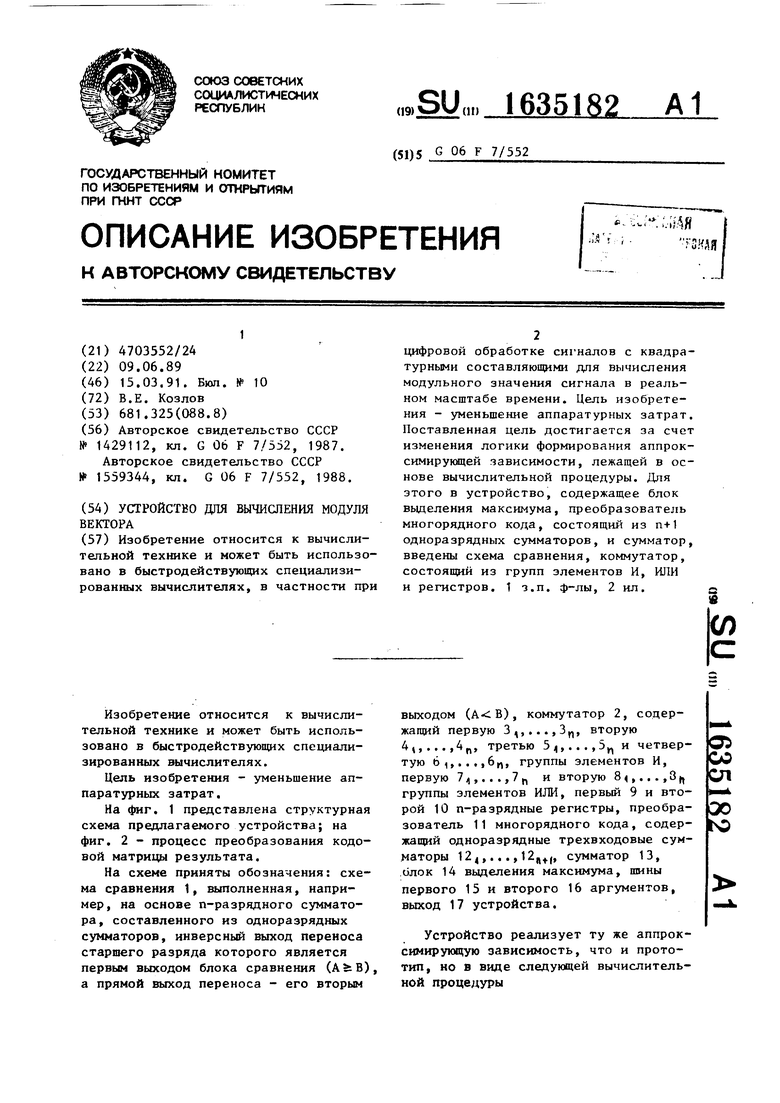

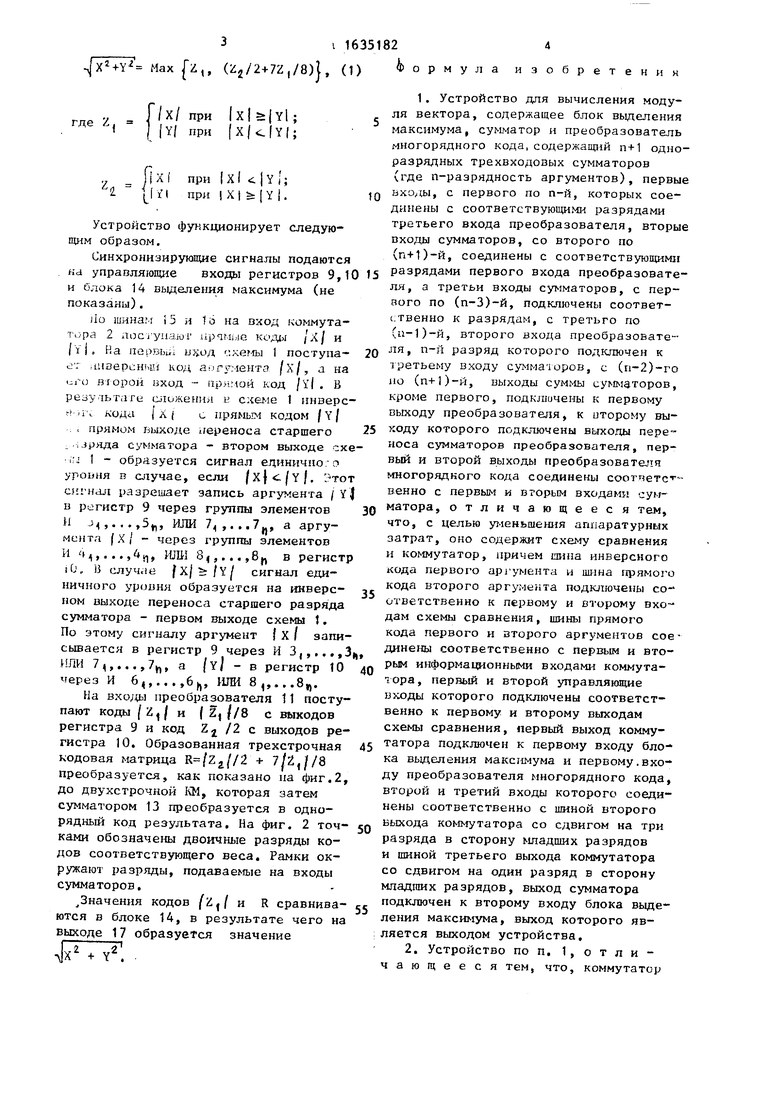

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - процесс преобразования кодовой матрицы результата.

На схеме приняты обозначения: схема сравнения 1, выполненная, например, на основе n-разрядного сумматора, составленного из одноразрядных сумматоров, инверсный выход переноса старшего разряда которого является первым выходом блока сравнения (AfcB), а прямой выход переноса - его вторым

выходом (А В) , коммутатор 2, содержащий первую 3,,...,3П, вторую 4 ,..., 4 „, третью 5 ,,,..., 5„ и четвертую 6 ,,..,,6П, группы элементов И, первую 7,),..., 7 h и вторую 8 «,..., 3 группы элементов ИЛИ, первый 9 и второй 10 n-разрядные регистры, преобразователь 11 многорядного кода, содержащий одноразрядные трехвходовые сумматоры 124,.. . ,12nf(, сумматор 13, блок 14 выделения максимума, шины первого 15 и второго 16 аргументов, выход 17 устройства.

Устройство реализует ту же аппроксимирующую зависимость, что и прототип, но в виде следующей вычислительной процедуры

3i 1635182

:XJ+Y2 Max z,, (Z2/2+72 ,/8)J , (1)

ормула изобретении

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля вектора | 1988 |

|

SU1559344A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1541602A1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Устройство для вычисления модуля вектора | 1987 |

|

SU1429112A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1305674A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях, в частности при цифровой обработке сигналов с квадратурными составляющими для вычисления модульного значения сигнала в реальном масштабе времени. Цель изобретения - уменьшение аппаратурных затрат. Поставленная цель достигается за счет изменения логики формирования аппроксимирующей зависимости, лежащей в основе вычислительной процедуры. Для этого в устройство, содержащее блок выделения максимума, преобразователь многорядного кода, состоящий из п+1 одноразрядных сумматоров, и сумматор, введены схема сравнения, коммутатор, состоящий из групп элементов И, ИЛИ и регистров. 1 з.п. ф-лы, 2 ил. Ј2 в

r« У j /X/ при |x|fe|Yl;

ГДе Z 1 |Y| при xfcfYf;

Пх I при Ul JYi; I (|f I при | X| SsjYl.

Устройство функционирует следующим образом.

Синхронизирующие сигналы подаются

10

ка управляющие входы регистров 9,10 15 Разрядами первого входа преобразовате20

25

30

и блока 14 выделения максимума (не показаны).

ао шинам 5 и 16 на вход коммута- Ti,pa 2 лооупайН ирчгьде коды /X/ и /х|. На нервы и ход пхемы 1 поступает -ашерсньш код аргумента /X/, а на

иГО ВТОРОЙ ВХОД - ПрлМОЙ КОД /Y|. В

резуаьтаге сложения н схеме 1 инверс- мч кода |А| L. прямым кодом /Y/

i прямом выходе переноса старшего „ . зряда сумматора - втором выходе схе- I .: I - образуется сигнал единично -п уроьня в случае, если . тот сигнал разрешает запись аргумента /Y| в регистр 9 через группы элементов И J4,...,5j,, ИЛИ 7,...7Й, а аргумента (X/ - через группы элементов И ц,. .. ,4,, ИЛИ 8,...,8ft в регистр |0„ В случае fX/5r/Y/ сигнал единичного уровня образуется на инверсном выходе переноса старшего разряда сумматора - первом выходе схемы 1. По этому сигналу аргумент { X / записывается в регистр 9 через И 3,,...,Зц, ИЛИ 7,...,7h, a /Y/ - в регистр 10 40 через И 6,,...,6h, ИЛИ 8,,...8Ч.

На входы преобразователя 11 поступают коды / и ( Z,//8 с выходов регистра 9 и код Z4 /2 с выходов регистра 10. Образованная трехстрочная кодовая матрица R /Za//2 + 7/2,//8 преобразуется, как показано на фиг.2, до двухстрочной КМ, которая затем сумматором 13 преобразуется в однорядный код результата. На фиг. 2 точками обозначены двоичные разряды кодов соответствующего веса. Рамки окружают разряды, подаваемые на входы сумматоров.

ля, а третьи входы сумматоров, с первого по (п-З)-й, подключены соответ- с.твенно к разрядам, с третьго по (а-1)-й, второго входа преобразователя, n-й разряд которого подключен к третьему входу сумматоров, с (п-2)-го по (п+1)-й, выходы суммы сумматоров, кроме первого, подключены к первому выходу преобразователя, к второму выходу которого подключены выходы переноса сумматоров преобразователя, первый и второй выходы преобразователя многорядкого кода соединены соотчетст- венно с первым и вторым входами сумматора, отличающееся тем, что, с целью уменьшения аппаратурных затрат, оно содержит схему сравнения и коммутатор, причем шина инверсного кода первого аргумента и шина прямого кода второго аргумента подключены со-1 ответственно к первому и второму вхо дам схемы сравнения, шины прямого кода первого и второго аргументов соединены соответственно с первым и вторым информационными входами коммута- юра, первый и второй управляющие входы которого подключены соответственно к первому и второму выходам схемы сравнения, первый выход комму- дг татора подключен к первому входу блока выделения максимума и первому.входу преобразователя многорядного кода, второй и третий входы которого соединены соответственно с шиной второго выхода коммутатора со сдвигом на три разряда в сторону младших разрядов и шиной третьего выхода коммутатора со сдвигом на один разряд в сторону младших разрядов, выход сумматора

35

50

,Значения кодов fz(/ и R сравнива- 55 подключен к второму входу блока выде- ются в блоке 14, в результате чего на ления максимума, выход которого яв- выходе 17 образуется значение ляется выходом устройства.

4

22

X2 + Y2.

Разрядами первого входа преобразовате

ля, а третьи входы сумматоров, с первого по (п-З)-й, подключены соответ- с.твенно к разрядам, с третьго по (а-1)-й, второго входа преобразователя, n-й разряд которого подключен к третьему входу сумматоров, с (п-2)-го по (п+1)-й, выходы суммы сумматоров, кроме первого, подключены к первому выходу преобразователя, к второму выходу которого подключены выходы переноса сумматоров преобразователя, первый и второй выходы преобразователя многорядкого кода соединены соотчетст- венно с первым и вторым входами сумматора, отличающееся тем, что, с целью уменьшения аппаратурных затрат, оно содержит схему сравнения и коммутатор, причем шина инверсного кода первого аргумента и шина прямого кода второго аргумента подключены со-1 ответственно к первому и второму вхо дам схемы сравнения, шины прямого кода первого и второго аргументов соединены соответственно с первым и вторым информационными входами коммута- юра, первый и второй управляющие входы которого подключены соответственно к первому и второму выходам схемы сравнения, первый выход комму- татора подключен к первому входу блока выделения максимума и первому.входу преобразователя многорядного кода, второй и третий входы которого соединены соответственно с шиной второго выхода коммутатора со сдвигом на три разряда в сторону младших разрядов и шиной третьего выхода коммутатора со сдвигом на один разряд в сторону младших разрядов, выход сумматора

содержит с первой по четвертую группы элементов И, первую и вторую группы элементов ИЛИ по п двухвходовых элементов в каждой группе, первый и второй n-разрядные регистры, причем разрядные шины, с первом по n-ю, первого информационного входа коммутатора подключены к первым входам соответствующих элементов И первой и второй групп, разрядные шины, с. первой по n-ю, второго информационного входа коммутатора, подключены к первым входам соответствующих элементов И третьей и четвертой групп, первый управ- ляющий вход коммутатора соединен с вторыми входами элементов И первой и четвертой групп, втгрой управляющий вход коммутатора соединен с вторыми входами элементов И ВТОРОЙ и

третьей групп, пыходы элементов И первой п третьей групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ первой группы, выходы которых соединены с соответствующими входами первого n-разрядного регистра, прямые и инверсные выходы разрядов которого соединены соответственно с первым и вторым выходами коммутатора, выходы элементов И второй и четвертой групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых подключены к соответствующим входам второго n-разрядного регистра, прямые выходы разрядов которого подключены к третьему выходу коммутатора.

Фиг. 1

fxx/xx

0.

7|г,|/«

| Устройство для вычисления модуля вектора | 1987 |

|

SU1429112A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1559344A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-15—Публикация

1989-06-09—Подача