сумматора 9, происходит арифметическое сложение с относительным адресом, поступившим на первые входы сумматора 9. При этом по информации разрядов 10 .,.. 13, поступающей с второго выхода регистра 7 команд, где хранится двоичный код о количестве обрабатываемых разрядов элемента операнда в инверсном виде, под воздейстИзобретБние относится к вьиисли- тельной технике и предназначено для использования в электронных цифровых вычислительных и управляющих машинах, работаюш 1х с относительной адреса- , дней.

Целью изобретения является повышение быстродействия.

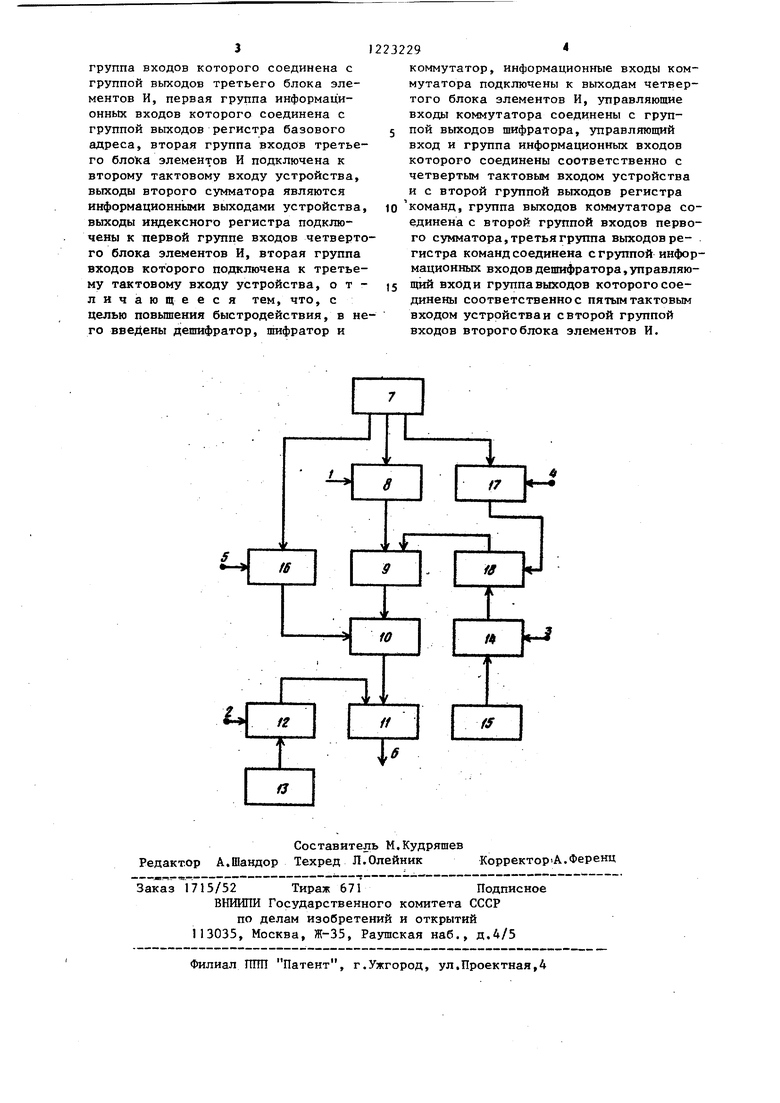

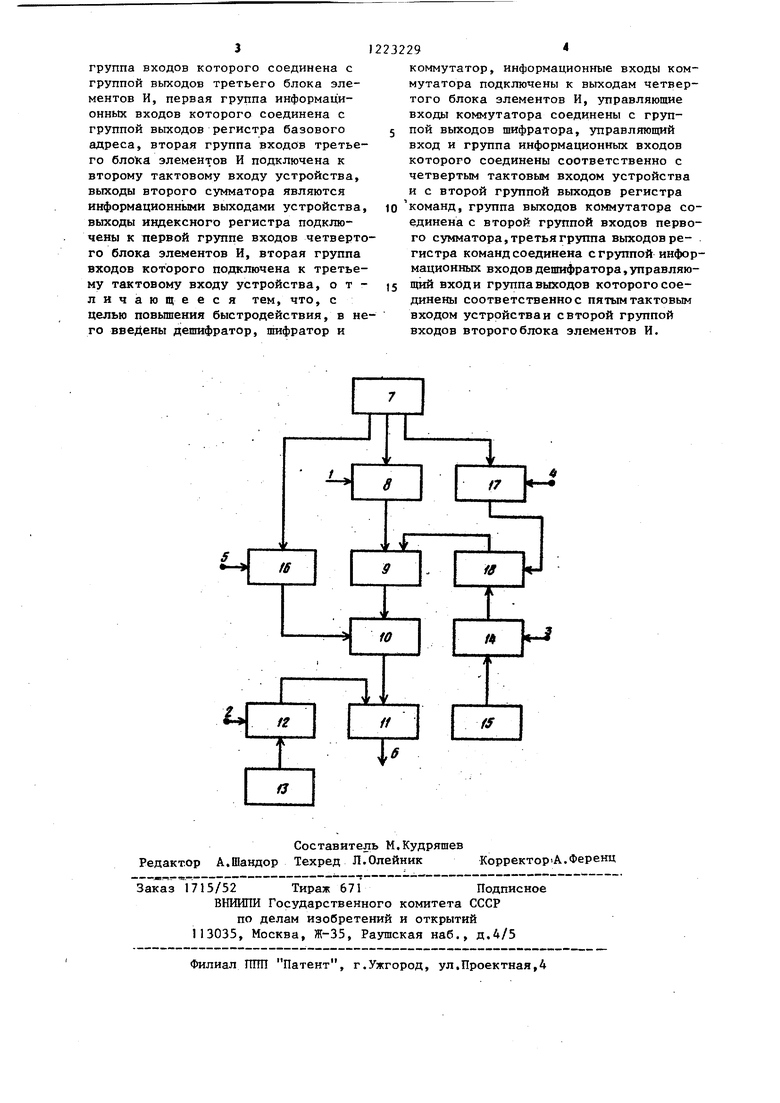

На чертеже представлена блок-схема устройства для формирования испол-. 10 вием управляющего сигнала, поступаю- нительньц: адресов.щего на пятый вход устройства, происСхема содержит тактовые входь 1-5 ходит формирование маски дешифрато- устройства, группу информационных вы- ром 16.

ходов 6 устройства, регистр 7 команд, Сформированная маска поступает с первый блок 8 элементов И, сумматор 9, is выходов дешифратора 16 на соответст- блок 10 элементов И, сумматор 11, блок 12 элементов И , регистр 13 базового адреса, блок 14 элементов И, индексный регистр 15, дешифратор 16, шифратор 17 и коммутатор 18.

Устройство работает следующим образом.

В регистре 7 хранится относительный адрес переменной длины до шест25

надцати разрядов для формирования исцолнительного адреса при относительной адресации. Для определения разрядности обрабатываемой информации элемента операнда, адрес которого формируется на выходе устройства, используются разряды с 10 по 13 регистра 7 команд, в которых записаи двоичный код о количестве обрабатываемых разрядов (КОР).

Под воздействием сигнала, поступающего на первый вход 1 устройства, блок 8 транслирует информацию относительного адреса из регистра 7 на соответствующие первые входы сумматора 9. Одновременно под воздействием сигнала, поступающего иа вход 3 устройства, блок 14 передает информацию из регистра 15 иа входы коммутатора 18, который производит сдвиг информации, определяющей номер обрабатьшаемого элемента операнда массива данных.

Двоичный код величины сдвига информации индексного регистра 15 появляется на выходах шифратора 17, ко ующие вторые входы блока 10 для окончательного формирования информации, поступающей с выходов сумматора 9. Маска накладьшается так, что на вы- 20 ходах блока 10 появляется результат арифметического сложения относительного адреса и вьщеленной части индексного регистра с учетом верхней границы маски.

Сформированный на сумматоре 9 адрес через блок 10 поступает на первые входы сумматора 11 для арифметического сложения с информацией регистра 13, информация которого при наличии сигнала, поступающего на вход 2 устройства, появляется на выходах блока 12 для подключения к вторым входам сумматора 11. На выходе последнего формируется исполнительный адрес устройства, по которому из операнда извлекается элемент, номер которого хранится в индексном регистре, а разрядность указана в регистре 7 команд.

Формула

30

35

40

4S

изобретения

Устройство для формирования исполнительных адресов, содержащее регистр команд, четыре блока элементов И, первый и второй сумматоры, регистр базового адреса и индексный регистр, при этом первая группа выходов регистра команд подключена к первой группе информационных входов первого блока элементов И, вторая

Устройство для формирования исполнительных адресов, содержащее регистр команд, четыре блока элемен тов И, первый и второй сумматоры, регистр базового адреса и индексный регистр, при этом первая группа выходов регистра команд подключена к первой группе информационных входов первого блока элементов И, вторая

торый формируется по содержимому раз- 50 группа входов которого соединена с

рядов 10 .... 13 регистра 7 команд и под воздействием сигнала, поступающего на вход 4 устройства. Согласно двоичному коду величины сдвига происходит сдвиг информации в сторону младших разрядов в коммутаторе 18. По информации, поступающей с выходов коммутатора 18 на вторые входы

первым тактовым входом устройства, выходы первого блока элементов И соединены с первой группой входов первого сумматора, выходы которого 55 подключены к первой группе входов второго блока элементов И, выходы которого подключены к первой группе входов второго сумматора, вторая

сумматора 9, происходит арифметическое сложение с относительным адресом, поступившим на первые входы сумматора 9. При этом по информации разрядов 10 .,.. 13, поступающей с второго выхода регистра 7 команд, где хранится двоичный код о количестве обрабатываемых разрядов элемента операнда в инверсном виде, под воздействием управляющего сигнала, поступаю- щего на пятый вход устройства, происСформированная маска поступает с выходов дешифратора 16 на соответст-

ующие вторые входы блока 10 для окончательного формирования информации, поступающей с выходов сумматора 9. Маска накладьшается так, что на вы- ходах блока 10 появляется результат арифметического сложения относительного адреса и вьщеленной части индексного регистра с учетом верхней границы маски.

Сформированный на сумматоре 9 адрес через блок 10 поступает на первые входы сумматора 11 для арифметического сложения с информацией регистра 13, информация которого при наличии сигнала, поступающего на вход 2 устройства, появляется на выходах блока 12 для подключения к вторым входам сумматора 11. На выходе последнего формируется исполнительный адрес устройства, по которому из операнда извлекается элемент, номер которого хранится в индексном регистре, а разрядность указана в регистре 7 команд.

Формула

изобретения

Устройство для формирования исполнительных адресов, содержащее регистр команд, четыре блока элементов И, первый и второй сумматоры, регистр базового адреса и индексный регистр, при этом первая группа выходов регистра команд подключена к первой группе информационных входов первого блока элементов И, вторая

группа входов которого соединена с

первым тактовым входом устройства, выходы первого блока элементов И соединены с первой группой входов первого сумматора, выходы которого подключены к первой группе входов второго блока элементов И, выходы которого подключены к первой группе входов второго сумматора, вторая

группа входов которого соединена с группой выходов третьего блока элементов И, первая группа информационных входов которого соединена с группой выходов регистра базового адреса, вторая группа входов третьего элементов И подключена к второму тактовому входу устройства, выходы второго сумматора являются информационн1з1ми выходами устройства, выходы индексного регистра подключены к первой группе входов четвертого блока элементов И, вторая группа входов которого подключена к третьему тактовому входу устройства, отличающееся тем, что, с целью повьшения быстродействия, в него введены дешифратор, шифратор и

23229

коммутатор, информационные входы коммутатора подключены к выходам четвертого блока элементов И, управляющие входы коммутатора соединены с груп- 5 пой выходов шифратора, управляющий вход и группа информационных входов которого соединены соответственно с четвертым тактовым входом устройства и с второй группой выходов регистра 10 команд, группа выходов коммутатора соединена с второй группой входов первого сумматора, третья группа выходов регистра команд соединена с группой информационных входов дешифратора,управляю- )5 щий входи группа выходов которого соединены соответственное пятым тактовым входом устройства и с второй группой входов второго блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования исполнительных адресов | 1989 |

|

SU1837285A1 |

| Устройство для формирования исполнительных адресов | 1985 |

|

SU1298745A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования исполнительных адресов | 1980 |

|

SU888121A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

Изобретение относится к вычислительной технике. Цель изобретения повышение быстродействия устройства, Устройство содержит регистр команд, первый - четвертый блоки элементов И, первый и второй сумматоры, регистр базового адреса и индексный регистр. Новым в устройстве является введение дешифратора, шифратора и коммутатора с соответствующими связями. В устройстве маска накладьтается так, что на выходах блока элементов И появляется результат арифметического сложения относительного адреса и вьщеленной части индексного регистра с учетом верхней границы маски. На выходе сумматора формируется исполнительный адрес, по которому из операнда извлекается элемент, номер ;которого хранится в индексном регистре, а разрядность указана в регистре команд. кл. i (Л

Составитель М.Кудряшев Редактор А.Шандор Техред Л.Олейник Корректор А.Ференц

Заказ 1715/52 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ПШ1 Патент, г.Ужгород, ул.Проектная,4

| Устройство для поиска операндов | 1974 |

|

SU506856A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР 431516, кл | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-04—Подача