адреса к соответствующим вторым групповым входам второго слагаемого второго сумматора 5.

Регистр 7 базового адреса предназначен для хранения базового адреса массива данных при относительной адресации с обоими типами индексации. Регистр 7 базового адреса выполнен на ИМС 155ТМ5 (справочник Интегральные микросхемы под редакцией Б.В.Тарабрина. М., Радио и связь, 1984, с.528, с.64). Шестнадцатиразрядный регистр 7 базового адреса состоит из четырех ИМС 155ТМ5. Информационные входы регистра 7 базового адреса РБА F... РВА 0 подключены к входу 15 базового адреса устройства. Выходы регистра 7 базового адреса подключены к соответствующим первым входам 47.1...47.16 (РБА F ... РБА 0) двухвходовых элементов 2И третьего блока 6 элементов И.

Четвертый блок 8 элементов И предназначен для подключения шестнадцатиразрядного сформированного индекса из индексного регистра 9 к первым групповым входам первого коммутатора 12.

Индексный регистр 9 предназначен для хранения номерэ операнда массива данных при значениях КОР, равного 1, 2, 4, 8 или 16 (0), которые относятся к.операнду при относительной адресации со сдвинутой индекса- цией, или индекса адреса операнда массива данных для всех значений КОР от 0 до 15 и УН Г от 0 до Fie, которые относятся к индексному регистру при относительной адресации с выделенной индексацией. Номер элемента операнда или индекс могут содержать от одного до шестнадцати разрядов, поэтому индексный регистр 9 состоит из четырех ИМС 155ТМ5 с соответствующими номерами выводов разрядов (справочник Интегральные микросхемы под ред. Б.В.Тарабрина. М., Радио и связь, 1984, с.528, с.64). Информационные входы индексного регистра 9 (ИР F.,. ИР OD подключены к входу 16 номера элемента операнда или индекса устройства.

Блок 10 дешифрации предназначен для выделения и управления дальнейшей трансляцией результата арифметического сложения относительного адреса из регистра 1 команд и сдвинутой информации индексного регистра 9 в зависимости от типа индексации при помощи управления работой двухвходовых элементов 2 И второго блока 4 элементов И,

Шифратор 11 предназначен для фооми- рования двоичного кода величины циклического сдвига информации из индексного регистра 9. Исходной информацией является содержимое разрядов РК 13... КР 10 регистра 1 команд, где хранится прямой двоичный код КОР. Информация поступает из второй группы выходов регистра 1 команд. Для значений КОР, равных 1, 2, 4, 8 или 16 (0), от относительной адресации со сдвинутой индексацией шифратор осуществляет формирование величины сдвига (ВСД) согласно формуле

ВСД log

16

2 КОР

(1.1),

где КОР - количество обрабатываемых разрядов элемента операнда.

КОР может принимать значения 1, 2, 4, 8 или 16 (0), а при этом ВСД - соответственно 4, 3, 2, 1,0.

Первый коммутатор 12 является элементом сдвига, предназначенным для циклического сдвига вправо до шестнадцати разрядов при различных типах индексации. При относительной адресации со сдвинутой индексацией необходим сдвиг до четырех разрядов в зависимости от значений КОР,

равным t, 2, 4, 8 или 16 (0). При относительной адресации с выделенной индексацией, которая определяется наличием сигнала на входе 22 типа индексации устройства, возможен сдвиг до пятнадцати разрядов в

зависимости от значения УНГ для содержимого индексного регистра 9, величина которого определяется по следующей формуле:

ВСД УНГ .(1.2)

Таким образом, для индексного регистра с разрядностью, равной 16, необходим циклический сдвиг до пятнадцати разрядов (при сдвиге на шестнадцать разрядов

информация возвращается в исходное состояние). Так как стандартный ИМС, осуще- ствляющих комбинационно данный циклический сдвиг в сторону младших разрядов, не существует, первый коммутатор

12 выполнен на базе двухразрядных коммутаторов - мультиплексоров (ИМС 155КП2, справочник Интегральные микросхемы под ред. Б.В.Тарабрина, М., Радио и связь, Т984,,с.528, с.69).

Второй коммутатор 13 предназначен для коммутации двоичного кода величины сдвига (ВСД) либо от шифратора 11 при относительной адресации со сдвинутой индексацией, либо от регистра 1 команд,

разряды РК 17 ... РК 14, где хранится двоичный код УНГ, при относительной адресации с выделенной индексацией. Второй коммутатор 13 реализован на базе четырехразрядного коммутатора (ИМС К531КП11, справочник Популярные цифровые микросхемы под ред. В.Л.Шило, М., Металлургия, 1988, с.352, с. 147). Второй коммутатор 13 имеет две группы информационных входов, два управляющих входа, четырехразрядный выход величины сдвига (ВСД 3... ВСД 0), Первый управляющий вход (5) второго коммутатора 13 подключен к входу 22 типа индексации устройства, который управляет подключением информации с группы входов В коммутатора на выходданного коммутатора для относительной адресации с выделенной индексацией. В исходном состоянии, при отсутствии сигнала на входе 22 типа индексации, информация с группы входов А коммутатора постоянно подключена на выход данного коммутатора для относительной адресации со сдвинутой индексацией, и подключается к управляющим входам первого коммутатора 12 при наличии сигнала на тактовом входе 20 устройства в шифраторе 11.

Таким образом, для относительной адресации со сдвинутой индексацией необходимо присутствие сигнала на тактовом входе 20 устройства, а для относительной адресации с выделенной индексацией необходимо присутствие сигнала на входе 22 типа индексации устройства.

Предлагаемое устройство работает следующим образом,

В разрядах F... 0 регистра 1 команд хранится относительный адрес переменной длины до шестнадцати разрядов для формирования исполнительного адреса при относительной адресации со сдвинутой или выделенной индексацией. Для определения разрядности обрабатываемой информации элемента операнда, адрес которого формируется на выходе устройства, или разрядности индексного регистра с относительным адресом, которые участвуют в формировании адреса операнда на выходе устройства в зависимости от типа индексации, используются разряды с 10 по 13 регистра 1 команд, в которых записан прямой и обратный двоичный код количества обрабатываемых разрядов (КОР).

В случае, когда отсутствует сигнал на входе 22 типа индексации устройства и присутствует сигнал на четвертом тактовом входе 20 устройства , а КОР принимает значения 1, 2,4, 8 или 16(0), осуществляется сдвиг информации в сторону младших разрядов на первом коммутаторе 12 согласно двоичного кода величины сдвига, сформированного согласно формуле (1.1):

ВСД - Iog2 у||р(1.1)

для относительной адресации со сдвинутой индексацией. В случае, когда присутствует

сигнал на входе 22 типа индексации, осуществляется сдвиг информации в сторону младших разрядов на первом коммутаторе 12 согласно двоичного кода величины сдви- 5 . га, сформированного по формуле (1.2):

30

ВСД-УНГ

(1.2)

для относительной адресации с выделенной

10 индексацией, а ВСД для сдвинутой индексации при этом отключается. Сдвиг информации из индексного регистра 9 в сторону младших разрядов при относительной адресации с выделенной индексацией необхо15 дим для того, чтобы при арифметическом сложении выделенного индекса с относительным адресом устройства сумма формировалась, начиная с самого младшего разряда, Далее происходит арифметиче20 ское сложение информации, поступающей с выходов первого коммутатора 12 на вторые групповые входы второго слагаемого первого сумматора 3, с относительным адресом, поступившем на первые групповые входы

25 первого слагаемого этих сумматоров. При этом для относительной адресации со сдвинутой индексацией по информации инверсных разрядов РК 10 ... РК 13, поступающей из третьей группы выходов регистра 1 команд, где хранится обратный код количества обрабатываемых разрядов, на информационные входы блока 10 дешифрации под воздействием тактового сигнала, поступающего на пятый тактовый вход 21

35 устройства и вход блока 10 дешифрации, происходит формирование маски, верхняя граница (ВГ) которой определяется по следующей формуле:

40

ВГ 16-ВСД где ВСД - log

(1.3),

для относительной

адресации со сдвинутой индексацией, при 45 этом ВГ определяет номер старшего разряда, а нижняя граница маски ограничена младшим разрядом.

Сформированная маска поступает с ви- 50 хода блока 10 дешифрации на соответстсу- юидое входы второго блока 4 элементов И для управления дальнейшей трансляцией информации с целью окончательного формирования результата сложения, поступаю- 55 щего с выходов первого сумматора 3 на входы блока 4 элементов И. Маска накладывается так, что на -выходах второго блока 4 элементов И появляется результат арифметического сложения относительного адреса и сдвинутой части информации из индексносигнал на входе 22 типа индексации, осуществляется сдвиг информации в сторону младших разрядов на первом коммутаторе 12 согласно двоичного кода величины сдви- . га, сформированного по формуле (1.2):

ВСД-УНГ

(1.2)

для относительной адресации с выделенной

индексацией, а ВСД для сдвинутой индексации при этом отключается. Сдвиг информации из индексного регистра 9 в сторону младших разрядов при относительной адресации с выделенной индексацией необходим для того, чтобы при арифметическом сложении выделенного индекса с относительным адресом устройства сумма формировалась, начиная с самого младшего разряда, Далее происходит арифметическое сложение информации, поступающей с выходов первого коммутатора 12 на вторые групповые входы второго слагаемого первого сумматора 3, с относительным адресом, поступившем на первые групповые входы

первого слагаемого этих сумматоров. При этом для относительной адресации со сдвинутой индексацией по информации инверсных разрядов РК 10 ... РК 13, поступающей из третьей группы выходов регистра 1 команд, где хранится обратный код количества обрабатываемых разрядов, на информационные входы блока 10 дешифрации под воздействием тактового сигнала, поступающего на пятый тактовый вход 21

устройства и вход блока 10 дешифрации, происходит формирование маски, верхняя граница (ВГ) которой определяется по следующей формуле:

ВГ 16-ВСД где ВСД - log

(1.3),

для относительной

rb регистра 9 с учетом верхней границы маски.

I Для относительной адресации с выде- индексацией по информации инвер- сных разрядов РК 1.0 ... РК 13, поступающей с третьей группы выходов peri/ стра 1 команд, где хранится обратный код КОР, на пятый-восьмой входы второй группы входов (В) блока 10 дешифрации под действием .управляющего сигнала, поступающего на вход 22 типа индексации устройства, вход блока 10 дешифрации, происходит формирование маски, верхняя граница (номер старшего разряда) которой определяется по следующей формуле:

ВГ КОР,

(1.4)

при этом нижняя граница маски ограничена самым младшим разрядом после сдвига на величину

8СД УНГ.

| При этом под воздействием управляющего сигнала, поступающего на вход 22 ти- п(1 индексации устройства и вход блока 10 дешифрации, происходит отключение ин- ф зрмации, которая используется при относительной адресации со сдвинутой индексацией. Сформированный на выходах первого сумматора 3 адрес через второй блок 4 элементов И поступает на первые групповые входы первого слагаемого второ- гс сумматора 5 для арифметического сложения с базовым адресом массива данных из регистра 13 базового адреса, информация которого при наличии тактового сигнала, пост упающего на второй тактовый вход 18 устройства и входы третьего блока 6 э/ементов И, появляется на выходах этих э/ ементов для подключения к вторым групповым входам второго слагаемого второго сумматора 5. На выходе второго сумматора 5 формируется исполнительный адрес устройства.

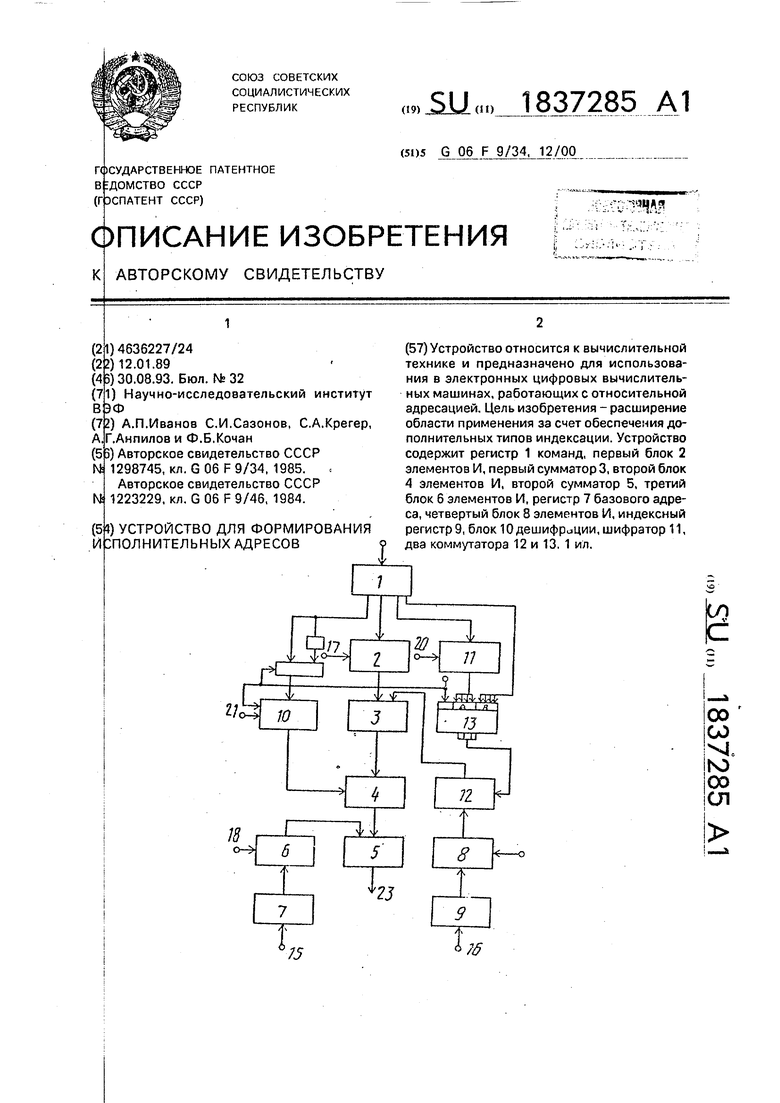

I Формула изобретения „ i Устройство для формирования исполнительных адресов, содержащее регистр ко- .минд, блок дешифрации, четыре блока элементов И, два сумматора, шифратор, регистр базового адреса, индексный регистр и первый коммутатор, причем информационный вход регистра команд является входом команды устройства, первый выход регистра команды устройства, первый выход регистра команд соединен с информационным входом блока дешифрации, второй выход регистра команд соединен с первым входом первого блока элементов И, выход которого

соединен с первым входом первого сумматора, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с первым входом второго сумматора, второй вход которого соединен

с выходом третьего блока элементов И, первый вход которого соединен с выходом регистра базового адреса, информационный вход которого является входом базового адреса устройства, выход которого подключен

к выходу второго сумматора, третий выход регистра команд соединен с информационным входом шифратора, вход индекса устройства соединен с информационным входом индексного регистра, выход которого соединен с первым входом четвертого блока элементов И, выход которого соединен с информационным входом первого коммутатора, выход которого соединен с вторым входом сумматора, с первого по пятый тактовые входы устройства подключены соответственно к вторым входам первого, третьего и четвертого блоков элементов И, к управляющему входу шифратора и к первому управляющему входу блока дешифрации, выход которого соединен с вторым входом второго блока элементов И, о т л и - чающееся тем, что, с целью расширения области применения за счет обеспечения дополнительных типов индексации, оно дополнительно содержит второй коммутатор, выход которого соединен с управляющим входом первого коммутатора, первый и второй информационные входы второго коммутатора подключены соответственно к

выходу шифратора и четгертому выходу регистра команд, управляющий вход второго коммутатора соединен с вторым управляющим входом блока дешифрации и является входом задания типа индексации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования исполнительных адресов | 1985 |

|

SU1298745A2 |

| Устройство для формирования исполнительных адресов | 1984 |

|

SU1223229A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для управления буфер-НОй пАМяТью | 1979 |

|

SU840903A1 |

| Устройство для формирования исполнительных адресов | 1980 |

|

SU888121A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

Авторы

Даты

1993-08-30—Публикация

1989-01-12—Подача