Изобретение относится к области вычислительной техники и используется для управления доступом к полю общей памяти двух процессоров вычислительной системы.

Цель изобретения - повышение надежности устройства за счет предотвращения вероятности ложного сраба- тьшания.

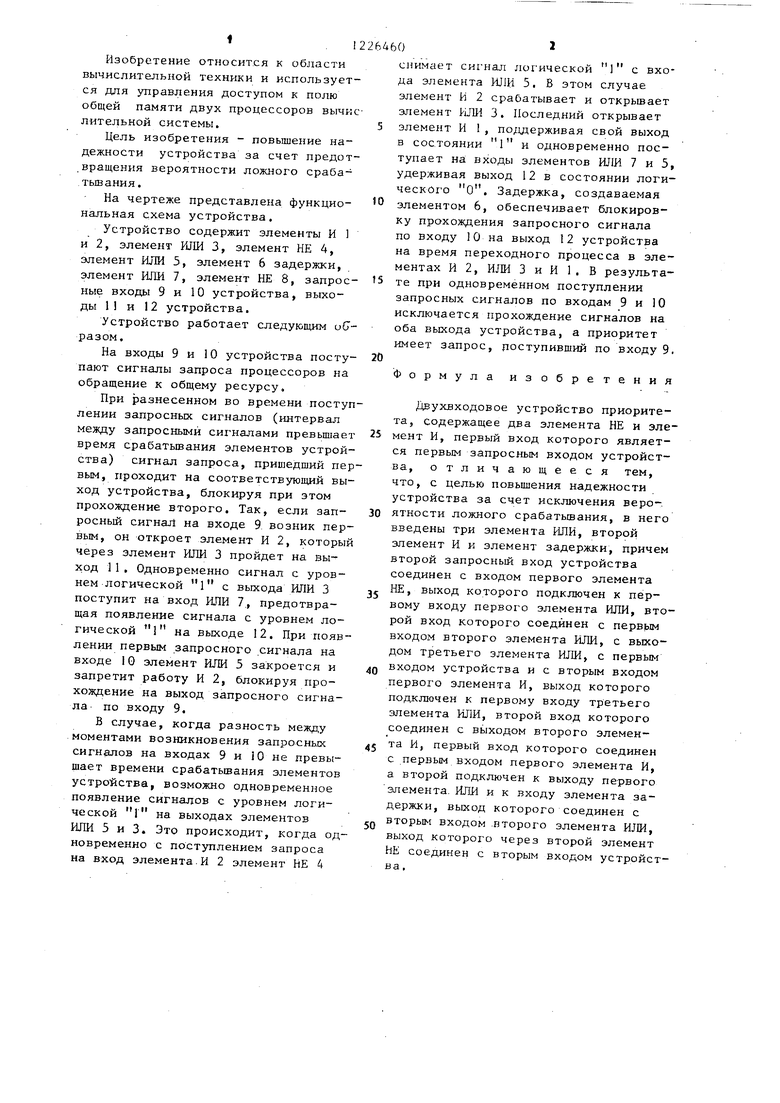

На чертеже представлена функциональная схема устройства.

Устройство содержит элементы И 1 и 2, элемент ИЛИ 3, элемент НЕ 4, элемент ИЛИ 5, элемент 6 задержки, элемент ИЛИ 7, элемент НЕ 8, запросные входы 9 и 10 устройства, выходы 1 и 12 устройства.

Устройство работает следующим оСГ- разом.

На входы 9 и 10 устройства поступают сигналы запроса процессоров на обращение к общему ресурсу.

При разнесенном во времени поступлении запросных сигналов (интервал между запросными сигналами превышает время срабатьшания элементов устройства) сигнал запроса, пришедший первым, проходит на соответствующий выход устройства, блокируя при этом прохождение второго. Так, если запросный сигнал на входе 9 возник первым, он откроет элемент И 2, который через элемент ИЛИ 3 пройдет на выход 11 . Одновременно сигнал с уровнем логической 1 с выхода ИЛИ 3 поступит на вход ИЛИ 7., предотвращая появление сигнала с уровнем логической 1 на выходе 12. При появлении первым запросного сигнала на входе 10 элемент ИЛИ 5 закроется и запретит работу И 2, блокируя прохождение на выход запросного сигнала- по входу 9.

В случае, когда разность между моментами возникновения запросных сигналов на входах 9 и 10 не превышает времени срабатьшания элементов устройства, возможно одновременное появление сигналов с уровнем логической 1 на выходах элементов ИЛИ 5 и 3. Это происходит, когда одновременно с поступлением запроса на вход элемента.И 2 элемент НЕ 4

S

0

5

0

5

0

5

50

снимает сигнал логической 1 с входа элемента ШЩ 5. В этом случае элемент И 2 срабатывает и открьшает элемент ИЛИ 3. Последний открывает элемент И 1 , по; держивая свой выход в состоянии 1 и одновременно поступает на: входы элементов ИЛИ 7 и 5, удерживая выход 12 в состоянии логического О. Задержка, создаваемая элементом 6, обеспечивает блокировку прохождения запросного сигнала по входу 1 о на выход 12 устройства на время переходного процесса в элементах И 2, ШШ 3 и И 1 . В результате при одновременном поступлении запросных сигналов по входам 9 и 10 исключается прохождение сигналов на оба выхода устройства, а приоритет имеет запрос, поступивший по входу 9,

Формула изобретения

Двухвходовое устройство приоритета, содержащее два элемента НЕ и элемент И, первый вход которого является первым запросным входом устройства, отличающееся тем, что, с целью повышения надежности устройства за счет исключения веро-. ятности ложного срабатьшания, в него введены три элемента ИЛИ, второй элемент И и элемент задержки, причем второй запросный вход устройства соединен с входом первого элемента НЕ, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с первь1м входом второго элемента ИЛИ, с выходом третьего элемента ИЛИ, с первым входом устройства и с вторым входом первого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым,входом первого элемента И, а второй подключен к выходу первого элемента. ИЛИ и к входу элемента задержки, выход которого соединен с вторым входом .второго элемента ИЛИ, выход которого через второй элемент НЕ соединен с вторым входом устройства ,

;;

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухвходовое устройство приоритета | 1984 |

|

SU1269132A1 |

| АРБИТР СИГНАЛОВ | 1991 |

|

RU2032935C1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1578712A1 |

| Двухвходовое устройство приоритета | 1987 |

|

SU1495798A2 |

| Устройство для обслуживания запросов | 1985 |

|

SU1251079A1 |

| Многоканальное устройство для управления очередностью обработки запросов | 1978 |

|

SU744573A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1709312A1 |

| Устройство управления прерываниями | 1982 |

|

SU1242948A1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| Многоканальное устройство переменного приоритета | 1983 |

|

SU1120332A1 |

Изобретение относится к вычислительной технике. Цель изобретения- повышение надежности устройства. Для достижения цели в него введены три элемента ИЛИ, элемент И и элемент задержки, соединенные с остальными узлами- устройства в соответствии с решаемой задачей. Устройство может быть использовано для управления доступом к полю общей памяти двух процессоров вычислительной системы, при этом устройство может предотвращать вероятность ложного срабатьшания. 1 Ш1 . (Л С

| Двухвходовое устройство приоритета | 1978 |

|

SU807296A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двухвходовое устройство приоритета | 1982 |

|

SU1059574A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-08-25—Подача