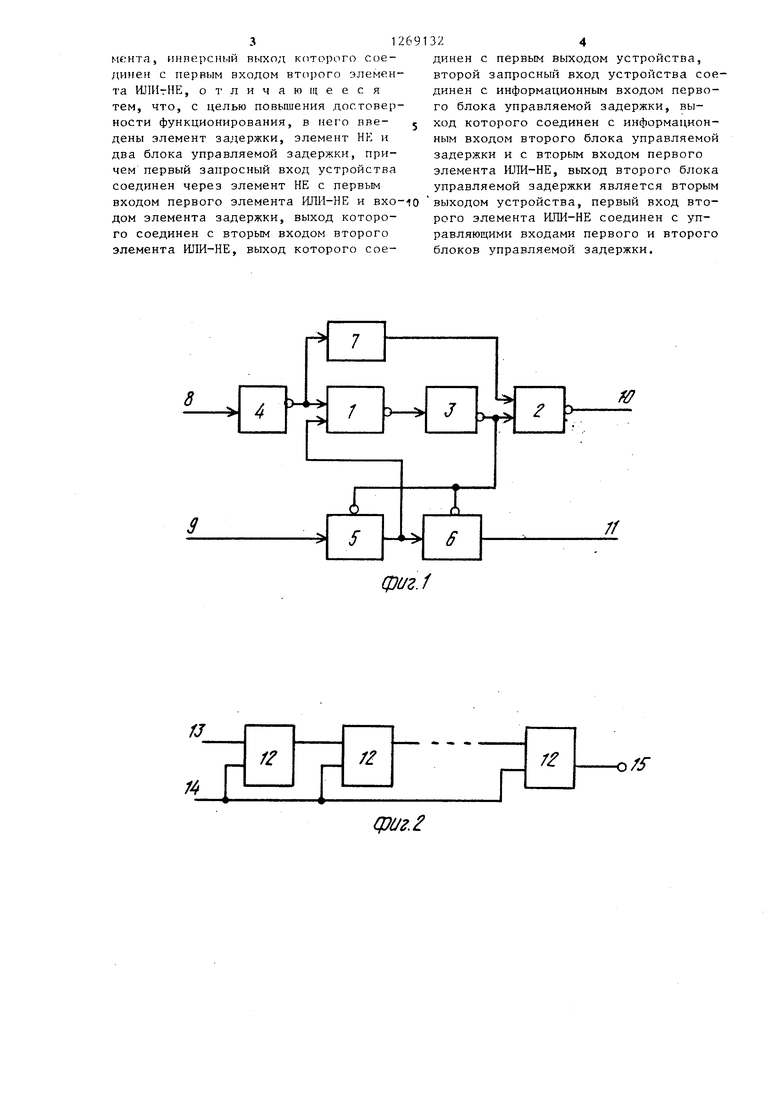

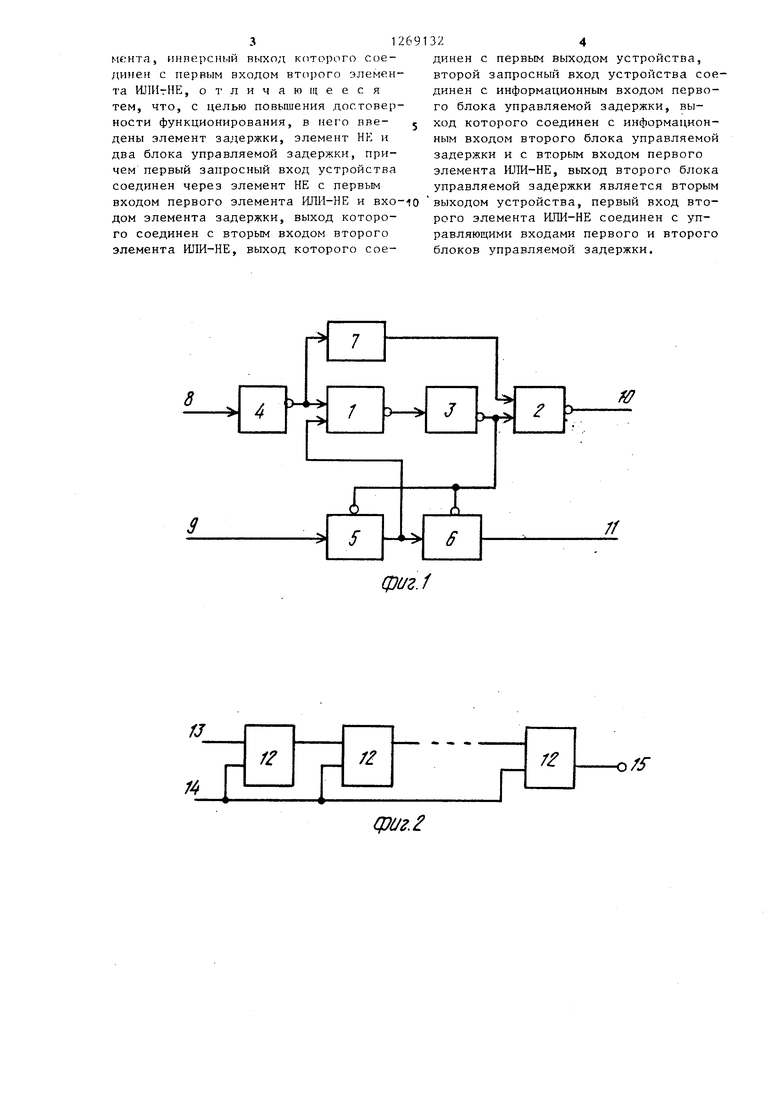

Изобретение относится к вычислительной технике и может быть использовано для управления доступом к общему ресурсу двух активных устройств вычислительной системы, например процессоров. Цель изобретения - повышение достоверности функционирования устройства. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 схема блока управляемой задержки. Устройство содержит элементы ИЛИНЕ 1 и 2,пороговый элемент (триггер Шмидта) 3, элемент НЕ 4, блоки 5- и 6 управляемой задержки, элемент 7 задержки, входы 8 и 9, выходы 10 и 11.Блоки 5 и 6 содержат элементы И 12, информационный вход, 13, управляющий вход 14, выход 15. Устройство работает следующим образом. Сигналы запросов поступают на входы 8 и 9 устройства в виде уровней логической 1. Поступление логической 1 на вход 8 приводит к появлению на выходе элемента НЕ 4 логического О, который поступает на входы элемента 7 задержки и элемента ШШ-НЕ 1. На выходе последнего образуется сигнал логической 1, вызывающий срабатывание порогового элемента 3, на инвертирующем внгходе которого формируется сигнал с уровнем логического О, далее преобразуемый с помощью элемента ИЖ-НЕ 2 в единичное значение сигнала запрос на выходе 10 устройства. Одновремен с выхода порогового элемента 3 нуле вой сигнал поступает на управляющие входы блоков 5 и 6 управляемой заде ки, что приводит к запрету прохожде ния через них сигнала запроса с вхо да 9 устройства на выход 11. При поступлении запросного сигна ла только на вход 9 устройства он проходит через блоки 5 и 6 управляе мой задержки на выход 11, так как н их управляющие входы с выхода порогового элемента 3 поступает логичес кая единица. Одновременно с выхода блока 5 управляемой задержки сигнал с уровнем 1 поступает на вход элемента И1Б1-НЕ 2, запрещая прохождение сигнала запроса с входа 8 уст ройства на выход 10. Рассмотрим режим соревнования, возникающий, когда интервал между поступлением запросов ио входам 8 и 9 соизмерим с временем срабатывания элементов. В этом случае возможна ситуация,, когда сигналы на входах элемента ИЛИ-НЕ 1 почти одновременно меняются на противоположные, в результате чего на его выходе формируется короткий импульс с уровнем логической 1 либо с уровнем, не достигшим полного уровня 1. Если этот импульс не приводит к срабатыванию порогового элемента 3, выход элемента ИЛИ-НЕ 1 остается в состоянии О, запросный сигнал с входа 9 через блок 6 проходит на выход 11, а прохождение сигнала с входа 8на выход 10 блокируется уровнем 1, поступающим на элемент ИЛИ-НЕ 1 с выхода блока 5„ В случае, если импульс на выходе элемента ИЛИ-НЕ 1 вызывает появление импульса на выходе порогового элемента 3, блоки 5 и 6 сбрасываются до того,как успеет возникнуть сиг- i нал на выходе 11. 1хлок 5 снимает единичный уровень с входа элемента ШШ-НЕ 1, на выходе которого формируется единичный сигнал, вызывающий появление сигнала на выходе 10 устройства. Прохождение сигнала с входа 9на выход 11 блокируется нулевым уровнем, действующим с выхода порогового элемента 3. ,Для надежной работы устройства величина задержки блоков 5 и 6 и элемента 7 должна быть не менее максимального суммарного времени срабатывания элемента ИЛИ-НЕ 1 и порогового элемента 3. Пример реализации блоков 5 и 6 управляемой задержки в виде цепочки элементов И показан на фиг. 2. Сиг- нал с информационного входа 13 проходит на выход 15 через суммарное воёмя срабатывания всех элементов И 12 при наличии сигнала на управляющем входе 14. Если в процессе прохождения сигнала на управляющем входе 14 появляется нулевой сигнал, то про.- хождение сигнала через элементы И 12 прекращается. Формула изобретения Двухвходовое устройство приорите д. содержащее первый и второй элементы ИЛИ-НЕ, пороговый, элемент, причем выход первого элемента ИЛИНЕ соединен с входом порогового эле312691

Mf-нта, ннпйрсный выход которого соединен с первым входом второго элемента ИЛНтНЕ, отличающееся тем, что, с целью повьаиения достоверности функционирования, в него вве- j дены элемент задержки, элемент НЕ и два блока управляемой задержки, причем первый запросный вход устройства соединен через элемент НЕ с первым входом первого элемента ИЛИ-НЕ и вхо-ю дом элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ, выход которого сое324

динен с первым вьпсодом устройства, второй запросный вход устройства соединен с информационным входом первого блока управляемой задержки, выход которого соединен с информационным входом второго блока управляемой задержки и с вторым входом первого элемента Ш1И-НЕ, выход второго блока управляемой задержки является вторым выходом устройства, первый вход второго элемента ИЛИ-НЕ соединен с управляющими входами первого и второго блоков управляемой задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухвходовое устройство приоритета | 1987 |

|

SU1495798A2 |

| Двухвходовое устройство приоритета | 1988 |

|

SU1589276A1 |

| АРБИТР СИГНАЛОВ | 1991 |

|

RU2032935C1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1141412A1 |

| Многоканальное устройство переменного приоритета | 1985 |

|

SU1282130A1 |

| Устройство для обслуживания запросов | 1979 |

|

SU864288A1 |

| Устройство сопряжения процессора с внешними устройствами | 1987 |

|

SU1509893A1 |

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

| Приоритетное устройство | 1987 |

|

SU1462313A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

Изобретение предназначено для применения в вычислительных системах при организации доступа двух процессоров к общему ресурсу. Целью изобретения является повьпиение достоверности функционирования. Устройство содержит два элемента ШШ-НЕ, элемент задержки, элемент НЕ, триггер Шмидта и два блока управляемой задержки. Применение последних позволяет обеспечить устойчивую работу устройства при разрешении конфликтных ситуаций независимо от параметS ров используемых элементов. 2 ил. сл

| Блок приоритета | 1983 |

|

SU1091162A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Варшавский В.И | |||

| и Кишеневский М.А Аномальное поведение логических схем и проблема арбитража | |||

| - Автоматика и телемеханика, 1982, № 1, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| За. | |||

Авторы

Даты

1986-11-07—Публикация

1984-09-01—Подача