Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных системах.

Цель изобретения - повышение быстродействия за счет параллельной настройки каналов с помощью многоразрядных настроечных кодов.

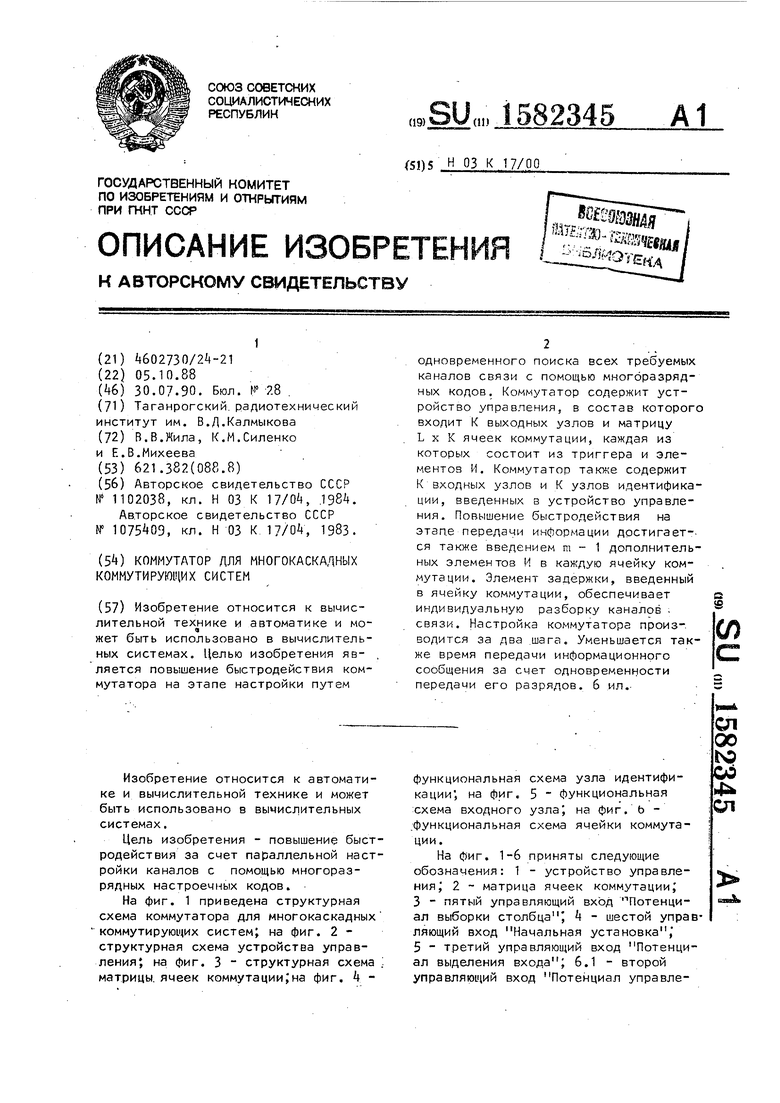

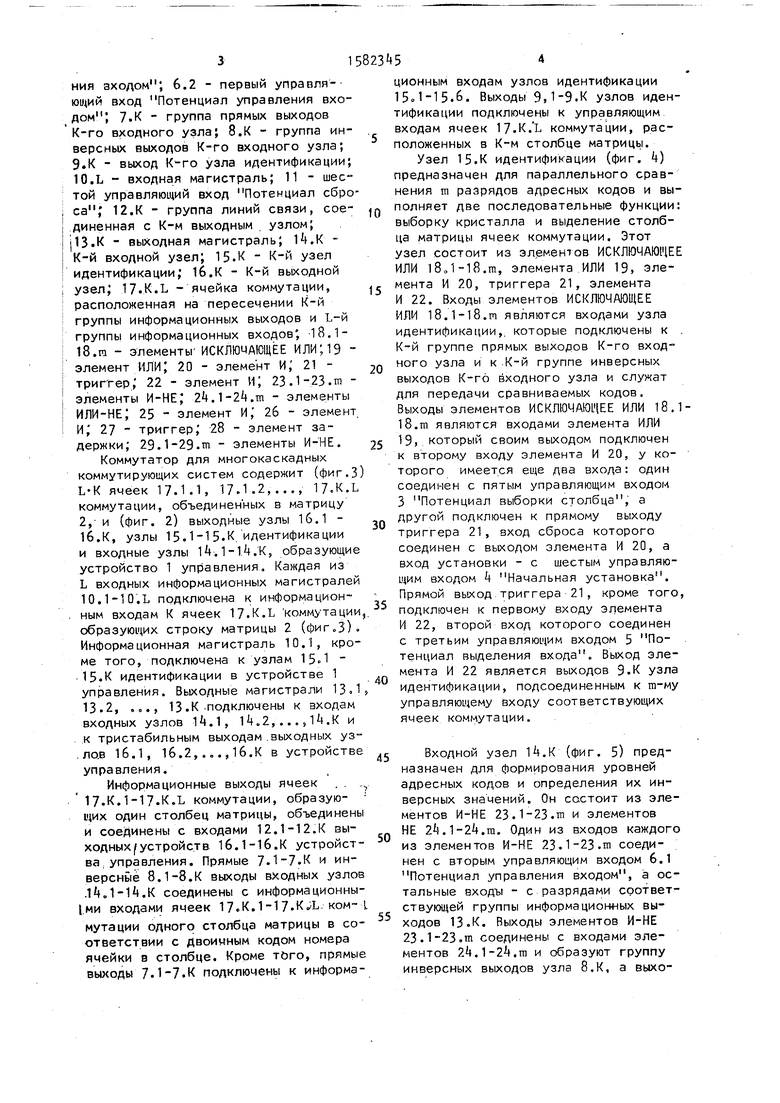

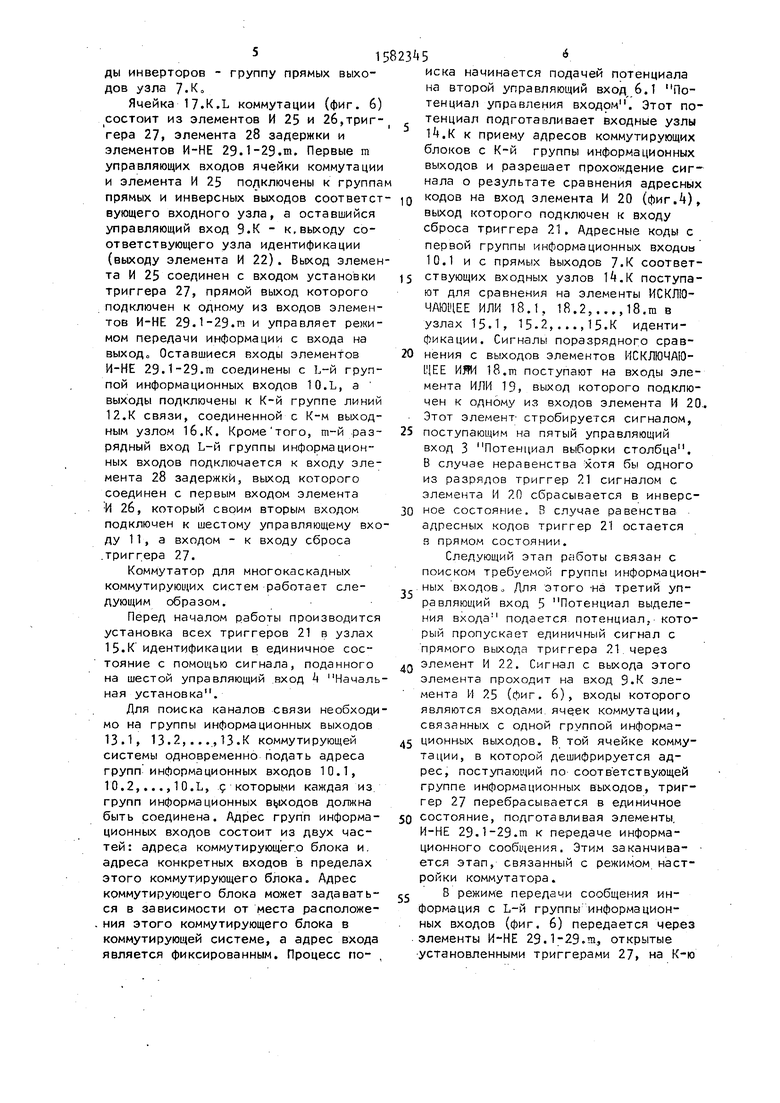

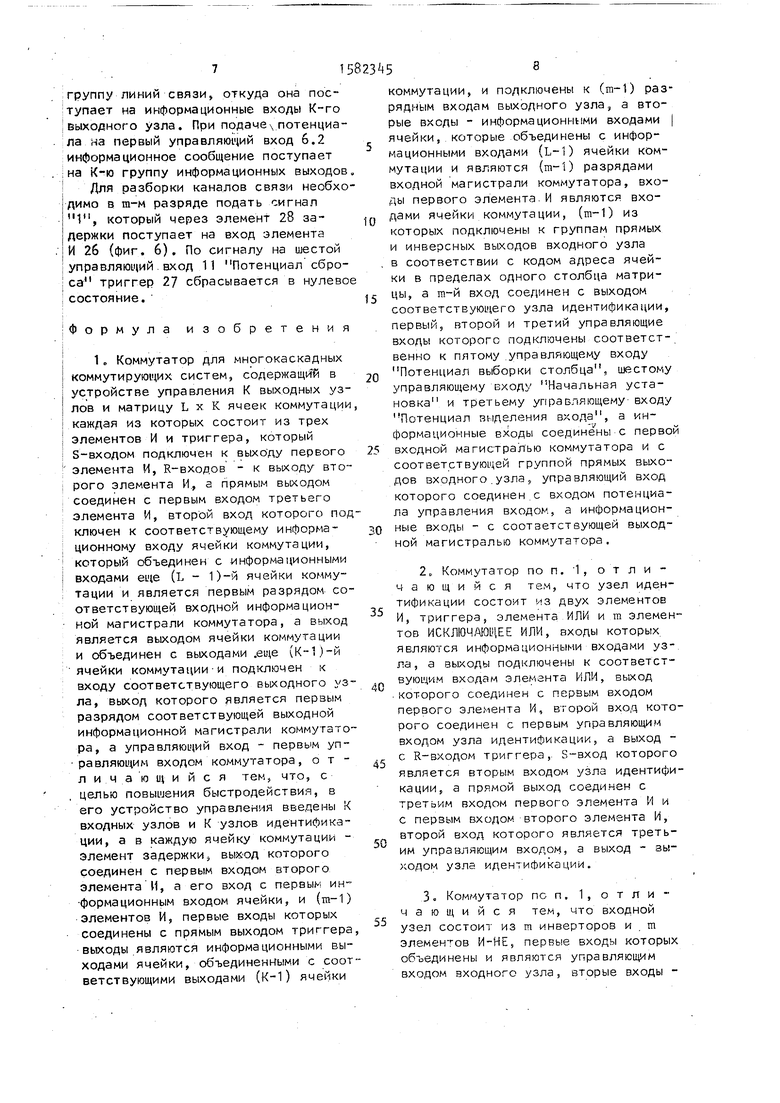

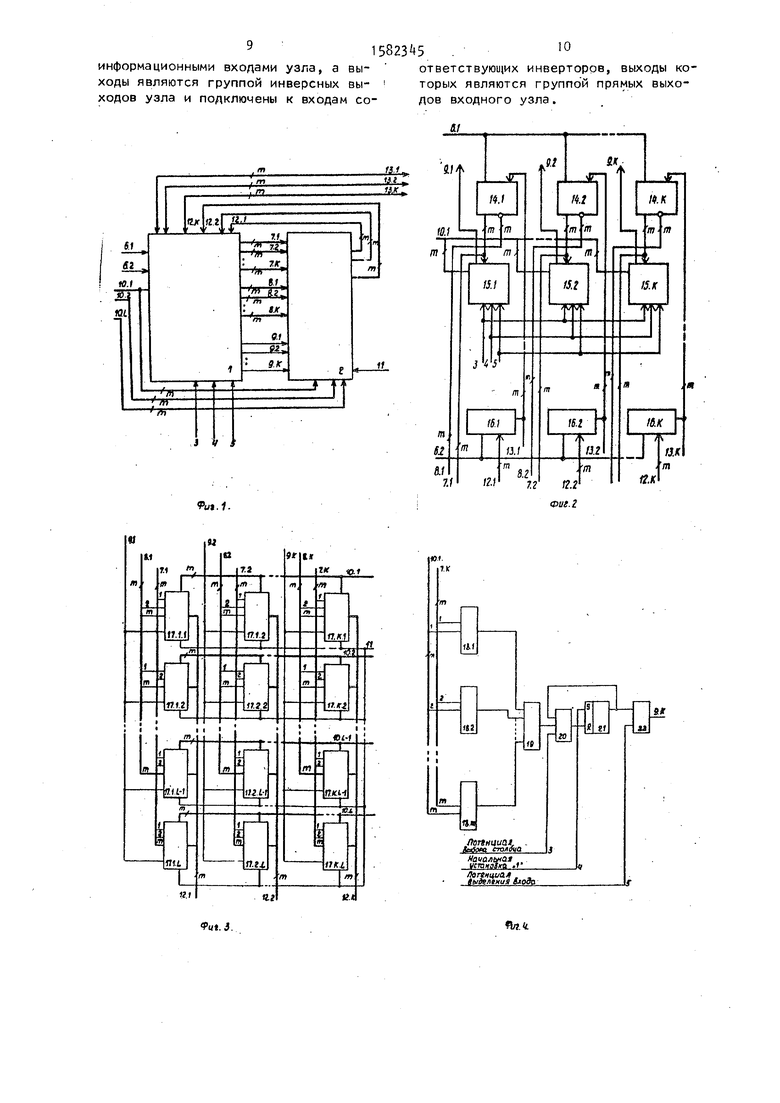

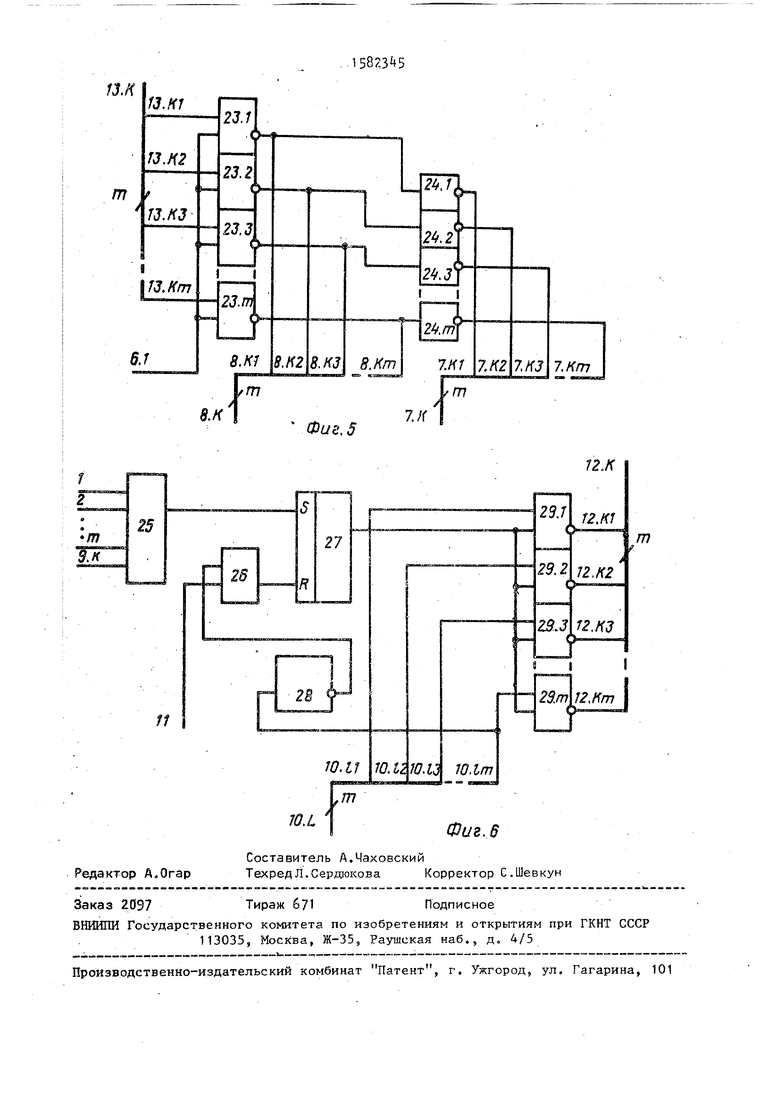

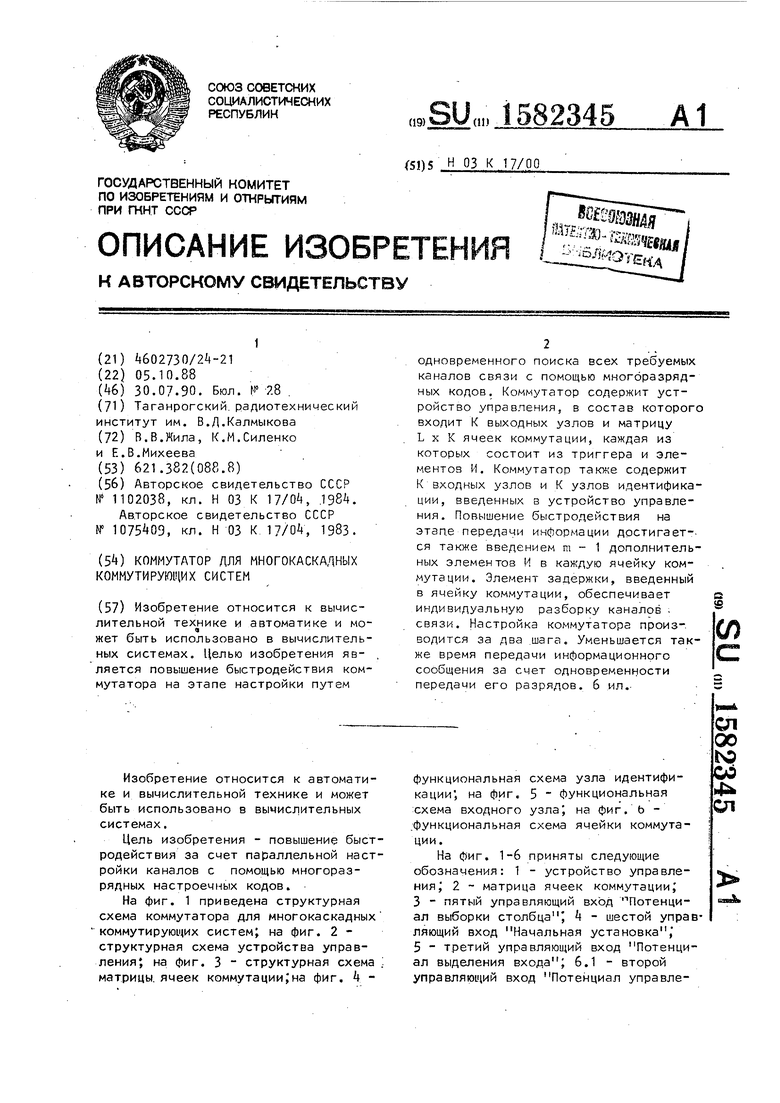

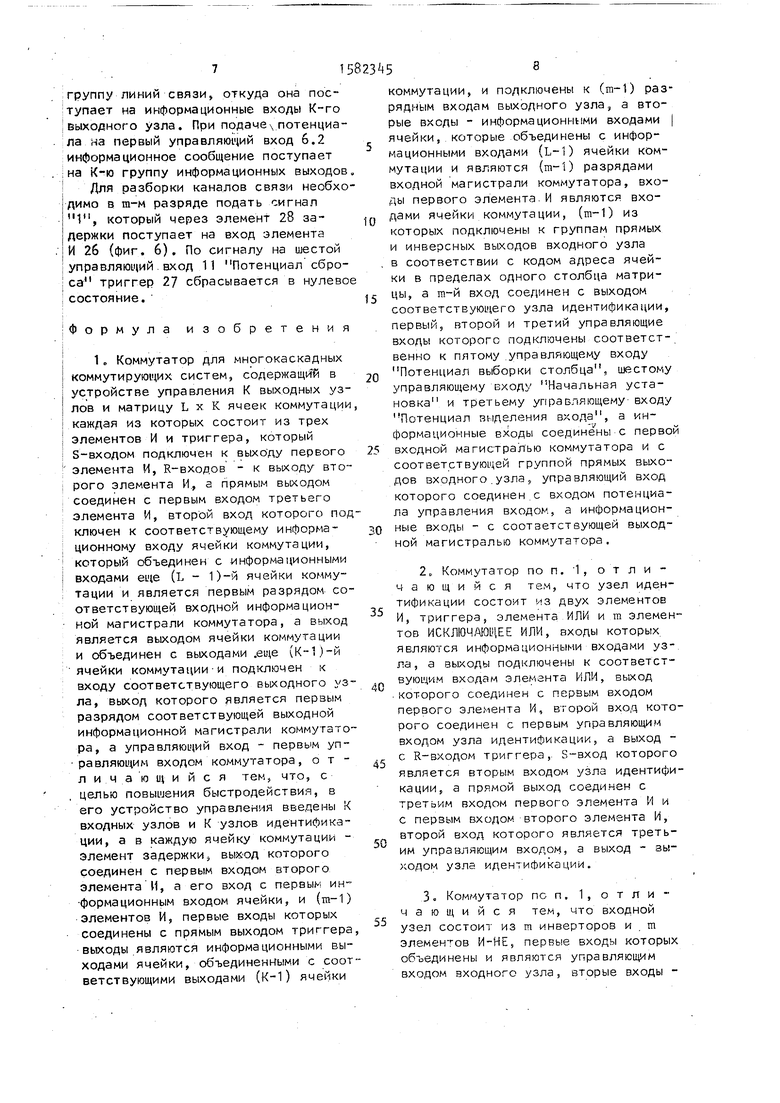

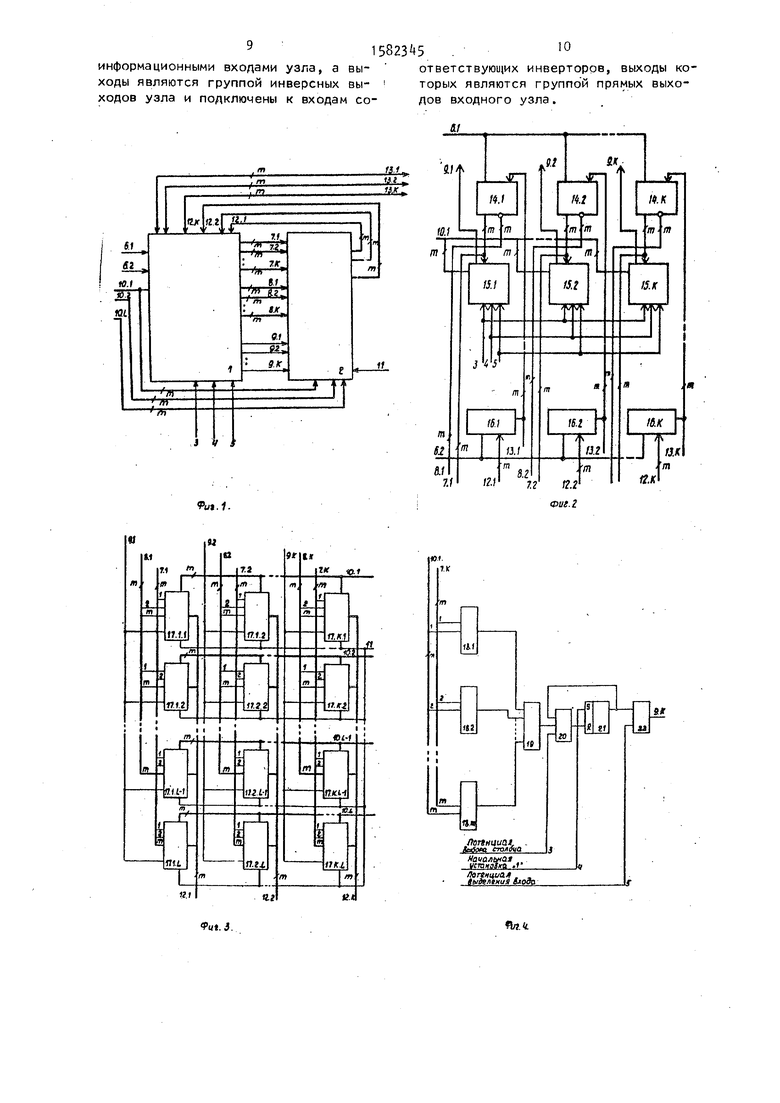

На фиг. 1 приведена структурная схема коммутатора для многокаскадных коммутирующих систем; на фиг. 2 - структурная схема устройства управления; на фиг. 3 - структурная схема матрицы ячеек коммутации;на фиг. 4 функциональная схема узла идентификации1, на фиг. 5 - функциональная схема входного узла , на фиг. b - функциональная схема ячейки коммутации.

На фиг. 1-6 приняты следующие обозначения: 1 - устройство управления; 2 - матрица ячеек коммутации; 3 - пятый управляющий вход Потенциал выборки столбца 4 - шестой управляющий вход Начальная установка, 5 - третий управляющий вход Потенциал выделения входа ; 6.1 - второй управляющий вход Потенциал управлеел

00 №

СО

ел

31

ния аходом ; 6.2 - первый управляющий вход Потенциал управления входом ; 7.К - группа прямых выходов К-го входного узла; 8.К - группа инверсных выходов К-го входного узла; 9.К - выход К-го узла идентификации; 10.L - входная магистраль; 11 - шестой управляющий вход Потенциал сброса, 12.К - группа линий связи, соединенная с К-м выходным узлом; (13.К - выходная магистраль; 14,К - К-й входной узел; 15.К - К-й узел идентификации; 16.К - К-й выходной узел; 17.K.L - ячейка коммутации, расположенная на пересечении К-й группы информационных выходов и L-й группы информационных входов, 18.1- 18.га - элементы ИСКЛЮЧАЮЩЕЕ ИЛИ;19 - элемент ИЛИ| 20 - элемент И, 21 - триггер; 22 - элемент HJ 23.1-23.m - элементы И-НЕ; 24.1-24.rn - элементы ИЛИ-НЕ; 25 - элемент И, 26 - элемент И; 27 триггер; 28 - элемент задержки; 29.1-29.tn - элементы И-НЕ.

Коммутатор для многокаскадных коммутирующих систем содержит (фиг.З L K ячеек 17.1.1, 17.1.2,..., 17.К.L коммутации, объединенных в матрицу 2, и (фиг. 2) выходные узлы 16.1 - 16.К, узлы 15.1-15.К идентификации и входные узлы 14.1-Й.К, образующие устройство 1 управления. Каждая из L входных информационных магистралей 10.1-10.L подключена к информационным входам К ячеек 17.K.L коммутации образующих строку матрицы 2 (фиг.З) Информационная магистраль 10.1, кроме того, подключена к узлам 15.1 15.К идентификации в устройстве 1 управления. Выходные магистрали 13. 13.2, ..., 13.К подключены к входам входных узлов 14.1, 14.2,...,14.К и к тристабильным выходам выходных узлов 16.1, 16.2,.„.,16.К в устройств управления.

Информационные выходы ячеек 17.К.1-17.К.L коммутации, образующих один столбец матрицы, объединен и соединены с входами 12.1-12.К выходных (устройств 16.1-16.К устройства управления. Прямые 7. и инверсные 8.1-8.К выходы входных узло 14J-14.K соединены с информационны (ми входами ячеек 17.К. 1-17.КД, коммутации одного столбца матрицы в соответствии с двоичным кодом номера ячейки в столбце. Кроме того, прямы выходы 7. подключены к информа

5

0

5

0

5

0

5

5

ционным входам узлов идентификации 15.1-15.6. Выходы 9,.К узлов идентификации подключены к управляющим входам ячеек 17.K/L коммутации, расположенных в К-м столбце матрицы.

Узел 15.К идентификации (фиг. 4) предназначен для параллельного сравнения га разрядов адресных кодов и выполняет две последовательные функции: выборку кристалла и выделение столбца матрицы ячеек коммутации. Этот узел состоит из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8j-l8.m, элемента ИЛИ 19, элемента И 20, триггера 21, элемента И 22. Входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18.1-18.т являются входами узла идентификации, которые подключены к К-й группе прямых выходов К-го входного узла и к К-й группе инверсных выходов К-го входного узла и служат для передачи сравниваемых кодов. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18.1- 18.m являются входами элемента ИЛИ 19, который своим выходом подключен к второму входу элемента И 20, у которого имеется еще два входа: один соединен с пятым управляющим входом 3 Потенциал выборки столбца, а другой подключен к прямому выходу триггера 21, вход сброса которого соединен с выходом элемента И 20, а вход установки - с шестым управляющим входом 4 Начальная установка. Прямой выход триггера 21, кроме того, подключен к первому входу элемента И 22, второй вход которого соединен с третьим управляющим входом 5 Потенциал выделения входа. Выход элемента И 22 является выходов 9.К узла идентификации, подсоединенным к т-му управляющему входу соответствующих ячеек коммутации.

Входной узел 14.К (фиг. 5) предназначен для формирования уровней адресных кодов и определения их инверсных значений. Он состоит из элементов И-НЕ 23.1-23.т и элементов НЕ 24.1-24.т. Один из входов каждого из элементов И-НЕ 23.1-23.га соединен с вторым управляющим входом 6.1 Потенциал управления входом, а остальные входы - с разрядами соответствующей группы информационных выходов 13.К. Выходы элементов И-НЕ 23..rn соединены с входами элементов 24.1-24.та и образуют группу инверсных выходов узла 8.К, а выхо10

20

25

ы инверторов - группу прямых выхоов узла 7-К о

Ячейка 17.K.L коммутации (фиг. 6) остоит из элементов И 25 и 2б,триг-| гера 27, элемента 28 задержки и элементов И-НЕ 29.1-29.т. Первые т управляющих входов ячейки коммутации и элемента И 25 подключены к группам прямых и инверсных выходов соответствующего входного узла, а оставшийся управляющий вход 9.К - к,выходу соответствующего узла идентификации (выходу элемента И 22). Выход элемента И 25 соединен с входом установки триггера 27, прямой выход которого подключен к одному из входов элементов И-НЕ 29.1-29.п и управляет режимом передачи информации с входа на выходо Оставшиеся входы элементов И-НЕ 29.1-29.m соединены с L-й группой информационных входов 10.L, а выходы подключены к К-й группе линий 12.К связи, соединенной с К-м выходным узлом 16.К. Кроме того, m-й разрядный вход L-й группы информационных входов подключается к входу элемента 28 задержки, выход которого соединен с первым входом элемента И 26, который своим вторым входом подключен к шестому управляющему входу 11, а входом - к входу сброса триггера 27.

Коммутатор для многокаскадных коммутирующих систем работает следующим образом.

Перед началом работы производится установка всех триггеров 21 в узлах 15.К идентификации в единичное состояние с помощью сигнала, поданного на шестой управляющий вход А Начальная установка.

Для поиска каналов связи необходимо на группы информационных выходов 13.1, 13.2,...,13.К коммутирующей системы одновременно подать адреса групп информационных входов 10.1, 10.2,...,10.L, р которыми каждая из групп информационных выходов должна быть соединена. Адрес групп информационных входов состоит из двух частей: адреса коммутирующего блока и. адреса конкретных входов в пределах этого коммутирующего блока. Адрес коммутирующего блока может задаваться в зависимости от места расположе- ния этого коммутирующего блока в коммутирующей системе, а адрес входа является фиксированным. Процесс по- ,

15

50

30

35

40

45

55

0

5

иска начинается подачей потенциала на второй управляющий вход 6.1 Потенциал управления входом. Этот потенциал подготавливает входные узлы 14. К к приему адресов коммутирующих блоков с К-й группы информационных выходов и разрешает прохождение сиг нала о результате сравнения адресных кодов на вход элемента И 20 (фиг.k), выход которого подключен к входу сброса триггера 21. Адресные коды с первой группы информационных входив 10.1 и с прямых выходов 7.К соответ5 ствующих входных узлов И.К поступают для сравнения на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 18.1. 18.2,...,18.га в узлах 15.1, 15-2,...,15.К идентификации. Сигналы поразрядного сравнения с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЯИ 18.m поступают на входы элемента ИЛИ 19, выход которого подключен к одному из входов элемента И 20. Этот элемент стробируется сигналом, поступающим на пятый управляющий вход 3 Потенциал выборки столбца. В случае неравенства хотя бы одного из разрядов триггер 21 сигналом с элемента И 20 сбрасывается в инверсное состояние. В случае равенства адресных кодов триггер 21 остается в прямом состоянии.

Следующий этап работы связан с поиском требуемой группы информационных входов о Для этого -на третий управляющий вход 5 Потенциал выделения входа подается потенциал, который пропускает единичный сигнал с прямого выхода триггера 21 через элемент И 22. Сигнал с выхода этого элемента проходит на вход 9.К элемента И 25 (фиг. 6), входы которого являются входами яче.ек коммутации, связанных с одной группой информационных выходов. В той ячейке коммутации, в которой дешифрируется адрес, поступающий по соответствующей группе информационных выходов, гер 27 перебрасывается в единичное

0 состояние, подготавливая элементы. И-НЕ 29..rn к передаче информационного сообщения. Этим заканчивается этап, связанный с режимом настройки коммутатора.

8 режиме передачи сообщения информация с L-й группы информационных входов (фиг. 6) передается через элементы И-НЕ 29.1-29.tn, открытые установленными триггерами 27, на К-ю

0

5

0

5

5

группу линий связи, откуда она посупает на информационные входы К-го выходного узла. При подаче потенциаа ria первый управляющий вход 6.2 информационное сообщение поступает на К-ю группу информационных выходов Для разборки каналов связи необхоимо в m-м разряде подать сигнал 1, который через элемент 28 за- ержки поступает на вход элемента 26 (фиг. 6). По сигналу на шестой управляющий вход 11 Потенциал сброса триггер 27 сбрасывается в нулевое состояние.

ормула изобретения

1 „ Коммутатор для многокаскадных коммутирующих систем, содержащий в устройстве управления К выходных узлов и матрицу L х К ячеек коммутации, каждая из которых состоит из трех элементов И и триггера, который S-входом подключен к выходу первого элемента И, R-входов - к выходу второго элемента И, а прямым выходом соединен с первым входом третьего элемента И, второй вход которого подключен к соответствующему информационному входу ячейки коммутации, который объединен с информационными входами еще (L - 1)-й ячейки коммутации и является первым разрядом соответствующей входной информационной магистрали коммутатора, а выход является выходом ячейки коммутации и объединен с выходами .еще (К-1)-й ячейки коммутации и подключен к входу соответствующего выходного узла, выход которого является первым разрядом соответствующей выходной информационной магистрали коммутатора, а управляющий вход - первым управляющим входом коммутатора, отличающийся гем, что, с целью повышения быстродействия, в его устройство управления введены К входных узлов и К узлов идентификации, а в каждую ячейку коммутации - элемент задержки, выход которого соединен с первым входом второго элемента И, а его вход с первые информационным входом ячейки, и (тп-1) элементов И, первые входы которых соединены с прямым выходом триггера, выходы являются информационными выходами ячейки, объединенными с соответствующими выходами (К-1) ячейки

5

0

5

5

0

5

0

5

коммутации, и подключены к (т-1) разрядным входам выходного узла, а вторые входы - информационными входами | ячейки, которые объединены с информационными входами (L-1) ячейки коммутации и являются (т-1) разрядами входной магистрали коммутатора, входы первого элемента И являются входами ячейки коммутации, (т-1) из которых подключены к группам прямых и инверсных выходов входного узла в соответствии с кодом адреса ячейки в пределах одного столбца матрицы, а га-й вход соединен с выходом соответствующего узла идентификации, первый, второй и третий управляющие входы которого подключены соответственно к пятому управляющему входу Потенциал выборки столбца, шестому управляющему сходу Начальная установка и третьему управляющему входу Потенциал выделения входа, а информационные входы соединены с первой входной магистралью коммутатора и с соответствующей группой прямых выходов входного узла 5 управляющий вход которого соединен с входом потенциала управления входом, а информационные входы - с соответствующей выходной магистралью коммутатора.

2, Коммутатор по п. 1, о т л и - чающийся тем, что узел идентификации состоит из двух элементов И, триггера, элемента ИЛИ и m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которых являются информационными входами узла, а выходы подключены к соответствующим входам элемэнта ИЛИ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым управляющим входом узла идентификации, а выход - с R-входом триггера, S-вход которого является вторым входом узла идентификации, а прямой выход соединен с третыим входом первого элемента И и с первым входом второго элемента И, второй вход котооого является третьим управляющим входом, а выход - выходом узла идентификации.

3 „ Коммутатор пс п, 1, о т л и - чающийся тем, что входной узел состоит из m инверторов и m элементов И-НЕ, первые входы которых объединены и являются управляющим входом входного узла, вторые входы 915823 510

информационными входами узла, а вы-ответствующих инверторов, выходы коходы являются группой инверсных выходов узла и подключены к входам соторых являются группой прямых выходов входного узла.

торых являются группой прямых выходов входного узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| Трехкаскадная коммутирующая система | 1989 |

|

SU1622886A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| Цифровое устройство доплеровской фильтрации | 1990 |

|

SU1830496A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Систолический автомат | 1990 |

|

SU1732340A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в вычислительных системах. Целью изобретения является повышение быстродействия коммутатора на этапе настройки путем одновременного поиска всех требуемых каналов связи с помощью многоразрядных кодов. Коммутатор содержит устройство управления, в состав которого входит К выходных узлов и матрицу L х К ячеек коммутации, каждая из которых состоит из триггера и элементов И. Коммутатор также содержит К входных узлов и К узлов идентификации, введенных в устройство управления. Повышение быстродействия на этапе передачи информации достигается также введением (M - 1) дополнительного элемента И в каждую ячейку коммутации. Элемент задержки, введенный в ячейку коммутации, обеспечивает индивидуальную разборку каналов связи. Настройка коммутатора производится за два шага. Уменьшается также время передачи информационного сообщения за счет одновременности передачи его разрядов. 6 ил.

.

к агГШ

-Ф

11

ИИ

7

tl

JE

/r

% 1

P«« j

Фиг Z

Я1rittJ

flrtft.

т

В.н

4 Фиг. 5

чп

Ж/Г

25

27

28

11

Ю.1

,т

1т

Ш

ОГ2.К1

т

72, Л 2

Г2,Кт

Ю.Ц

Ю,1т

Фиг. 6

| Матричный коммутатор | 1983 |

|

SU1102038A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-30—Публикация

1988-10-05—Подача