Изобретение относится к вычислительной технике, в частности к запомнающим устройствам, и может быть использовано при построении многоканальных коммутирующих систем.

Цель изобретения - расширение области применения ячейки памяти за счет осуществления в ней реверса информации.

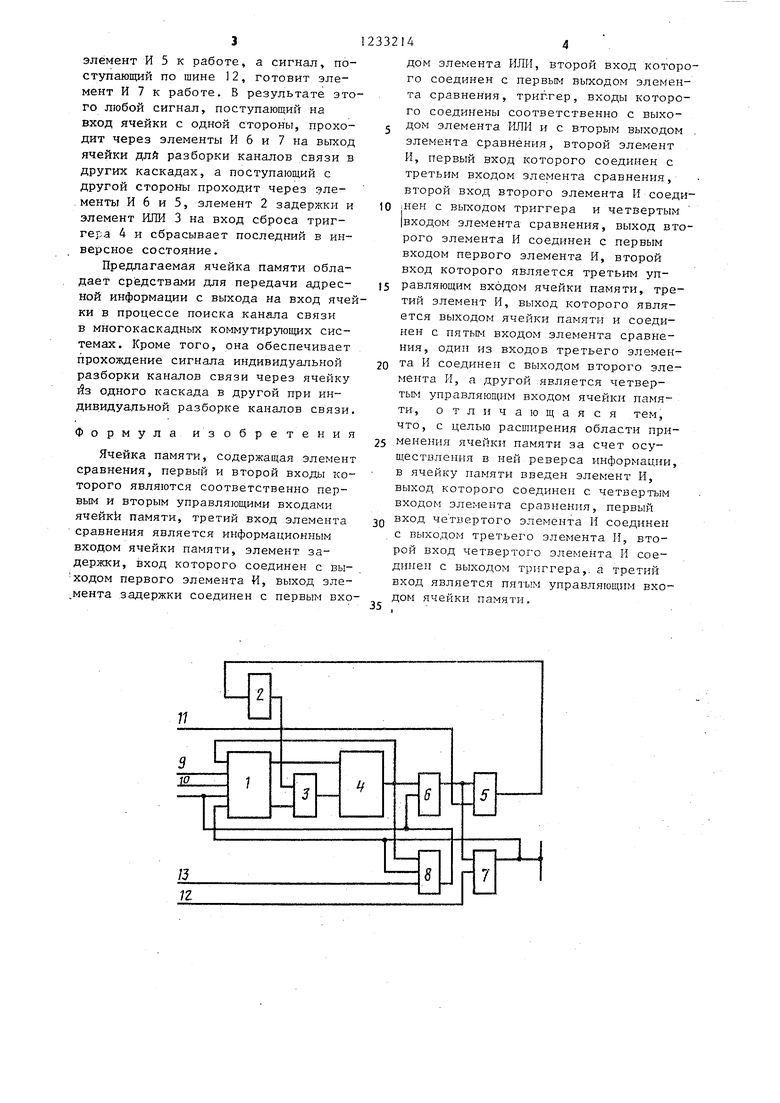

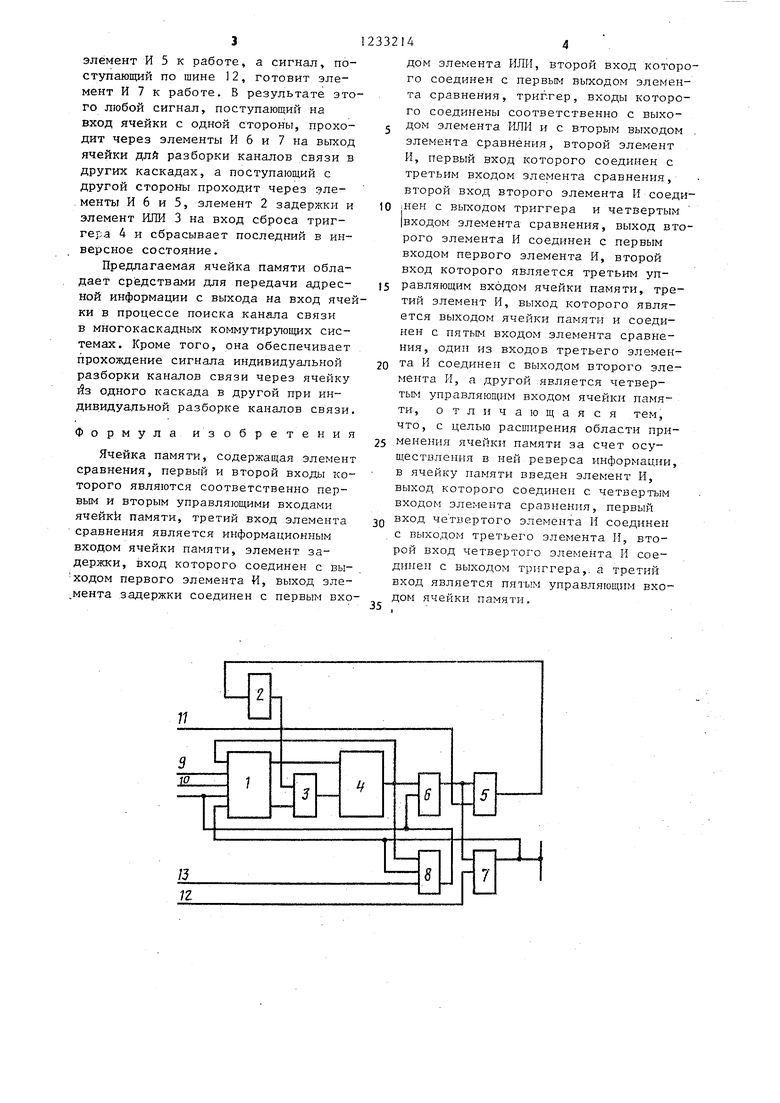

На чертеже приведена функциональ- ная схемэ предлагаемой ячейки памяти

Устройство содержит элемент 1 сравнения, элемент 2 задержки, элемент ИЛИ 3, триггер 4, элементы И 5- 8, шины 9-13 управления. Элемент 1 сравнения может быть выполнен на элементе сложения по модулю два, элементе ИЛИ и двух элементах И. Элемен 7 предназначен для блокировки передачи информации с выхода элемента И на выход ячейки, элемент И 8 - для передачи адресной информации с выход ячейки на ее вход, элемент ИЛИ 3 - для формироваг-шя сигнала сброса триггера 4 и выработки сигнала неравен- ства в элементе 1 сравнения, а элемент И 5 - для выделения сигнала индивидуальной выборки канала связи.

Ячейка работает- следующим обраsp

) Дпя фиксаций входного сигнала на

шину 10 подается сигнал, который поступает на второй вход, элемента I и готовит его к работе. Поиск инфор- мацин производится подачей на выход ячейки адресной информации. Адресная информация представляет собой последовательность адресов, первый из которых предназначен для управ- ления поиском и фиксацией кана- ,ла связи в рассматриваемой ячейке, а Остальные адреса должшл передаваться с выхода ячейки на ее вход, если канал связи проходит через эту .ячейку, или блокироваться, если канал связи через ячейку не проходит. Одновременно на вход ячейки подается а,о;рес, соответствующий входу данной ячейки памяти. Первый адрес с выхода ячейки и адрес с ее выхода поразрядно поступают на тре- тий и пятый входы элемента 1 сравнения. Одновременно с поступлением на элемент 1 сравнения первых; раз- рядов адресных кодов на первый вход элемента 1 сравнения по шине 9 посту .пает запускшощий импульс. Если первые разряды адресных кодов одинаковы, то единичный сигнал со второго

S 0 5

0

5

0

5

выхода элемента 1 поступает на вход установки триггера -4 и переводит его в прямое состояние. Потенциал с прямого выхода триггера 4 поступает на четвертый вход элемента 1 сравнения и разрешает сравнение следую- шдх разрядов адресных кодов, удерживая через элемент ИЛИ 3 в открытом состоянии cooтвeтcтвyюшJ e элементы И элемента . Каждый следующий сигнал равенства подтверждает прямое состояние триггера 4. Сигнал неравенства, выработанный элементом 1 . на любом шаге сравнения, сбрасывает триггер 4 в инверсное состояние и тем самым прекращает дальнейшее сравнение адресных кодов в элементе 1 сравнет ия, После прохоящения всех разрядов первого адреса из адресной информации с шины 10 снимается сигнал поиска и дальнейшее сравнение ал,ресов в элементе 1 сравнения прекращается .

В результате, если на вход и выход ячейки памяти поступают одинаковые адресные коды, то триггер 4 устанавливается в единичное состоя- iffle; если же адресные коды разные, то 4 находится в инверсном состоянии. Прямое состояние триггера 4 соответствует зафиксированному каналу связи. Триггер 4, находящийся в прямом состоянии, ГОТО-: БИТ к работе элементы И 6 и 8. Одновременно со снятием сигнала с шины 10 поступает сигнал на гаину 13, При этом, если триггер 4 находится в прямом состоя нии, то все следующие адреса проходят через элемент И 8 на вход ячейки для идентификации каналов связи в следуювщх каскадах. Длительность сигнала на шине 13 определяется количеством каскадов, через 1соторые проходит канал связи, и разрядностью каждого адреса, проходящего через элемент И 8, После прохокд ения всей адресной информации сигнал с шимл 13 снимается,

В режиме передачи информационного сообщения на элемент И 8 по шине 12 поступает сигнал, разреЕ;ающкй передачу сооба(ения с входа на выход ячейки., Информационное сообщение при этом проходит через открытый потенц1|алом с прямого выхода триггера 4 на вход элемента И 6.

При разборке канала связи сигнал, поступаю1ллй по шине 1 1 , готовит

3

элемент И 5 к работе, а сигнал, поступающий по шине 12, готовит элемент И 7 к работе. В результате этого любой сигнал, поступающий на вход ячейки с одной стороны, проходит через элементы И 6 и 7 на выход ячейки дли разборки каналов связи в других каскадах, а поступающий с другой стороны проходит через дле- ,менты И 6 и 5, элемент 2 задержки и элемент ИЛИ 3 на вход сброса триггера 4 и сбрасывает последний в инверсное состояние.

Предлагаемая ячейка памяти обладает средствами для передачи адресной информации с выхода на вход ячейки в процессе поиска канала связи в многокаскадных коммутирзпощих системах. Кроме того, она обеспечивает прохождение сигнала индивидуальной разборки каналов связи через ячейку из одного каскада в другой при индивидуальной разборке каналов связи

Формула изобретения

Ячейка памяти, содержащая элемен сравнения, первый и второй входы которого являются соответственно первым и вторым управляющими входами ячейки памяти, третий вход элемента сравнения является информационным входом ячейки памяти, элемент задержки, вход которого соединен с вы- ходом первого элемента И, выход эле- ,мента задержки соединен с первым вхо332144

дом элемента ИЛИ, второй вход которого соединен с первым выходом элемента сравнения, триг.гер, входы которого соединены соответственно с выхо- 5 дом элемента ИЛИ и с вторым выходом . элемента сравнения, второй элемент И, первый вход которого соединен с третьим входом элемента сравнения, второй вход второго элемента И соеди- 10 ней с выходом триггера и четвертым входом элемента сравнения, выход второго элемента И соединен с первым входом первого элемента И, второй вход которого является третьим уп- 15 равляющим входом ячейки памяти, третий элемент И, выход которого является выходом ячейки памяти и соединен с пятым входом элемента сравнения, один из входов третьего элемен- 20 та И соединен с выходом второго элемента И, а другой является четвертым управляющим входом ячейки памяти, отличающаяся тем, что, с целью расширения области при- 25 .мене}1ия ячейки памяти за счет осуществления в ней реверса информации, в ячейку памяти введен элемент И, выход которого соединен с четвертым входом элемента сравнения, первый 2Q вход четвертого элемента И соединен с выходом третьего элемента И, второй вход четвертого И соединен с выходом триггера,, а третий вход является пятым управляющим входом ячейки памяти, 3j I

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Ячейка памяти матричного коммутатора | 1975 |

|

SU575697A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении многоканальных коммутирующих систем С целью расширения области применения ячейки памяти за счет осуществления реверса информации она дополнена четвертым элементом И, выход которого соединен с четвертым входом элемента сравнения, первый вход четвертого элемента И соединен с выходом третьего элемента И, второй вход четвертого элемента И соединен с выходом триггера, а третий вход является пятым управляющим входом ячейки памяти. Одновременно ячейка памяти обладает средствами для передачи . адресной информации с выхода на вход ячейки в процессе поиска канала связи в многокаскадных коммутирующих системах. 1 ил. S (Л

| Патент Франции № 2052043, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Стрелочный контрольный замок | 1924 |

|

SU422A1 |

Авторы

Даты

1986-05-23—Публикация

1984-07-27—Подача