1226618

10, 12, 15, 7, 8 и 16 являются квази- а стоки двуистоковьк транзисторов линейными нагрузочными транзисторами, гальванически развязаны,

1 ил. 2 т

1

Изобретение относится к импульсной электронике и может быть использовано в цифровых устройствах автоматики и вычислительной техники.

Цель изобретения - повышение надежности и быстродействия тактируемого JK-триггера путем выполнения ведущего и ведомого триггеров на двуисто- ковых транзисторах и включения параллельно транзисторам ведущего триггера дополнительно двух двуистоковых транзисторов.

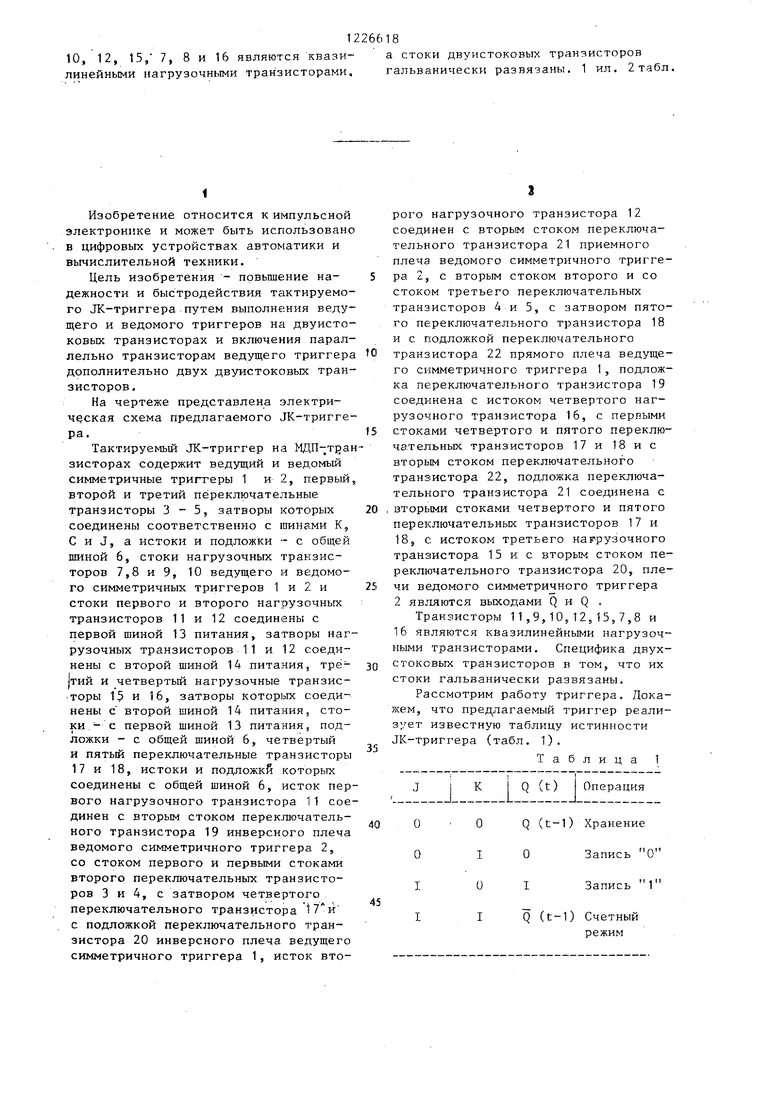

На чертеже представлена электри- схема предлагаемого JK-триггера.

Тактируемый JK-триггер на МДП-тран зисторах содержит ведущий и ведомый симметричные триггеры 1 и 2, первый второй и третий переключательные транзисторы 3-5, затворы которых соединены соответственно с 1пинами К, С и J, а истоки и подложки - с общей шиной 6, стоки нагрузочных транзисторов 7,8 и 9, 10 ведущего и ведомого симметричных триггеров 1 и 2 и стоки первого и второго нагрузочных транзисторов 11 и 12 соединены с первой шиной 13 питания, затворы нагрузочных транзисторов 11 и 12 соединены с второй шиной 14 питания, трё- |тий и четвертый нагрузочные трашзис- торы 15 и 16, затворы которых соединены с второй шиной 14 питания, стоки,- с первой шиной 13 питания, подложки - с общей шиной 6, четвертый и пятый переключательные транзисторы 17 и 18, истоки и подложки которых соединены с общей шиной 6, исток первого нагрузочного транзистора 11 соединен с вторым стоком перек.пючатель- ного транзистора 19 инверсного плеча ведомого симметричного триггера 2, со стоком первого и первыми стоками второго переключательных транзисторов 3 и 4, с затвором четвертого переключательного транзистора с подложкой переключательного транзистора 20 инверсного плеча ведущего симметричного триггера 1, исток втозисторов

1 ил. 2 табл.

рого нагрузочного транзистора 12 соединен с вторым стоком переключательного транзистора 21 приемного плеча ведомого симметричного триггера 2, с вторым стоком второго и со стоком третьего переключательных транзисторов 4 и 5, с затвором пятого переключательного транзистора 18 и с подложкой переключательного транзистора 22 прямого плеча ведущего симметричного триггера 1, подложка переключательного транзистора 19 соединена с истоком четвертого нагрузочного транзистора 16, с перяыми стоками четвертого и пятого переключательных транзисторов 17 и 18 и с вторым стоком переключательного транзистора 22, подложка переключательного транзистора 21 соединена с , вторыми стоками четвертого и пятого перев;лючательных: транзисторов 17 и 18, с истоком третьего нагрузочного транзистора 15 и с вторым стоком переключательного транзистора 20, плечи ведомого симметричного триггера 2 являются выходами Q и Q .

Транзисторы 11,9,10,12.,15,,7,8 и 16 являются квазилинейными нагрузочными транзисторами. Специфика двух- стоковьгх транзисторов в том, что их стоки: гальванически развязаны.

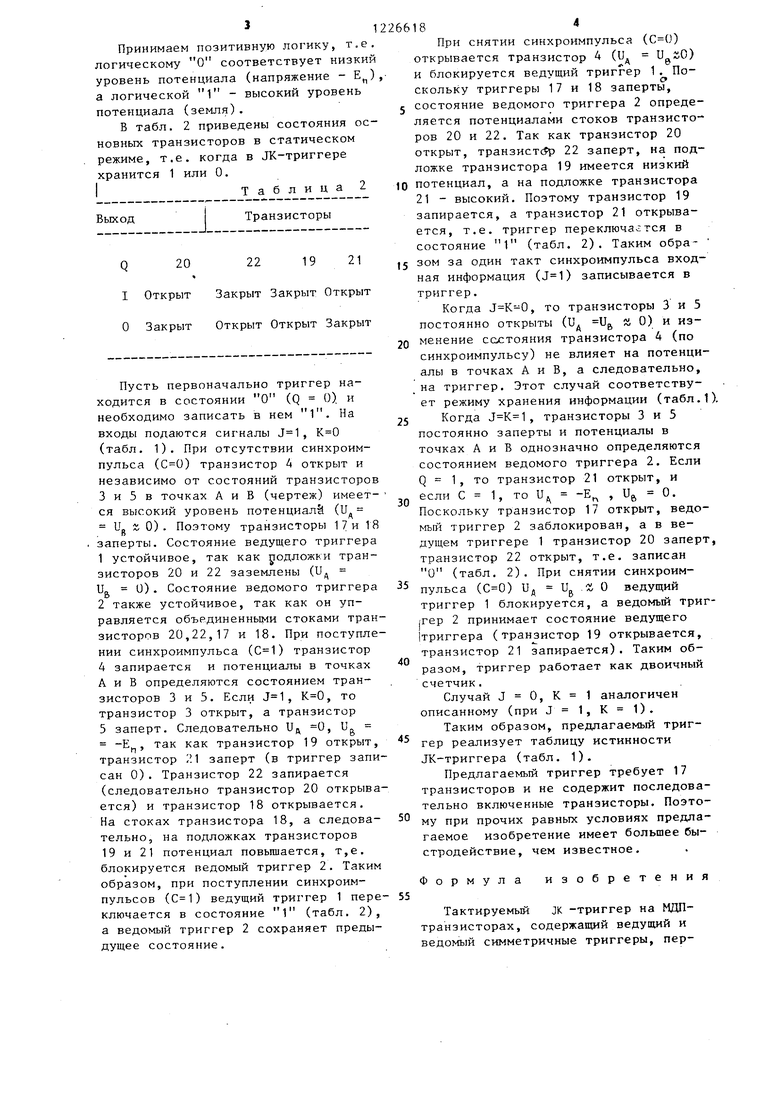

Рассмотрим работу триггера. Докажем, что предлагаемый триггер реализует известную таблицу истинности JK-триггера (табл. 1).

Таблица 1

1

Принимаем позитивную логику, т.е. логическому О соответствует низкий уровень потенциала (напряжение Е) а логической 1 - высокий уровень потенциала (земля).

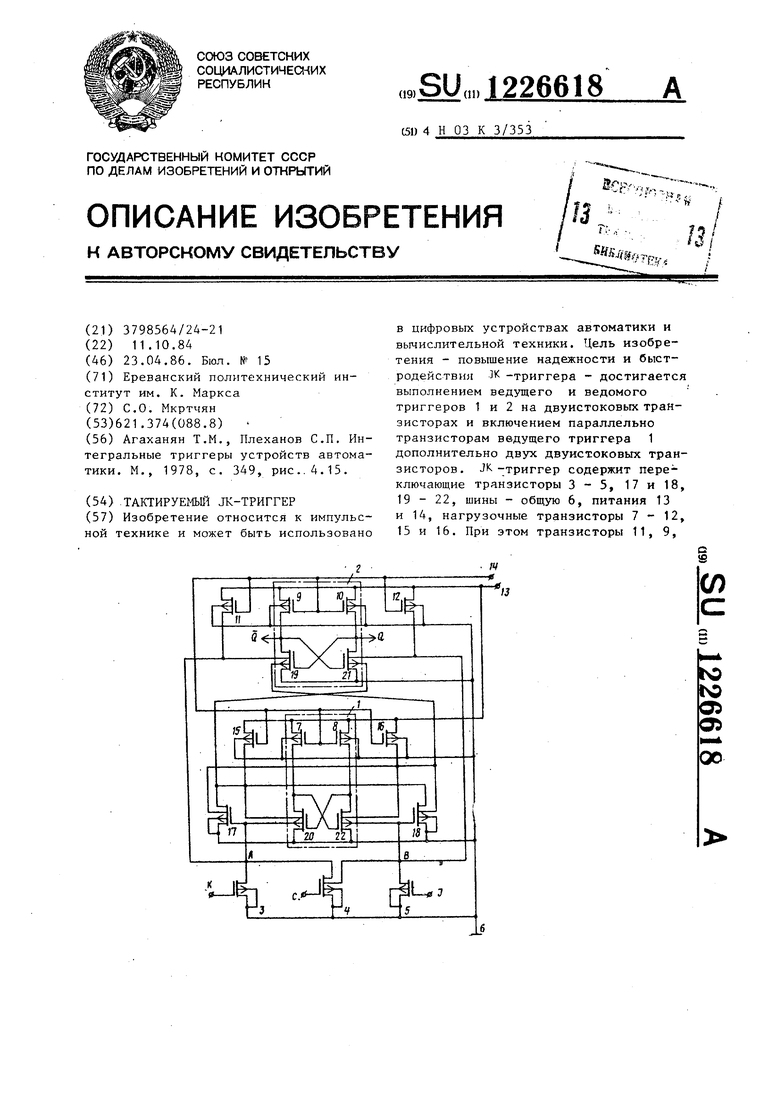

В табл. 2 приведены состояния основных транзисторов в статическом режиме, т.е. когда в JK-триггере хранится 1 или 0. IТаблица2

Выход

.1

Транзисторы

Q 20 22 19 21

«

I ОткрытЗакрыт Закрыт Открыт

О ЗакрытОткрыт Открыт Закрыт

Пусть первоначально триггер находится в состоянии О (Q О), и необходимо записать в нем 1. На входы подаются сигналы , (табл. 1). При отсутствии синхроимпульса () транзистор А открыт и независимо от состояний транзисторов

3и 5 в точках А и В (чертеж) имеет- ся высокий уровень потенциал (U

Up % 0). Поэтому транзисторы 17 и 18 заперты. Состояние ведущего триггера

1устойчивое, так как уодложки транзисторов 20 и 22 заземлены (U

Ug 0). Состояние ведомого триггера

2также устойчивое, так как он управляется объединенными стоками транзисторов 20,22,17 и 18. При поступлении синхроимпульса () транзистор

4запирается и потенциалы в точках А и В определяются состоянием транзисторов 3 и 5. Если , , то транзистор 3 открыт, а транзистор

5заперт. Следовательно U 0, U -Е|, так как транзистор 19 открыт, транзистор . 1 заперт (в триггер записан 0). Транзистор 22 запирается (следовательно транзистор 20 открывается) и транзистор 18 открывается.

На стоках транзистора 18, а следовательно, на подложках транзисторов 19 и 21 потенциал повышается, т,е. блокируется ведомый триггер 2. Таким образом, при поступлении синхроимпульсов () ведущий триггер 1 переключается Б состояние 1 (табл. 2), а ведомый триггер 2 сохраняет предыдущее состояние.

266184

При снятии синхроимпульса () открывается транзистор 4 (Ь д U ;SO)

и блокируется ведущий триггер 1. Пос

скольку триггеры 17 и 18 заперты, 5 состояние ведомого триггера 2 определяется потенциалами стоков транзисторов 20 и 22. Так как транзистор 20 открыт, транзистсУр 22 заперт, на подложке транзистора 19 имеется низкий

10 потенциал, а на подложке транзистора 21 - высокий. Поэтому транзистор 19 запирается, а транзистор 21 открывается, т.е. триггер переключается в состояние 1 (табл. 2). Таким обра-

J5 зом за один такт синхроимпульса входная информация () записывается в триггер.

Когда , то транзисторы 3 и 5 постоянно открыты (и. Ug, и 0) и из20 менение ссх;тояния транзистора 4 (по синхроимпульсу) не влияет на потенциалы в точках А и В, а следовательно, на триггер. Этот случай соответствует режиму хранения информации (табл.1).

25 Когда , транзисторы 3 и 5 постоянно заперты и потенциалы в точках А и В однозначно определяются состоянием ведомого триггера 2. Если Q 1, то транзистор 21 открыт, и jQ если С 1, то Up -Е , Ug, 0.

Поскольку транзистор 17 открыт, ведомый триггер 2 заблокирован, а в ведущем триггере 1 транзистор 20 заперт, транзистор 22 открыт, т.е. записан О (табл. 2). При снятии синхроим- пульса () и. и. . О ведущий

М D

триггер 1 блокируется, а ведомый триггер 2 принимает состояние ведущего триггера (транзистор 19 открывается, транзистор 21 запирается). Таким образом, триггер работает как двоичный счетчик.

Случай J О, К 1 аналогичен описанному (при J 1, К 1).

Таким образом, предлагаемый три:- гер реализует таблицу истинности JK-триггера (табл. 1).

Предлагаемый триггер требует 17 транзисторов и не содержит последовательно включенные транзисторы. Поэто- му при прочих равных условиях предлагаемое изобретение имеет большее быстродействие, чем известное.

40

Формула изобретения

Тактируемый JK -триггер на МДП- транзисторах, содержащий ведущий и ведомый симметричные триггеры, первый, второй и третий переключательные транзисторы, затворы которых соединены соответственно с шинами К, С и J, а истоки и ПОДЛОЖКИ - с общей шиной, стоки нагрузочных транзисторов ведущего и ведомого симметричных триггеров и стоки первого и второго нагрузочньк транзисторов соединены е первой шиной питания, затворы всех нагрузочных транзисторов соединены с второй шиной питания, отличающийся тем, что, с целью повышения надежности и быстродействия, в него введены третий и четвер- тый нагрузочные транзисторы, затворы которых соединены с второй шиной питания, стоки - с первой шиной питания, подложки - с общей шиной, четвертый и пятый переключательные тран- зисторы,истоки и подложки которых соединены с общей шиной,исток первого нагрузочного транзистора соединен с вторым стоком переключательного транзистора инверсного плеча ведомого сим- метричного триггера, со стоком первого и первым стоком второго переключательных транзисторов, с затворо четвертого перекл рчательного транзистора и с подложкой переключатель- кого транзистора инверсного плеча ведущего симметричного триггера, исРедактор Н. Рогулич Заказ 2146/57

Составитель А. Кабанов

Техред В.Ксщар Корректор А. Тяско

Тираж 816 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ток второго нагрузочного транзистора соединен с вторым стоком переключательного транзистора прямого плеча ведомого симметричного триггера, с

вторым стоком второго и со CTOKON

третьего переключательных транзисторов j с затвором пятого переключательного транзистора и с подложкой пере- хлючательного транзистора прямого плеча ведущего симметричного триггера, подложка переключательного транзистора инверсного плеча ведомого симметричного триггера соединена с истоком четвертого нагрузочного транзистора, с первыми стоками четвертого и пятого переключательных транзисторов и с вторым стоком переключательного транзистора прямого плеча ведущего симметричного триггера, подложка переключательного транзисто )эа прямого плеча ведомого симметричного триггера соединена с вторыми стоками четвертого и пятого переключательных транзисторов, с истоком третьего нагрузочного транзистора и с вторым стоком переключательного транзистора инверсного плеча ведущего симметричного триггера, пчи ведомого симметричного тригра являются выходами JK- триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Формирователь суммы на мдп-транзисторах | 1972 |

|

SU516038A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Усилитель записи-считывания на КМДП-транзисторах | 1988 |

|

SU1571673A1 |

| IK-триггер | 1988 |

|

SU1554114A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

| Триггер с индикацией моментов окончания переходных процессов | 1987 |

|

SU1420647A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах автоматики и вычислительной техники. Цель изобретения - повышение надежности и быстродействия К -триггера - достигается выполнением ведущего и ведомого триггеров 1 и 2 на двуистоковых транзисторах и включением параллельно транзисторам ведущего триггера 1 дополнительно двух двуистоковых транзисторов. J -триггер содержит переключающие транзисторы 3-5, 17 и 18, 19 - 22, шины - общую 6, питания 13 и 14, нагрузочные транзисторы 7 - 12, 15 и 16. При этом транзисторы 11, 9, (Л

| Агаханян Т.Н., Плеханов С.П | |||

| Интегральные триггеры устройств автоматики | |||

| М., 1978, с | |||

| Способ составления поездов | 1924 |

|

SU349A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-11—Подача