Изобретение относится к технической физике, а точнее к оптоэлектронике, к разделам считывания и хранения оптической информации, а также к полупроводниковым приборам, чувствительным к излучению.

Известны фотоприемные ячейки, предназначенные для сравнения (вычитания) двух оптических сигналов и фотоэлектрического преобразования парафазного оптического кода в электрический код. Это класс полупроводниковых устройств, которые содержат по крайней мере два фотоприемника для приема и фотоэлектрического преобразования сравниваемых оптических сигналов и дифференциальную схему. В качестве дифференциальной схемы в таких устройствах используются триггеры (устройства с положительной обратной связью) либо усилителя с коммутационными транзисторами, включаемыми в нужный момент времени. В этих условиях превышение уровня (энергии, мощности) оптического сигнала на одном фотоприемнике по сравнению с уровнем сигнала на другом фотоприемнике определяется по состоянию выхода триггера.

Недостаточная чувствительность первых устройств объясняется большими пороговыми напряжениями срабатывания триггера, технологическими разбросами входящих в него элементов (транзисторов, резисторов).

Наиболее близкой по технической сущности и признакам к описываемому устройству является фотоприемная ячейка, содержащая усилительные транзисторы, нагрузочные транзисторы, токостабилизирующий транзистор, фотодиоды, ключевые транзисторы записи-стирания и конденсатор.

Недостаток такой фотоприемной ячейки наличие начального разбаланса дифференциального усилителя, свойственного вообще используемому в ячейке дифференциальному усилителю. Начальный разбаланс дифференциального усилителя в таких ячейках возникает из-за несимметрии параметров элементов дифференциального усилителя и, складываясь с полезным сигналом на выходе дифференциального усилителя, напрямую ограничивает пороговую чувствительность такой фотоприемной ячейки. При этом важно подчеркнуть следующее обстоятельство: теоретический анализ и экспериментальные данные свидетельствуют о том, что наиболее существенный вклад и влияние на начальный разбаланс дифференциального усилителя оказывает несимметрия параметров усилительных транзисторов дифференциального усилителя и, в частности, несимметрия их пороговых напряжений. Откуда следует, что добившись симметрии усилительных транзисторов или скомпенсировав влияние этой несимметрии на начальный разбаланс дифференциального усилителя ячейки, можно существенно уменьшить реальный начальный разбаланс дифференциального усилителя ячейки и тем самым значительно увеличить ее пороговую чувствительность.

Указанные недостатки устраняются в описываемом устройстве, введением ключевых транзисторов балансировки и ключевого транзистора записи.

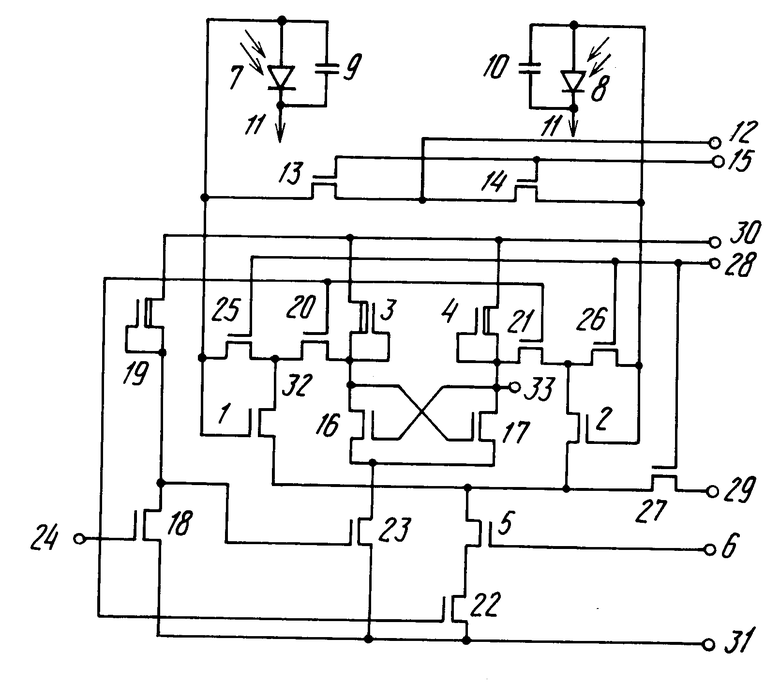

На чертеже представлена схема фотоприемного интегрального элемента памяти.

Он содержит третий и четвертый усилительные транзисторы 1 и 2, первый и второй нагрузочные транзисторы 3 и 4, токостабилизирующий транзистор 5, управляемый от задающей режим шины 6, фотодиоды 7 и 8 с собственными емкостями 9 и 10, подложку фотодиодов и транзисторов 11, шину смещения фотодиодов 12, ключевые транзисторы стирания 13 и 14, шину стирания 15, первый и второй усилительные транзисторы 16, 17 и ключевой транзистор 18, третий нагрузочный транзистор 19, первый, второй, третий и четвертый ключевые транзисторы записи 23, 20, 21, 22, шину записи 24, первый, второй и третий ключевые транзисторы балансировки 25, 26 и 27, шину балансировки 28, шину смещения балансировки 29, шину питания 30, общую шину 31, информационные выходы 32 и 33, инвертор записи 34.

Указанные элементы соединены между собой следующим образом.

Фотодиоды 7 и 8, имеющие собственные емкости 9 и 10, подключены к затворам соответственно третьего и четвертого усилительных транзисторов 1, 2 и к подложке 11. Стоки ключевых транзисторов стирания 13 и 14 соединены с шиной смещения фотодиодов 12, затворы этих транзисторов подключены к шине стирания 15, а истоки соответственно к затворам усилительных транзисторов 1 и 2. Сток третьего усилительного транзистора 1 соединен с истоками второго ключевого транзистора записи 20 и первого ключевого транзистора балансировки 25, сток четвертого усилительного транзистора 2 соединен с истоками второго ключевого транзистора записи 21 и второго ключевого транзистора балансировки 26, стоки второго и третьего ключевых транзисторов записи 20 и 21, являющиеся информационными выходами ячеек 32 и 33, подключены соответственно к затворам и истокам первого и второго нагрузочных транзисторов 3 и 4, истоки третьего и четвертого усилительных транзисторов 1, 2 и третьего ключевого транзистора балансировки 27 соединены со стоком токостабилизирующего транзистора 5, затвор которого подключен к шине управления 6, а исток к стоку четвертого ключевого транзистора записи 22, стоки первого и второго ключевых транзисторов балансировки 25, 26 соединены соответственно с затворами третьего и четвертого усилительных транзисторов 1 и 2, сток третьего ключевого транзистора балансировки 27 подключен к шине смещения балансировки 29, сток первого и затвор второго усилительных транзисторов 16 и 17 соединены с затвором и истоком первого нагрузочного транзистора 3, сток второго и затвор первого усилительных транзисторов 17 и 16 подключены к затвору и истоку второго нагрузочного транзистора 4, истоки первого и второго усилительных транзисторов 16 и 17 соединены со стоком четвертого ключевого транзистора записи 23, затвор которого подключен к затвору и истоку третьего нагрузочного транзистора 19 и стоку ключевого транзистора 18, затворы с второго по четвертый ключевых транзисторов записи 20, 21, 22 и затвор ключевого транзистора 18 соединены с шиной записи 24, затворы с первого по третий ключевых транзисторов балансировки 25, 26, 27 подключены к шине балансировки 28, стоки с первого по третий нагрузочных транзисторов 3, 4, 19 соединены с шиной питания 30, а истоки ключевого транзистора 18, четвертого и первого ключевых транзисторов записи 22 и 23 подключены к общей шине 31.

Принцип работы устройства состоит в следующем.

По сигналу стирания 15 через открытые каналы ключевых транзисторов 13 и 14 заряжаются до напряжения источника смещения 12 емкости 9 и 10 фотодиодов 7 и 8. По окончании сигнала стирания каналы транзисторов стирания запираются. Фотодиоды 7 и 8 оказываются обратно смещенными напряжениями, которые определяются зарядами, запасенными емкостями 9 и 10 во время стирания. Эти напряжения поступают на входы (затворы) усилительных транзисторов 1 и 2.

Дифференциальный усилитель, предназначенный для усиления разности напряжений на емкостях 9, 10 фотодиодов 7 и 8, возникающей при интегрировании входных оптических сигналов, образуется конфигурацией из третьего и четвертого усилительных транзисторов 1, 2, первого и второго нагрузочных транзисторов 3, 4, токостабилизирующего транзистора 5 при открытых каналах второго, третьего и четвертого ключевых транзисторов записи 20, 21, 22 и закрытом канале первого ключевого транзистора записи 23. Это соответствует наличию на шине записи 24 сигнала записи и инверсии этого сигнала инвертором 34, содержащим ключевой транзистор 18 и третий нагрузочный транзистор 19. Суммарный ток в нагрузках дифференциального усилителя, т.е. режим усилителя, задается и стабилизируется токостабилизирующим транзистором 5, управляемым от шины управления 6 (как известно, сигнал на шине управления токостабилизирующим транзистором в дифференциальных усилителях в общем случае может быть либо постоянным, либо переменным; для формирования переменного сигнала на шине 6 в ячейке могут быть использованы различные устройства).

При равенстве напряжений на входах дифференциального усилителя на его выходах 32 и 33 устанавливается напряжение Uвыхо начального разбаланса этого усилителя, которое при накоплении (интегрировании) оптических сигналов на емкостях фотодиодов 9 и 10 будет суммироваться с полезным сигналом, усиливаемым дифференциальным усилителем. Величину Uвыхо можно существенно уменьшить, если скомпенсировать в нем влияние несимметрии пороговых напряжений усилительных транзисторов 1 и 2.

Достигается это в описываемом устройстве тем, что сигналы на входе дифференциального усилителя (напряжения на емкостях фотодиодов) после стирания при отсутствии сигнала записи, когда транзисторы 20, 21, 22 заперты, подвергаются дополнительной коррекции в соответствии с разбросом пороговых напряжений усилительных транзисторов 1 и 2. Для этой цели на затворы ключевых транзисторов 25, 26 и 27 подается по шине 28 сигнал балансировки (импульс напряжения), задний фронт которого задержан относительно заднего фронта сигнала стирания. Открытые каналы ключевых транзисторов 25 и 26 соединяют стоки и затворы усилительных транзисторов 1 и 2, у которых каналы сток-исток будут проводяшими, если напряжение на стоках превышает напряжение на истоках на величину Uпор соответствующего транзистора. В описываемом устройстве напряжение на истоках транзисторов 1 и 2 при наличии сигнала балансировки на шине 28 устанавливается через открытый канал ключевого транзистора 27 равным напряжению на шине смещения балансировки 29. Источниками напряжений на затворах транзисторов 1 и 2 будут заряды, запасенные емкостями 9 и 10 фотодиодов 7 и 8 во время стирания. Поэтому, если после стирания во время балансировки напряжения на затворах транзисторов 1 и 2 будут удовлетворять условиям U1 > Uпор1 + U29, U2 > Uпор2 + U29, где U1 и U2 напряжения на затворах транзисторов 1 и 2, Uпор1 и Uпор2 пороговые напряжения транзисторов 1 и 2, U29 напряжение на шине смещения балансировки, то емкости 9 и 10 фотодиодов 7 и 8 будут разряжаться до тех пор, пока каналы сток-исток транзисторов 1 и 2 будут проводящими, т.е. пока имеют место указанные условия. Таким образом, во время балансировки напряжения на затворах усилительных транзисторов 1 и 2 дифференциального усилителя ячейки, т.е. напряжения на емкостях фотодиодов перед началом накопления, устанавливаются в соответствии с напряжением на шине 29 и пороговыми напряжениями транзисторов 1 и 2, компенсируя тем самым разброс пороговых напряжения этих транзисторов и повышая дифференциальную чувствительность ячейки в целом.

При отсутствии сигнала записи на шине записи 28 каналы ключевых транзисторов записи 20, 21, 22 заперты, а ключевой транзистор записи 23 открыт (выходным сигналом с выхода инвертора 34 записи 23 открыт (выходным сигналом с выхода инвертора 34 сигнала записи). При этом конфигурация, состоящая из транзисторов 16, 17, 3, 4, образует статический триггер (транзистор 23 включает его питание), т.е. ячейку памяти с выходами 32 и 33. На время действия сигнала записи питание этого триггера отключается (канал транзистора 23 запирается) и на входах триггера 32 и 33 устанавливается дифференциальный сигнал от усиления дифференциальным усилителем дифференциального сигнала на емкостях 9 и 10 фотодиодов 7 и 8. Усиленный сигнал запоминается на паразитных емкостях выходов 32 и 33. По заднему фронту сигнала записи, когда каналы транзисторов записи 20, 21, 22 запираются, а канал транзистора записи 23 открывается, происходит срабатывание триггера в соответствии со знаком напряжения, установившегося на его входах (выходах фотоприемной ячейки 32 и 33) перед концом сигнала записи. Таким образом, производится компарирование сигнала дифференциального усилителя с фотодиодами на входах, его нормирование по уровню и запись в триггер.

Описываемое устройство в отличие от известных с реализацией аналогичных по назначению устройств сочетает высокую пороговую чувствительность при устойчивости к влиянию несимметрии параметров входящих в нее элементов и широкие функциональные возможности (позволяет, в частности, организовать конвейер по накоплению и обработке оптических данных: во время преобразования оптического сигнала может выполняться обработка данных, преобразованных и запомненных на предыдущем такте работы ячейки) с простотой ее схемы и минимальным количеством входящих в нее элементов.

Моделирование описанного устройства полностью подтвердило эффективность заложенного в нее принципа функционирования и возможности обеспечения повышенной пороговой чувствительности в условиях несимметрии и параметров используемых в ячейке элементов, а также перспективность ее применения в качестве элементарной ячейки интегральных фотоматричных БИС с оптическим входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Фотоприемная ячейка | 1989 |

|

SU1619345A1 |

| Фотоприемная ячейка | 1989 |

|

SU1626261A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| СЛЕДЯЩИЙ ФИЛЬТР-ПРОЦЕССОР ДЛЯ ОБРАБОТКИ СИГНАЛОВ ЛАЗЕРНОГО ДОПЛЕРОВСКОГО ИЗМЕРИТЕЛЯ СКОРОСТИ | 2000 |

|

RU2177159C1 |

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ КОРРЕКЦИИ ЭЛЕКТРОТЕРМИЧЕСКОЙ СВЯЗИ В БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2011 |

|

RU2462813C1 |

Изобретение относится к технической физике, а точнее к оптоэлектронике, к полупроводниковым приборам, чувствительным к излучению. Повышение пороговой чувствительности устройства достигается за счет введения в него ключевых транзисторов балансировки и ключевого транзистора записи. 1 ил.

ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ, содержащий первый усилительный транзистор, сток которого подключен к затвору второго усилительного транзистора, к затвору и истоку первого нагрузочного транзистора, сток второго и затвор первого усилительных транзисторов соединены с затвором и истоком второго нагрузочного транзистора, истоки первого и второго усилительных транзисторов с стоком первого ключевого транзистора записи, затвор которого подключен к стоку ключевого транзистора, к затвору и истоку третьего нагрузочного транзистора, третий и четвертый усилительные транзисторы, истоки которых соединены со стоком токостабилизирующего транзистора, стоки третьего и четвертого усилительных транзисторов подключены соответственно к истокам второго и третьего ключевых транзисторов записи, стоки которых соединены с затворами и истоками соответственно первого и второго нагрузочных транзисторов, затворы второго и третьего ключевых транзисторов записи и ключевого транзистора подключены к шине записи, стоки первого, второго и третьего нагрузочных транзисторов соединены с шиной питания, истоки ключевого транзистора и первого ключевого транзистора записи подключены к общей шине, первый и второй фотодиоды, которые одноименными выводами подключены к подложке, первый и второй ключевые транзисторы стирания, истоки которых соединены соответственно с первым и вторым фотодиодами, стоки с источником смещения фотодиодов, а затворы с шиной стирания, отличающийся тем, что в него введены ключевые транзисторы балансировки и четвертый ключевой транзистор записи, затвор которого подключен к шине записи, исток к общей шине, а сток к истоку токостабилизирующего транзистора, затвор которого соединен с шиной задания режима, затворы ключевых транзисторов балансировки подключены к шине балансировки, стоки первого и второго ключевых транзисторов балансировки соединены с истоками второго и третьего ключевых транзисторов записи соответственно, исток первого ключевого транзистора балансировки подключен к затвору третьего усилительного транзистора, к истоку первого ключевого транзистора стирания и к первому фотодиоду непосредственно, а через собственную емкость первого фотодиода к подложке, исток второго ключевого транзистора балансировки подключен к затвору четвертого усилительного транзистора, к истоку второго ключевого транзистора стирания и к второму фотодиоду непосредственно, а через собственную емкость второго фотодиода к подложке, исток третьего ключевого транзистора балансировки соединен со стоком токостабилизирующего транзистора, а сток третьего ключевого транзистора балансировки подключен к шине смещения балансировки.

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-12-20—Публикация

1992-12-18—Подача