( ФОРМИРОВАТЕЛЬ СИГНАЛОВ ВЫБОРКИ АДРЕСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств в интегральном исполнении /

Известно устройство для формирова-5 ния адресных сигналов, в котором адресные сигналы формируют с помощью инверторов t1,

Данное простейшее техническое решение определило, вследствие большой Ю емкости адресных шин, невысокое быстродействие устройства при сравнительно высокой потребляемой мощности, свойственной статическим схемам,

Известно также -устройство для фор- 5 мированчя адресных сигналов, в котором с целью увеличения быстродействия и уменьшения потребляемой мощности, для считывания адресной информации используются дифференциальные усилите- ° ли, а для формирования адресных си|- налов - динамические повторители, подключенные к каждому из плеч дифференциального усилителя. Использование Д Ф ; еренциальных усилителей позволяет с высокой скоростью (юрмировать на затворах динамических повторителей прямой и инверсный адресные сигналы, а использование динамических повторителей позволяет без потерь мощности в устройстве, установить информацию на адресных шинах 2,

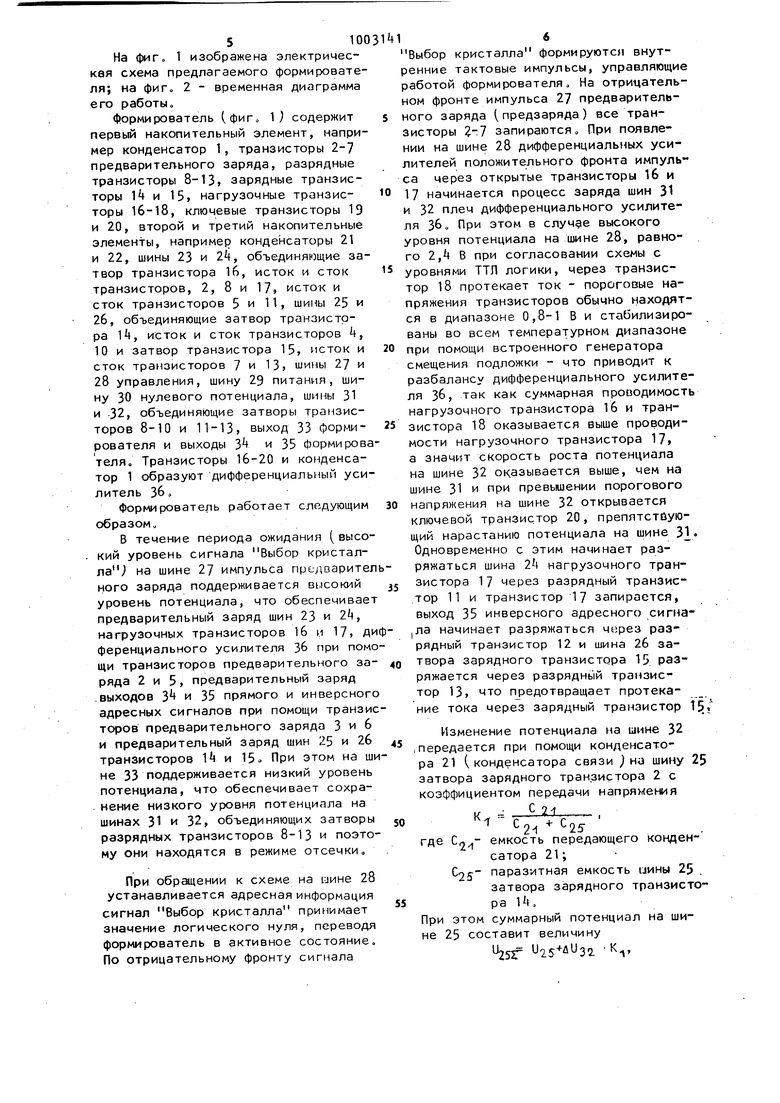

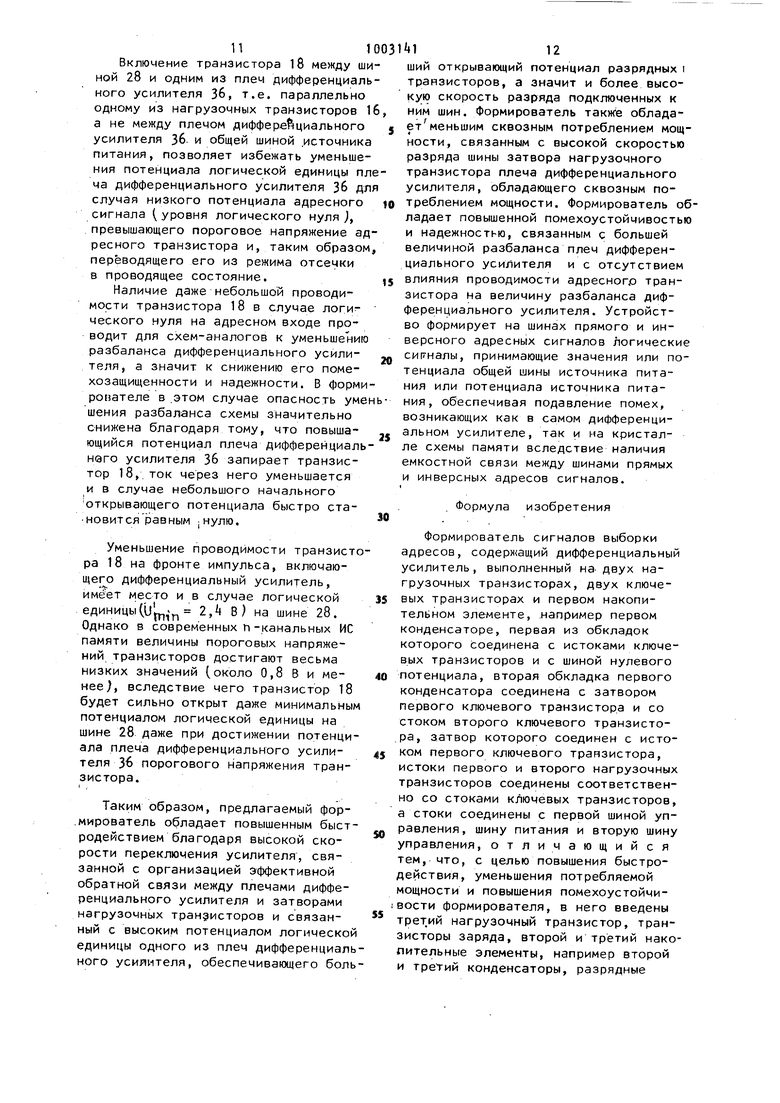

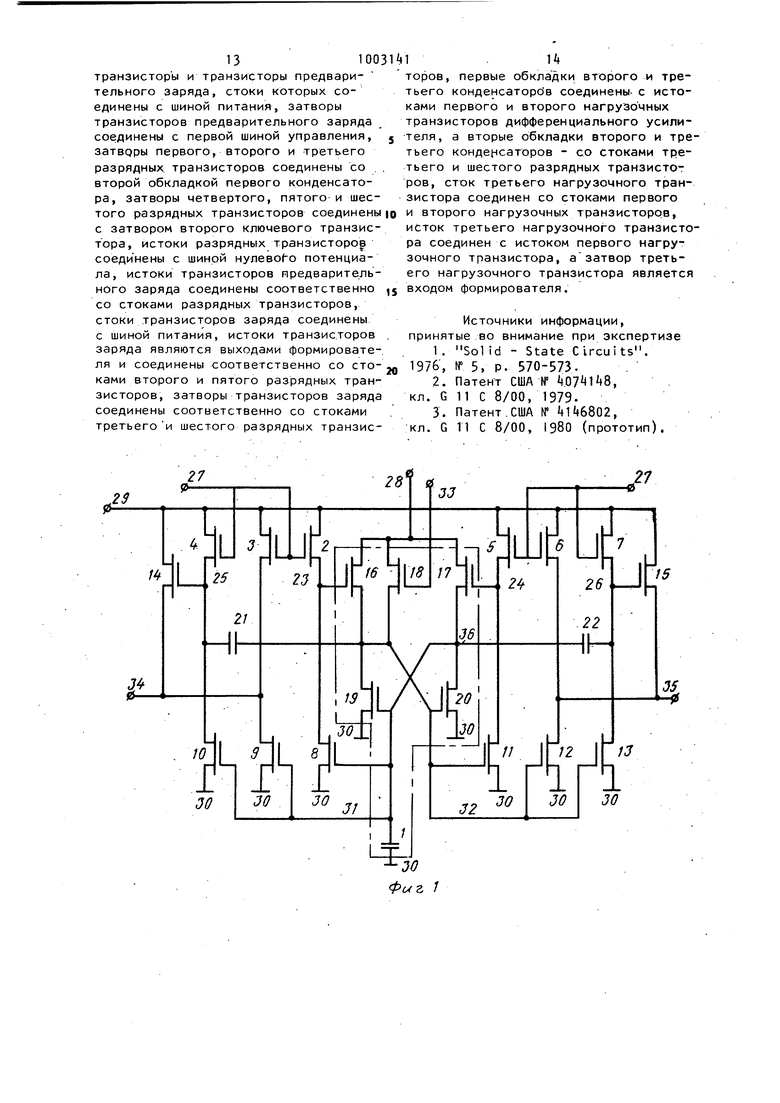

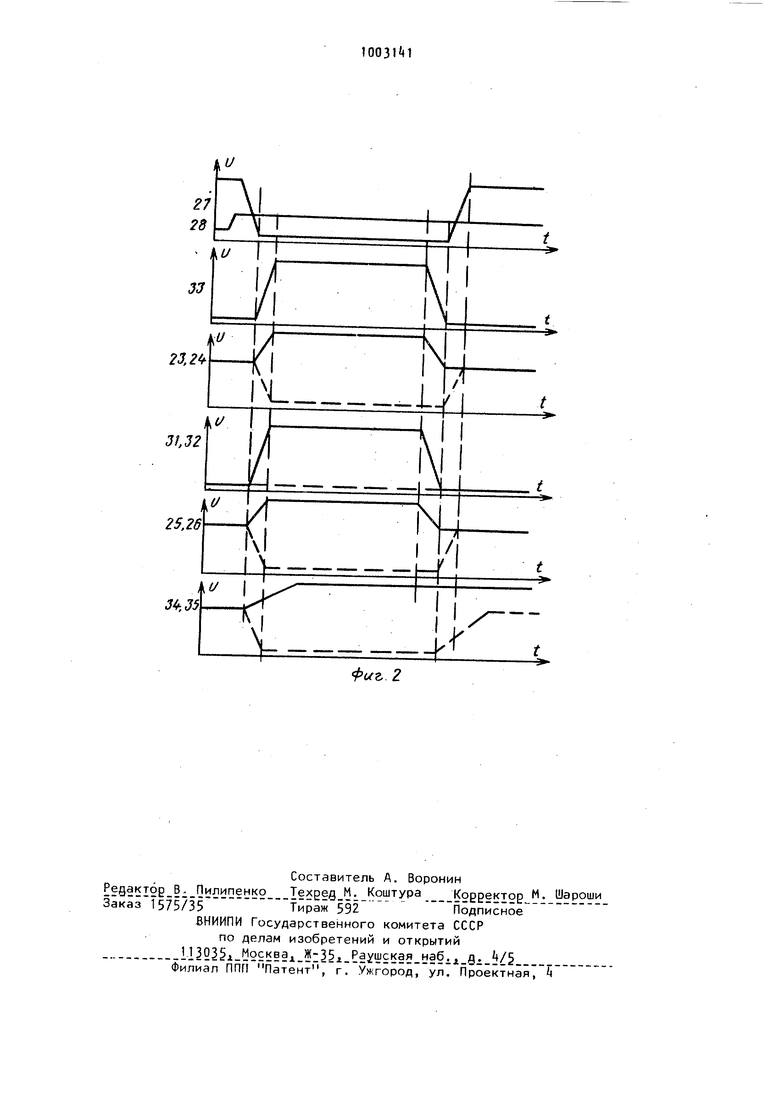

Однако известные устройства обладают рядом недостатков, во-пероых значительным сквозным потреблением мощности в одном из плеч дифсзеренци- . ального усилителя; во-вторых использование предзаряженных адресных шин приводит к пониженному потенциалу логической единицы на адресных шинах вследствие значительных трудностей получения потенциала импульса предзаряда, превышающего напряжение источника питания; в-третьих, о устройствах, использующих принцип предзаряда адресных шин или динамические, повторители для формирования адресных сигналов, при обращении к схеме памяти, одна из адресных шин каждого адресного каскада, не меняющая свой потенциал, оказывается отклочен ной от остальной части схемы, при этом из-за наличия значительной емкостной связи между адресными шинами, расположенными на кристалле параллельно друг другу с максимальной плотностью, изменение потенциала на переключающихся адресных шинах передается с некоторым коэффициентом передачи на адресные шины, отключенные от остальной части схемы, что мо жет привести к сбою в работе дещифратора адреса, управляемого адресным сигналами; в-четвертых, для устройства формирования, использующего динамические повторители для формиро вания адресных сигналов, тре()уется дополнительный импульс тактового пит ния, что усложняет схему буфера, а также синхронизацию работы его частей и уменьшает быстродействие схемы Наиболее близким по технической сущности к предлагаемому является формирователь сигналов выборки адресов, в котором благодаря предзаряду адресных шин обеспечивается высокая скорость работы схемы, а нагрузочные транзисторы дифференциального усилителя одновременно выполняют роль динамических повторителей, что наряду с использованием лишь двух импуль сов тактового питания упрощает схему буфера 3. Известный формирователь также обладает перечисленными выше недостатками, причем подключение шин прямого и инверсного адресных сигналов к затворам нагрузочных транзисторов дифференциального усилителя уменьшает э фективность работы нагрузочных транзисторов в качестве динамических повторителей вследствие значительной паразитной емкости адресных шин Цель изобретения - повышение быст родействия, уменьшение потребляемой мощности и повышение помехоустойчивости формирователя сигналов выборки адресов. Поставленная цель достигается тем что в формирователь сигналов выборки адресов, содержащий дифференциальный усилитель, выполненный на двух нагрузочных транзисторах, двух кгаочевых транзисторах и первом накопительном элементе, например первом крконденсвторе, перв.ая из обкладок ко-, торого соединена с истоками ключевых транзисторов и с шиной нулевого потенциала, вторая обкладка первого конденсатора соединена с затвором первог го ключевого транзистора и со стоком второго ключевого транзистора, затвор которого соединен с истоком первого ключевого тразистора, истоки первого и второго нагрузочных транзисторов соединены соответственно со стоками ключевых транзисторов, а стоки соединены с первой шиной управления, шину питания и вторую шину управления, введены третий нагрузочный транзистор, транзисторы заряда, второй и третий накопительные элементы, например, второй и третий конденсаторы, разрядные транзисторы и транзисторы предварительного заряда, стоки которых соединены с шиной питания, затворы транзисторов предварительного заряда соединены с первой шиной управления, затворы первого, второго и третьего разрядных транзисторов соединены со второй обкладкой первого конденсатора, затворы четоертого, пятого и шестого разрядных транзисторов соединены с затвором второго ключевого транзистора, истоки разрядных транзисторов соединены с шиной нулевого потенциала, истоки транзисторов предварительного заряда соединены соответственно со стоками разрядных транзисторов, стоки транзисторов заряда соединены с шиной питания, истоки транзисторов заряда являются выходами формирователя и соединены соответственно со стоками второго и пятого разрядных транзисторов, затворы транзисторов заряда соединены соответственно со стоками третьего и шестого разрядных транзисторов, первые обкладки второго и третьего конденсаторов соединены с истоками первого и второго нагрузочных транзисторов дифференциального усилителя, а вторые обкладки второго и третьего конденсаторов - со стоками третьего и шестого разрядных транзисторов, сток третьего нагрузочного транзистора соединен со стоками первого и второго нагрузочных транзисторов, исток третьего нагрузочного транзистора соединен с истоком первого нагрузочного транзистора, а затвор третьего нагрузочного транзистора является входом формирователя. На фиг. 1 изображена электрическая схема предлагаемого формирователя; на фиг„ 2 - временная диаграмма его работы формирователь (фиго U содержит первый накопительный элемент, например конденсатор 1, транзисторы 2-7 предварительного заряда, разрядные транзисторы 8-13 зарядные транзисторы 14 и 15 нагрузочные транзисторы 16-18, ключевые транзисторы 19 и 20, второй и третий накопительные элементы, например конденсаторы 21 и 22, шины 23 и 2k, объединянзщие затвор транзистора 16, исток и сток транзисторов, 2, 8 и 17 исток и сток транзисторов 5 и 11, шины 25 и 2б, объединяющие затвор транзистора 1, исток и сток транзисторов k, 10 и затвор транзистора 15, исток и сток транзисторов 7 и 13, шины 27 и 28 управления, шину 29 питания, шину 30 нулевого потенциала, шины 31 и -32, объединяющие затворы транзисторов 8-10 и 11-13 выход 33 формирователя и выходы Jk и 35 формирова теля. Транзисторы 16-20 и конденсатор 1 образуют дифференциальный усилитель Зб формирователь работает следующим образом В течение периода ожидания (высокий уровень сигнала Выбор кристалла на шине 27 импульса предварител ного заряда поддерживается высокий уровень потенциала, что обеспечивает предварительный заряд шин 23 и , нагрузочных транзисторов 16 и 17, ди ференциального усилителя 36 при помо щи транзисторов предварительного заряда 2 и 5, предварительный заряд .выходов 3 и 35 прямого и инверсного адресных сигналов при помощи транзис торов предварительного заряда 3 и 6 и предварительный заряд шин 25 и 2б транзисторов Т и 15 о При этом на ш не 33 поддерживается низкий уровень потенциала, что обеспечивает сохра. нение низкого уровня потенциала на шинах 31 и 32, объединяющих затворы разрядных транзисторов 8-13 и поэто му они находятся в режиме отсечки о При обрацении к схеме на шине 28 устанавливается адресная информация сигнал Выбор кристалла принимает значение логического нуля, переводя формирователь в активное состояние, По отрицательному фронту сигнала Выбор кристалла формируются внутенние тактовые импульсы, управляющие работой формирователя о На отрицательном фронте импульса 27 предварительного заряда (предзаряда ) все транзисторы запираются. При появлении на шине 28 дифференциальных усилителей положительного фронта импульса через открытые транзисторы 16 и 17 начинается процесс заряда шин 31 и 32 плеч дифференциального усилителя 36 о При этом в случае высокого уровня потенциала на шине 28, равного 2,А В при согласовании схемы с уровнями ТТЛ логики, через транзистор 18 протекает ток - пороговые напряжения транзисторов обычно находятся в диапазоне 0,8-1 В и стабилизированы во всем температурном диапазоне при помощи встроенного генератора смещения подложки - что приводит к разбалансу дифференциального усилителя Зб, так как суммарная проводимость нагрузочного транзистора 16 и транзистора 18 оказывается выше проводимости нагрузочного транзистора 17 а значит скорость роста потенциала на шине 32 оказывается выше, чем на шине 31 и при превышении порогового напряжения на шине 32 открывается ключевой транзистор 20, препятстйующий нарастанию потенциала на шине Одновременно с этим начинает разряжаться шина 2t нагрузочного транзистора 17 через разрядный транзистор 11 и транзистор 17 запирается, выход 35 инверсного адресного сигна|Ла начинает разряжаться через разрядный транзистор 12 и шина 26 затвора зарядного транзистора 15 разряжается через разрядный транзистор 13, что п редотвращает протекание тока через зарядный транзистор 15/ Изменение потенциала на шине 32 Iпередается при помощи конденсатора 21 (конденсатора связи jна шину 25 затвора зарядного транзистора 2 с коэффициентом передачи напряжения С 2-г 2-1 25 емкость передающего конденсатора 21; паразитная емкость иины 25 затвора зарядного транзистора 1ь При этом суммарный потенциал на шине 25 составит величину Uzsr . -К, где и,- исходный потенциал пины 25 затвора зарядного транзистора Н; величина изменения потенци ла в плече дифференциально усилителя 36. Величина коэффициента передачи н пряжения может варьироваться в широ ких пределах при помощи изменения г метрических размеров (а также и емкости МДП-конденсатора 21. Увеличение потенциала на шине 25 затвора зарядного транзистора Т пр ведет к его отпиранию и зарядит выход З прямого адресного сигнала от исходного потенциала (,например,Uoc Е - Vf , где Е - напряжение источни ка питания, VY - величина порогового напряжения транзистора до потенциала источника питания, при условии, что коэффициент передачи напряжения К выбран достаточно высоким и суммарный потенциал на шине.25 соста вит величину не менее ,f25r E- 4Заряд выхода 3ч при помощи зарядного транзистора Н предотвращает падение потенциала на адресной шине как за счет возможного паразитного всплеска потенциала на шине 31, так и за счет емкостной связи между выходом З и другими адресными шинами формирова телей. Изменение потенциала на шине 32 на положительном фронте импульса так тового питания передается на шину 23 затвора транзистора 16, причем его затвор: играет здесь роль передающего конденсатора. Благодаря низкой величине паразитной емкости шины 23 состоящей из емкости перекрытия за.твор-исток транзистора 2, емкости перекрытия затвор-сток разрядного транзистора 8 и емкости межсоединений, суммарный потенциал на шине 23 может превысить напряжение источника питания (если при этом достаточно велика емкость затвора нагрузочного транзистора J. . В случае низкого потенциала на шине 33, равного 0,8 В при согласовании схемы с уровнями ТТЛ логики, транзистор 18 заперт и ток через него равен нулю. Благодаря небольшой разнице в ширине каналов нагрузочных транзисторов, 16 и 17, дифференциальный усилитель 36 на фронте импульса тактового питания устанавливается в состояние, при котором шина 31 заряжена до высокого логического уровня. При этом разряжается шина 23 затвора нагрузочного транзистора 16 через разрядный транзисJOP разряжается также и выход З через разрядный транзистор 9, а шина 25 затвора зарядного транзистора разряжается через разрядный транзистор 10. Изменение потенциала на. шине 31 передается при помощи конденсатора 22 на шину 2б с коэффициентом передачи напряжения: С 22 . 22 -26 где С, емкость передающего конденсатора 22; паразитная емкость шины 2б затвора зарядного транзистора 15. Потенциал на шине 2б в результате превышает напряжение источника питания и происходит заряд выхода 35 инверсного адресного сигна/ а через зарядный транзистор 15. Для правильной работы дифференци-. ального усилителя 36 необходимо выполнить следующие условия: оба плеча дифференциального усилителя 36 ( шины 31 и 32) должны иметь одинаковую емкостн нагрузку, так что подключение истока транзистора 18 к одному из плеч дифференциального усилителя 36 должно быть компенсировано подключением конденсатора 1 эквивалентной емкости к другому плечу. Небольшая разница в ширине каналов нагрузочных транзисторов 16 и 17, обеспечивающая несколько большую проводимость нагрузочного транзистора 17, должна быть такова, что при низком уровне потенциала на шине 33 (транзистор 18 не проводит ) дифференциальный усилитель 36 устанавливается в такое состояние, что на шине 31 появляется высокий потенциал, а шина 32 остается при низком уровне потенциала и, при высоком уровне потенциала на шине 33 (транзистор 18 открыт), дифференциальный усилитель 36 устанавливается в противоположное состояние благодаря тому, что суммарная проводимость транзистора 16 и транзистора 18 выше, чем проводимость транзистора 17. После окончания сигнала Выбор кристалла происходит восстановление начального состояния формирования. На входе 28 тактового питания дифференциального усилителя 36 появляется низкий уровень потенциала, что приводит 9100 к разряду плеча дифференциального усилителя 36 заряженного при обращении к схеме, при этом потенциал на затворе нагрузочного транзистора этого плеча на отрицательном фронте тактового импульса уменьшится до исходного значения благодаря емкостной передаме , где роль передающего конденсатора будет выполнять затвор нагрузочного транзистора дифференциального усилителя. Изменение потенциала од ного из плеч дифференциального усилителя передается через конденсатор 21 или 22 на затвор одного из зарядных транзисторов, уменьшая ее потенциал до исходного значения. Появление высокого потенциала на шине 27 импуль са предзаряда, открывающего все транзисторы 2-7, происходит с небольшой задержкой относительно отрицательного фронта тактового импульса для пред отвращения сквозного потребления мощности в формирователе. Открытые импульсом 27 предзаряда транзисторы 2-7 предзаряда восстанавливают исходные потенциалы на шинах прямого и инверс ного адресных сигналов, на затворах зарядного транзистора и нагрузочного транзистора дифференциального усилителя Зб, разряженных при обращении к формирователю. При этом следует отметить, что ши на прямого или инверсного адресного сигнала, заряженная при обр131цении до потенциала источника питания, сохранит свой потенциал. Уменьшение этого потенциала до исходного может происходить лишь за счет токов утечки. Однако для дешифратора адреса (не по казан , управляемого предзаряженными адресными шинами, такая неопределенность потенциала адресных шин (этот потенциал будет лежать в пределах от Е до (E-VT) при потенциале шины 2 импульса предзаряда, равном напряжению источника питания ) не существенна, так как этот потенциал поддерживается не ниже определенного уровня (равного E-VTJ, запирающего адресные транзисторы дешифратора. В предлагаемом формирователе обес печиваемся высокая скорость разрядазатворов транзисторов 16 или 17 при обращении в том из пл.еч дифференциал ного усилителя Зб, где устанавливает ся низкое значение потенциала, благодаря тому, что паразитная емкость шин 23 и затворов нагрузочных транзисторов 16 и 17 мала и може 10 составить величину порядка 0,1-0,2 пф, тогда как в схеме-прототипе к затворам нагрузочных транзисторов подключены шины Прямого и инверсного адресных сигналов, емкость которых достигать величины пФ и более. Высокая скорость разряда затвора нагрузочного транзистора 16 или 17 дифференциального усилителя 36 обеспечивает минимальное время сквозного потребления мощности, так как сквозной ток в плече дифференциального усилителя 36 будет протекать лишь от начала положительного фронта импульса 33 тактового питания (точнее после превышения порогового напряженияпротивоположным плечом дифференциального усилителя) до разряда затвора нагрузочного транзистора 16 или 17 до потенциала, меньшего порогового напряжения транзистора. Низкая паразитная емкость шин 23 и 24 затворов нагрузочных транзисторов 16 и 17 обеспечивает высокий коэффициент передачи напряжения на шины 23 и на положительном фронте импульса 33 тактового питания, так что суммарное напряжение на одном из затворов транзисторов 16 или 17 превысит напряжение источника питания при достаточно больших геометрических размерах канала, и, следовательно, большой емкости затворов транзисторов 16 и Т7. Значительное увеличение проводимости одного из транзисторов 16 и 17 при эффективном подавлении потенциала затвора и, следовательно, уменьшении проводимости другого транзистора 17 на положительном фронте импульса шины 28 тактового питания приводит к увеличению разбаланса плеч дифференциального усилителя 36, а значит увеличению помехозащищенности формирователя. Повышенный потенциал одного из затворов транзисторов 16 или 17 дифференциального усилителя 36 позволяет заряжать одно из его плеч с большей скоростью и до потенциала, равного потенциалу источника питания. Это, в свою очередь, приводит к увеличению быстродействия формирователя, так как приводит к ускорению разряда шины прямого или инверсного адресных си| налов через соответствую(ций разрядный транзистор, затвор которого подключен к одному из плеч дифференциального усилителя Зб. n Включение транзистора l8 между ш ной 28 и одним из плеч дифференциал ного усилителя Зб, т.е. параллельно одному из нагрузочных транзисторов а не между плечом дифференциального усилителя Зб. и общей шиной источник питания, позволяет избежать уменьше ния потенциала логической единицы пл ча дифференциального усилителя 36 дл случая низкого потенциала адресного сигнала ( уровня логического нуля ), превышающего пороговое напряжение ад ресного транзистора и, таким образом переводящего его из режима отсечки в проводящее состояние. Наличие даже небольшой проводимости транзистора 18 в случае логического нуля на адресном входе проводит для схем-аналогов к уменьшению разбаланса дифференциального усилителя, а значит к снижению его помехозащищенности и надежности. В форми рователе в .этом случае опасность уме шения разбаланса схемы значительно снижена благодаря тому, что повышающийся потенциал плеча дифференциаль ного усилителя 36 запирает транзистор 18,. ток через него уменьшается и в случае небольшого начального открывающего потенциала быстро становится равным Нулю. Уменьшение проводимости транзисто ра 18 на фронте импульса, включающего дифференциальный усилитель, имёет место и в случае логической единицы(и, 2,k В) на шине 28. Однако в современных п-канальных ИС памяти величины пороговых напряжений транзисторов до.стигают весьма низких значений (около 0,8 В и менее), вследствие чего транзистор 18 будет сильно открыт даже минимальным потенциалом логической единицы на шине 28 даже при достижении потенциала плеча дифференциального усилителя 36 порогового напряжения транзистора. Таким образом, предлагаемый фор,мирователь обладает повышенным быстродействием благодаря высокой скорости переключения усилителя, связанной с организацией эффективной обратной связи между плечами дифференциального усилителя и затворами нагрузочных транзисторов и связанный с высоким потенциалом логической единицы одного из плеч дифференциаль ного усилителя, обеспечивающего боль ший открывающий потенциал разрядных i транзисторов, а значит и более высокую скорость разряда подключенных к ним шин. Формирователь такжё обладаетменьшим сквозным потреблением мощности, связанным с высокой скоростью разряда шины затвора нагрузочного транзистора плеча дифференциального усилителя, обладающего сквозным потреблением мощности. Формирователь обладает повышенной помехоустойчивостью и надежностью, связанным с большей величиной разбаланса плеч дифференциального усилителя и с отсутствием влияния проводимости адресногр транзистора на величину разбаланса дифференциального усилителя. Устройство формирует на шинах прямого и инверсного адресных сигналов логические сигналы, принимающие значения или потенциала общей шины источника питания или потенциала источника питания, обеспечивая подавление помех, возникающих как в самом дифференциальном усилителе, так и на кристалле схемы памяти вследствие наличия емкостной связи между шинами прямых и инверсных адресов сигналов. Формула изобретения Формирователь сигналов выборки адресов, содержащий дифференциальный усилитель, выполненный на двух нагрузочных транзисторах, двух ключевых транзисторах и первом накопительном элементе, .например первом конденсаторе, первая из обкладок которого соединена с истоками ключевых транзисторов и с шиной нулевого потенциала, вторая обкладка первого конденсатора соединена с затвором первого клю.чевого транзистора и со стоком второго ключевого транзистора, затвор которого соединен с истоком первого ключевого транзистора, истоки первого и второго нагрузочных транзисторов соединены соответственно со стоками ключевых транзисторов, а стоки соединены с первой шиной управления, шину питания и вторую шину управления, отличающийся тем, что, с целью повышения быстродействия, уменьшения потребляемой мощности и повышения помехоустойчивости формирователя, в него введены трет.ий нагрузочный транзистор, транзисторы заряда, второй и третий накопительные элементы, например второй и третий конденсаторы, разрядные

13ЮО

транзисторы и транзисторы предварительного заряда, стоки которых соединены с шиной питания, затворы транзисторов предварительного заряда соединены с первой шиной управления, затврры первого, второго и третьего разрядных транзисторов соединены со . второй обкладкой первого конденсатора, затворы четвертого, пятого и шестого разрядных транзисторов соединены с затвором второго ключевого транзистора, истоки разрядных транзисторе соединены с шиной нулевого потенциала, истоки транзисторов предварительного заряда соединены соответственно со стоками разрядных транзисторов, стоки транзисторов заряда соединены с шиной питания, истоки транзисторов заряда являются выходами формирователя и соединены соответственно со стоками второго и пятого разрядных транзисторов, затворы транзисторов заряда соединены соответственно со стоками третьего и шестого разрядных транзис1 - U торов, первые обкладки второго и третьего конденсаторбв соединены- с истоками первого и второго нагрузочных транзисторов дифференциального усилителя, а вторые обкладки второго и третьего конденсаторов - со стоками третьего и шестого разрядных транзистот ров, сток третьего нагрузочного транзистора соединен со стоками первого и второго нагрузочных транзисторов, исток третьего нагрузочного транзистора соединен с истоком первого нагрузочного транзистора, азатвор третьего нагрузочного транзистора является входом формирователя.

Источники информации, принятые во внимание при экспертизе

:кл. G 11 С 8/00, 1980 (прототип).

фиг. 2

Авторы

Даты

1983-03-07—Публикация

1981-09-22—Подача