В отличие от известных схем сумматоров, предлагаемая схема параллельного действия обеспечивает вдвое меньшее время суммировання двух кодов по сравнению со схемой однотактного сумматора.

Схема достаточно проста как по построению, так и по управлению.

Новизна предлагаемого устройства заключается в использовании запоминающих свойств ферриттранзисторных элементов для создания простой схемы хранения импульсов, а также для выполнения цепи сквозного переноса.

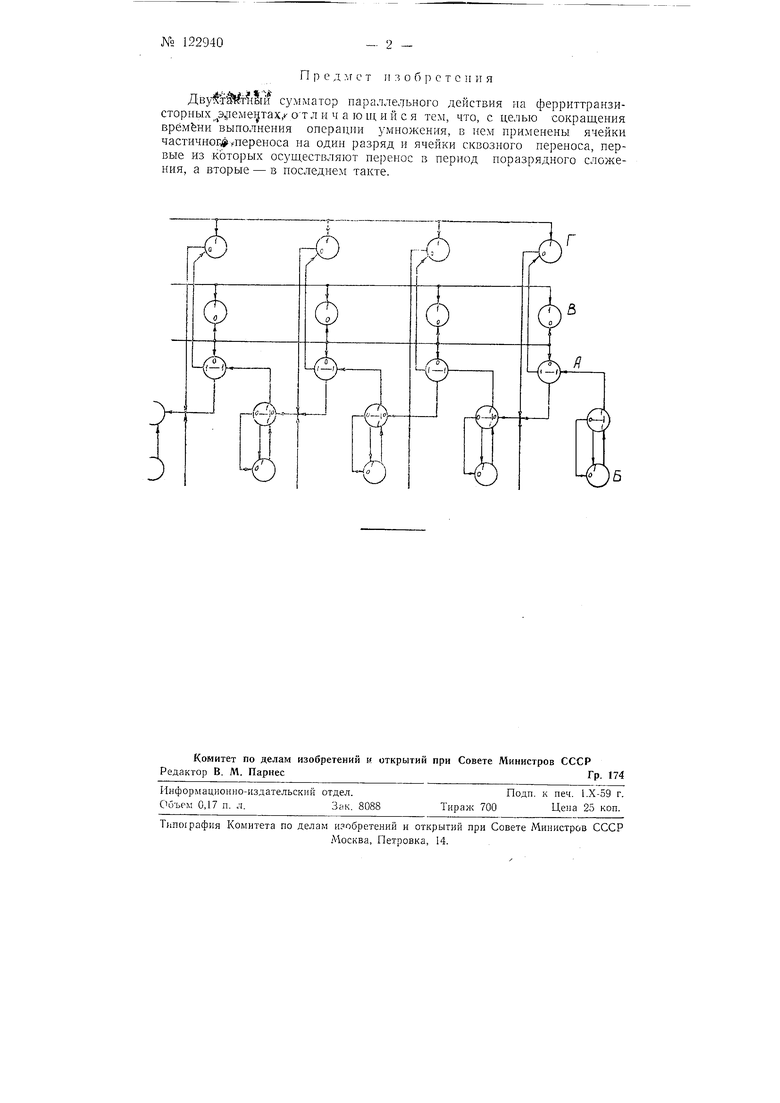

Устройство состоит из суммирующих элементов, выполиенных на однотактных триггерах, и ячеек сквозного и частичного переноса. Сложение чисел производится за два такта: в первом такте производится частичный перенос на один разряд непосредственно после сложения, во втором такте производится сквозной перенос.

При умножении чисел сквозной перенос производится после всех сложений, что существенно сокращает время выполнения операции.

Принцип работы сумматора показан на чертеже. В нижние кольца ячеек тактового переноса А поступают единицы переноса с триггеров Б. Эти импульсы записываются верхними кольцами вентилей В.

При подаче на вентили списываюп;его тактового импульса сигнал переноса с выхода вентиля поступает в следующий разряд. На этом операция частичного переноса заканчивается, и в сумматор снова подается следующий, код числа, и все операции повторяются. После окончания поступления суммирующих кодов производится сквозной перенос через ряд ячеек Г.

Таким образом, частота суммирования при умножении не ограничивается временем полного сквозного переноса и зависит только от скорости работы ячеек, что особенно важно при большой частоте суммирования и большом числе разрядов.

Пред м с т и : о б р с т с н и я

Дву тМт1{ыи сзмматор параллельного действия на ферриттранзисторных ,3.iieMe Tax,отл и ч а ю ш, и и с я тем, что, с целью сокращения времени выполнения операции умножения, в нем применены ячейки частичног,в «переноса на один разряд и ячейки сквозного переноса, первые из которых осуществляют перенос в период поразрядного сложения, а вторые - в последнем такте.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки команд из долговременного запоминающего устройства | 1961 |

|

SU151119A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ НА ФЕРРИТ-ТРАНЗИСТОРНЫХЯЧЕЙКАХ | 1967 |

|

SU203320A1 |

| Устройство для умножения | 1988 |

|

SU1580352A1 |

| Устройство для умножения | 1987 |

|

SU1425659A1 |

| Конвейерный сумматор | 1989 |

|

SU1714588A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

Авторы

Даты

1959-01-01—Публикация

1958-12-10—Подача