Изобретение относится к вычислительной технике, в частности к устройствам для умножения, и может быть использовано прл построении арифмети- ческих устройств электронных вычислительных машин.

Целью изобретения является сокращение количества оборудования устройства.

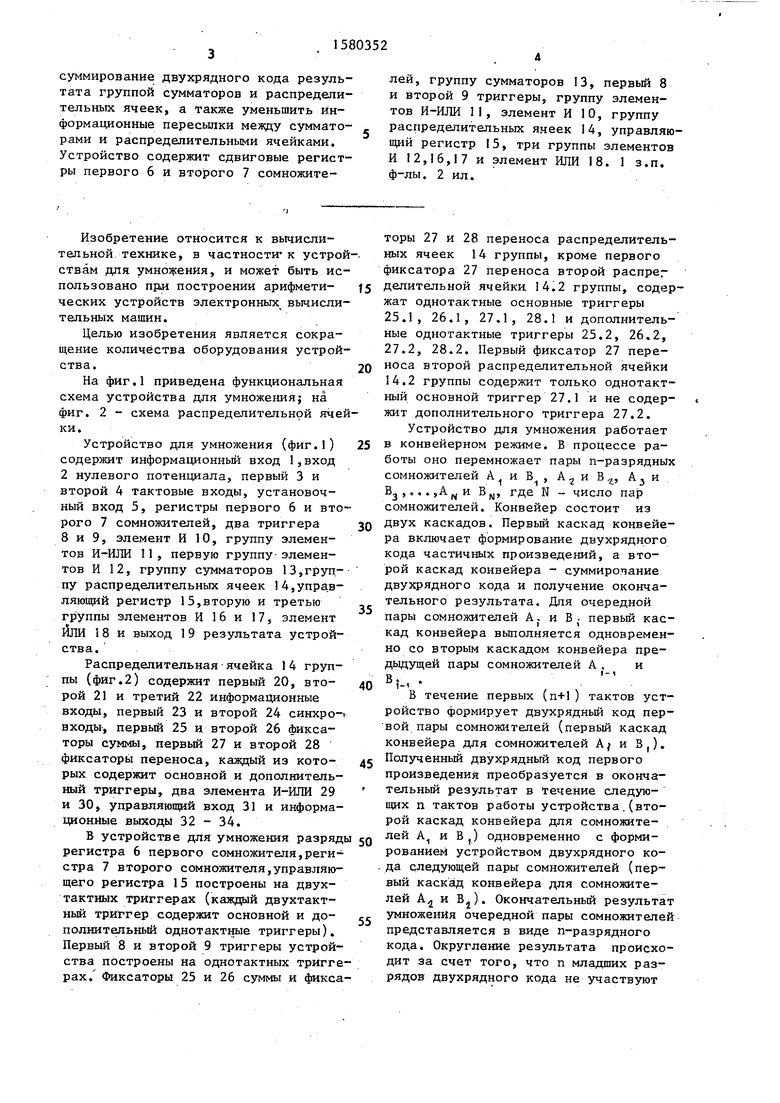

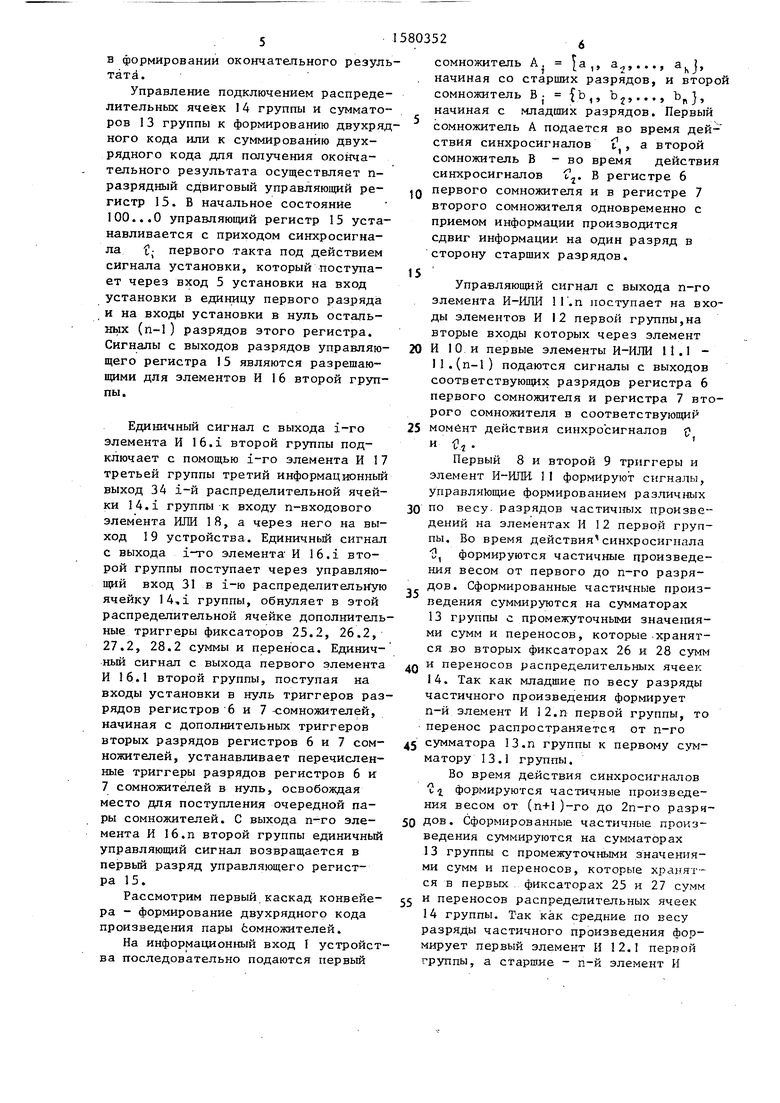

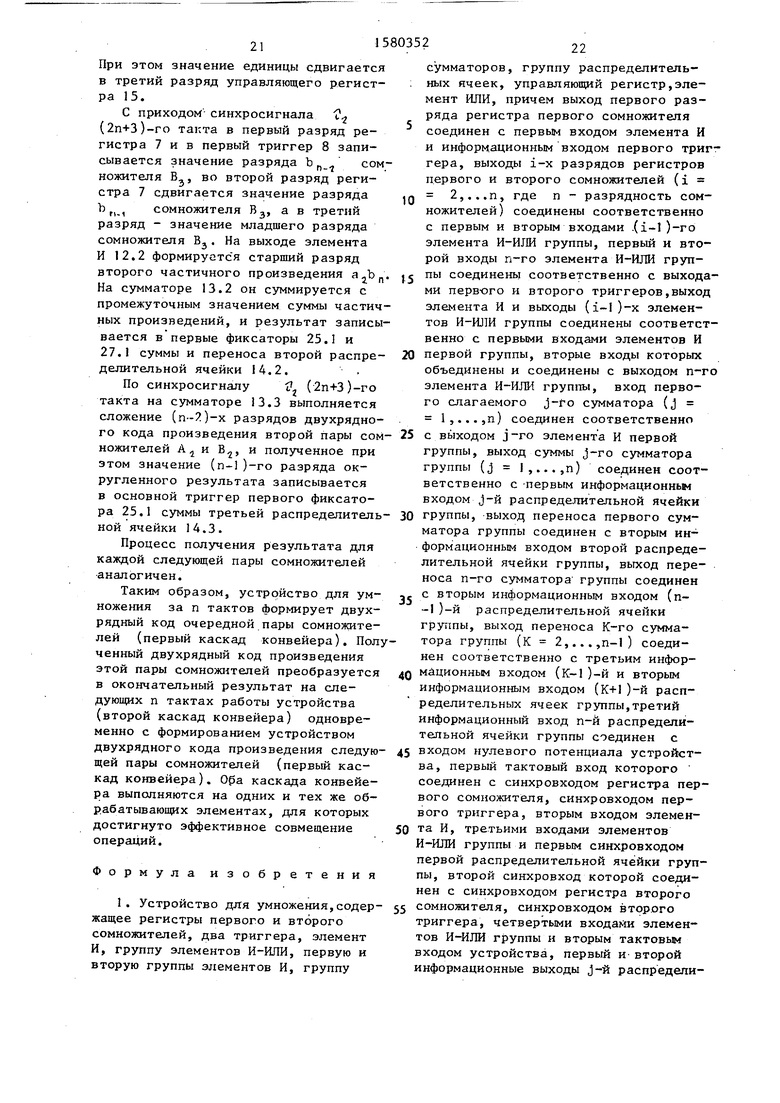

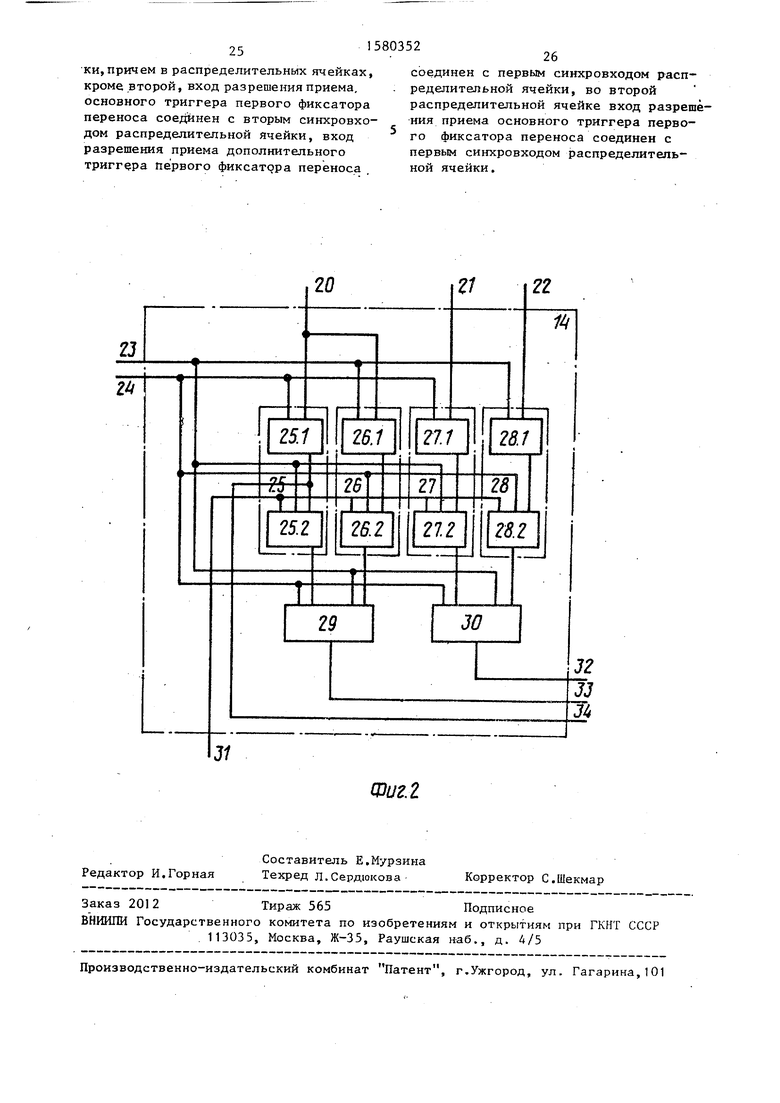

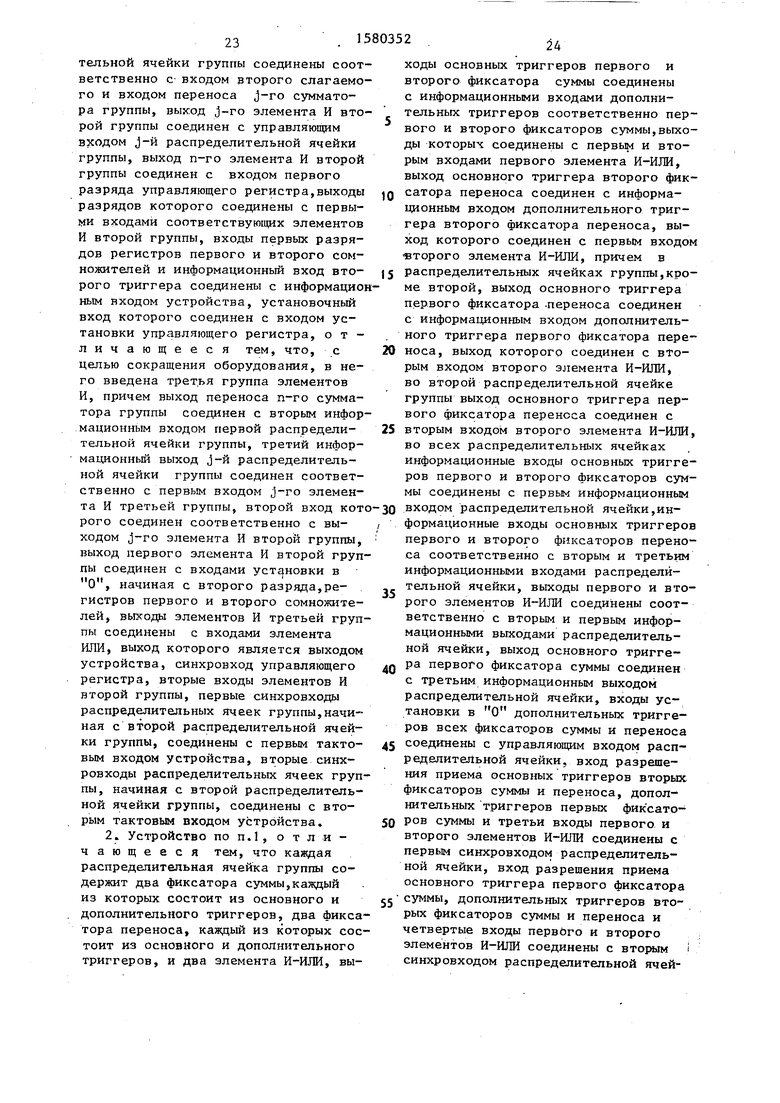

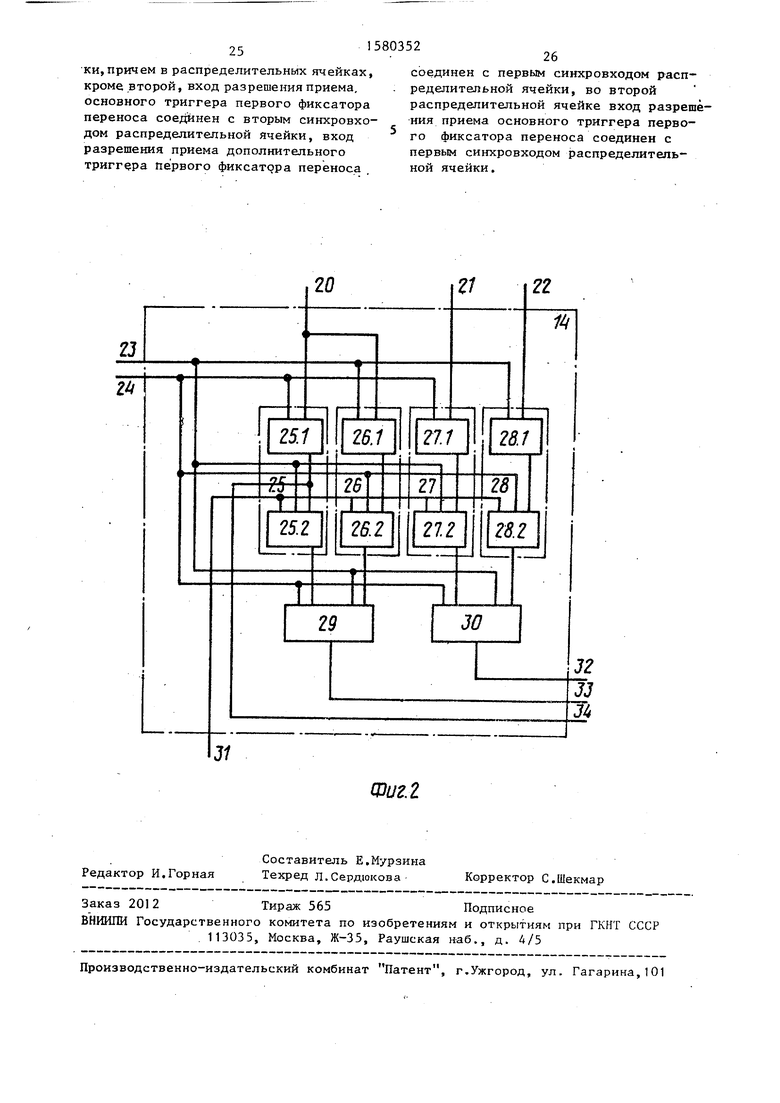

На фиг.1 приведена функциональная схема устройства для умножения; на фиг. 2 - схема распределительной ячейки.

Устройство для умножения (фиг.1) содержит информационный вход 1,вход 2 нулевого потенциала, первый 3 и второй 4 тактовые входы, установочный вход 5, регистры первого 6 и второго 7 сомножителей, два триггера 8 и 9, элемент И 10, группу элементов И-ИЛИ 11, первую группу элементов И 12, группу сумматоров 13,группу распределительных ячеек 34,управляющий регистр 15,вторую и третью группы элементов И 16 и 17 s элемент ИЛИ 18 и выход 19 результата устройства.

Распределительная ячейка 14 группы (фиг.2) содержит первый 20, вто- рой 21 и третий 22 информационные входы, первый 23 и второй 24 синхро- входы, первый 25 и второй 26 фиксаторы суммы, первый 27 и второй 28 фиксаторы переноса, каждый из кото- рых содержит основной и дополнительный триггеры, два элемента И-ИЛИ 29 и 30, управляющий вход 31 и информационные выходы 32 - 34.

В устройстве для умножения разряды регистра 6 первого сомножителя,регистра 7 второго сомножителя,управляющего регистра 15 построены на двухтактных триггерах (каждый двухтактный триггер содержит основной и до- полнительный однотактные триггеры). Первый 8 я второй 9 триггеры устройства построены на однотактных триггерах. Фиксаторы 25 и 26 суммы и фикса

5

0

5 0

0 д5

50 с г

5

торы 27 и 28 переноса распределительных ячеек 14 группы, кроме первого фиксатора 27 переноса второй распрег делительной ячейки 14.2 группы, содержат однотактные основные триггеры

25.1,26.1, 27.1, 28.1 и дополнительные однотактные триггеры 25.2, 26.2,

27.2,28.2. Первый фиксатор 27 переноса второй распределительной ячейки 14.2 группы содержит только однотакт- ный основной триггер 27.1 и не содер- « жит дополнительного триггера 27.2.

Устройство для умножения работает в конвейерном режиме. В процессе работы оно перемножает пары п-разрядных сомножителей АиВ, А2иВ, АЭИ В.,...,Ами BN, где N - число пар сомножителей. Конвейер состоит из двух каскадов. Первый каскад конвейера включает формирование двухрядного кода частичных произведений, а второй каскад конвейера - суммирование двухрядного кода и получение окончательного результата. Для очередной пары сомножителей А. и В- первый каскад конвейера выполняется одновременно со вторым каскадом конвейера предыдущей пары сомножителей А . и

ч

В течение первых (п+1) тактов устройство формирует двухрядный код первой пары сомножителей (первый каскад конвейера для сомножителей AJ и В,). Полученный двухрядный код первого произведения преобразуется в окончательный результат в течение следующих п тактов работы устройства.(второй каскад конвейера для сомножителей А1 и В() одновременно с формированием устройством двухрядного кода следующей пары сомножителей (первый каскад конвейера для сомножителей А и В.). Окончательный результат умножения очередной пары сомножителей представляется в виде п-разрядного кода. Округление результата происходит за счет того, что п младших разрядов двухрядного кода не участвуют

в формировании окончательного результата.

Управление подключением распределительных ячеек 14 группы и сумматоров 13 группы к формированию двухрядного кода или к суммированию двухрядного кода для получения окончательного результата осуществляет п- разрядный сдвиговый управляющий регистр 15. В начальное состояние 100...О управляющий регистр 15 устанавливается с приходом синхросигнала Ј первого такта под действием сигнала установки, который поступает через вход 5 установки на вход установки в единицу первого разряда и на входы установки в нуль остальных (п-1) разрядов этого регистра. Сигналы с выходов разрядов управляющего регистра 15 являются разрешающими для элементов И 16 второй группы.

Единичный сигнал с выхода i-ro элемента И 16.1 второй группы подключает с помощью 1-го элемента И 17 третьей группы третий информационный выход 34 1-й распределительной ячейки 14.1 группы к входу п-входового элемента ИЛИ 18, а через него на выход 19 устройства. Единичный сигнал с выхода 1-тго элемента И 16.1 второй группы поступает через управляющий вход 31 в i-ю распределительную ячейку 14,1 группы, обнуляет в этой распределительной ячейке дополнительные триггеры фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса. Единичный сигнал с выхода первого элемента И 16.1 второй группы, поступая на входы установки в нуль триггеров разрядов регистров 6 и 7 -сомножителей, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7 сомножителей, устанавливает перечисленные триггеры разрядов регистров 6 к 7 сомножителей в нуль, освобождая место для поступления очередной пары сомножителей. С выхода n-го элемента И 1б.п второй группы единичный управляющий сигнал возвращается в первый разряд управляющего регистра 15.

Рассмотрим первый каскад конвейера - формирование двухрядного кода произведения пары сомножителей.

На информационный вход I устройства последовательно подаются первый

сомножитель

А, - I.

a-i 3 К j

начиная со старших разрядов, и второй сомножитель В- {b,, bz,..., bn, начиная с младших разрядов. Первый сомножитель А подается во время дей- ствия синхросигналов i , а второй сомножитель В - во время действия синхросигналов С. В регистре 6 первого сомножителя и в регистре 7 второго сомножителя одновременно с приемом информации производится сдвиг информации на один разряд в сторону старших разрядов.

5

Управляющий сигнал с выхода п-го

элемента И-ИЛИ 11.п поступает на входы элементов И 12 первой группы,на вторые входы которых через элемент

0 И 10 и первые элементы И-ИЛИ 11.1 - ll.(n-l) подаются сигналы с выходов соответствующих разрядов регистра 6 первого сомножителя и регистра 7 второго сомножителя в соответствующий

5 момент действия синхросигналов Ј и Ј7 .

Первый 8 и второй 9 триггеры и элемент И-ИЛИ 11 формируют сигналы, управляющие формированием различных

0 по весу разрядов частичных произведений на элементах И 12 первой группы. Во время действия4синхросигнала

3, формируются частичные произведения весом от первого до n-го разрядов. Сформированные частичные произведения суммируются на сумматорах 13 группы с промежуточными значениями сумм и переносов, которые хранятся во вторых фиксаторах 26 и 28 сумм

и переносов распределительных ячеек 14. Так как младшие по весу разряды частичного произведения формирует n-ri элемент И 12.п первой группы, то перенос распространяется от п-го

сумматора I3.n группы к первому сумматору 13.1 группы.

Во время действия синхросигналов i формируются частичные произведения весом от (п+1)-го до 2п-го разряД°в. Сформированные частичные произведения суммируются на сумматорах

13группы с промежуточными значениями сумм и переносов, которые хранятся в первых фиксаторах 25 и 27 сумм

и переносов распределительных ячеек

14группы. Так как средние по весу разряды частичного произведения формирует первый элемент И 12.1 первой группы, а старшие - n-й элемент И

12.п первой группы, то перенос распространяется от первого сумматора 13.1 группы к n-му сумматору 13.п группы.

При работе первого каскада конвейера в качестве исходной информации для обработки выступают два сомножителя А- и В,- . При работе второго каскада конвейера исходной информацией для обработки выступают два слагаемых - двухрядный код суммы частичных произведений и переноса.

В то время, когда часть сумматоров 13 групцы занята суммированием формируемых частичных произведений, другая, не занятая в этом процессе оставшаяся часть сумматоров 13 группы выполняет суммирование двухрядного кода - второй каскад конвейера. Чтобы разряды регистров 6 и 7 сомножителей не оказывали влияние на второй каскад конвейера, производится их периодическое обнуление, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7 сомножителей.

Обнуление разрядов при суммировании двухрядного кода производится при помощи элементов И 16 второй группы, на первые входы- которых поступают синхросигналы

, а на вторые - сигналы с выходов соответствующих разрядов управляющего регистра 15. В момент поступления синхросигнала 2, нулевой сигнал с выхода элемента И 16 второй группы закрывает элемент И 17 третьей группы.Единичный сигнал с выхода элемента И 16 второй группы обнуляет дополнительные триггеры фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса , соответствующей распределительной ячейки 14 группы в момент перезаписи информации из основных триггеров. Округление п младших разрядов выполняется их отбрасыванием, так как выходы соответствующих им вторых фиксаторов 26 сумм не подключены к выходу устройства.

Первые фиксаторы 25.1- сумм распределительных ячеек 14 группы после поступления в них старших разрядов результата, подключаются к выходу устройства для вывода результата, причем информация подается с выхода основных триггеров первых фиксаторов 25.1 сумм через третий информационный выход 34 распределительной ячейки. Элементы И 16 второй группы и управляющий регистр 15 периодически подключают третьи информационные выходы 34 соответствующих распределительных ячеек 14 группы через элементы И 17 третьей группы к элементу ИЛИ 18 и выходу 19 устройства.

Устройство работает следующим об- разом.

В исходном состоянии триггеры и регистры устройства обнулены.С приходом синхросигнала , первого такта на вход 5 устройства подается 5 сигнал установки, который устанавливает управляющий регистр 15 в начальное состояние, т.е. в состояние 1000...0. По синхросигналу С первого такта в первый разряд регистра Q 6 записывается значение старшего разряда а , сомножителя А1, а с приходом синхросигнала Ј первого такта в первый разряд регистра 7 и в первый триггер 8 записывается значение млад- 5 шего разряда Ъп сомножителя В .

В течение первого такта на сумматорах 13 суммируется нулевая информация регистров 6 и 7 и дополнительных триггеров фиксаторов 25 - 28 суммы 0 и переноса распределительных ячеек 14. Со следующего такта для первой пары сомножителей А и В ч начинается первый каскад конвейера.

Во время действия синхросигнала , ,, второго такта в первый разряд регистра 6 записывается значение разряда сомножителя А, во второй разряд регистра 6 и во второй триггер 9 сдвигается значение разря- Q да а1 сомножителя А,. На выходе элемента И 12.1 формируется первое частичное произведение а.Ъ . На сум II

маторе 13.1 оно суммируется с нулевым значением суммы частичных произ- 45 ведений и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительной ячейки 14.1 в качестве промежуточного зна- чения суммы частичных произведений.

По синхросигналу

второго

такта с выхода первого разряда управляющего регистра 15 через первый элемент И 16.1 второй группы проходит единичный управляющий сигнал на первый вход первого элемента И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки 14.1 , и входы установки в нуль триггеров разрядов регистров 6 и 7, начиная с

дополнительных триггеров вторых разрядов регистров 6 и 7. Под действием единичного управляющего сигнала с выхода основного триггера первого фиксатора 27.1 переноса первой распределительной ячейки 14.1 через третий информационный выход 34 этой распределительной ячейки, первый элемент И 17.1 третьей группы, элемент ИЛИ 18 проходит нулевая информация на выход 19 устройства. Одновременно с этим производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса первой распределительной ячейки 14.1 и, начиная с дополнительного триггера второго разряда регистра, триггеров регистров 6 и 7, а значени единицы сдвигается во второй разряд управляющего регистра 15,

Во время действия синхросигнала

I второго такта в первый разряд регистра 7 и в первый триггер 8 записывается значение разряда Ъ„ , сомножителя В., , во второй разряд регистра 7 сдвигается значение разряда bfl сомножителя Bt.

По синхросигналу { третьего такта в первый разряд регистра 6 записывается значение разряда а„ сомножителя AJ, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а 4 сомножителя А(, в третий разряд регистра 6 сдвигается значение разряда а, сомножителя А1. На выходе элементов И 12. и 12.2 первой группы формируются младшие разряды второго частичного произведения а 4Ъ „., , а 1 Ъ „, первой пары сомножителей А1 и В,. На сумматорах 13.1 и 13.2 они суммируются с промежуточным значением суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.1 и 14.2.

Во время действия синхросигнала

О, третьего такта с выхода второго разряда управляющего регистра 15 единичный управляющий сигнал поступает через второй элемент И 16.2 второй группы на первый вход второго элемента И 17.2 третьей группы. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы второй распределительной ячейки 14.2 на выход 19 устройства поступает ну

левая информация, прошедшая через третий информационный выход 34 второй распределительной ячейки 14.2,второй элемент И 17.2 третьей группы, элемент ИЛИ 18. Одновременно с этими действиями производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса второй распределительной ячейки 14.2, на входы установки в нуль которых единичный сигнал поступает через управляющий вход 31 распределительной ячейки 14.2. При этом значе5 ние единицы сдвигается в третий разряд управляющего регистра 15.

По синхросигналу Ј третьего такта в младший разряд регистра 7 и в первый триггер 8 записывается значе0 ние разряда Ъ сомножителя В ; во второй разрэд регистра 7 сдвигается

значение разряда Ъ

П-1

сомножителя

В, а в третий разряд - значение младшего разряда Ъ„ сомножителя В .

На выходе элемента И 12.2 формируется старший разряд второго частичного произведения . На сумматоре 13.2 оно суммируется с промежуточным значением суммы частичных произведений,

и результат .записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса второй распределительной ячейки 14.2.

С помощью синхросигнала Ј,(1+1)- го такта в первый разряд регистра 6

1 ««

записывается значение разряда а сомножителя А, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а

сомножителя At, в третий разряд - значение

разряда а ,-., сомножителя А,, в каждый следующий до (i+1)-го разряда регистра 6 сдвигается значение предыдущего разряда сомножителя А 1 в (1+1)-и

разряд регистра 6 сдвигается значение разряда а, сомножителя А,. На выходе элементов И 12.1 - 12.1 первой группы формируются младшие разряды частичных произведений: а,Ь п. (/,

а(Ъ „ (,,) - На сумматорах 13.1 - 13.1 они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.2 и 28.1 суммы и переноса распределительных ячеек 14.1 - 14.1.

Во время действия синхросигнала С, (i+l)-ro такта с выхода 1-го разряда управляющего регистра 15 единич

ный управляющий сигнал поступает через i-й элемент И 16.1 второй группы на первый вход 1-го элемента И 17.1 третьей группы. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы 1-й распределительной ячейки 14.1 на выход 19 устройства поступает нулевая информация, прошедшая через третий информационный выход 34 1-й распределительной ячейки 14.1, 1-й элемент И 17.1 третьей группы, элеме нт ИЛИ 18. Одновременно с этим действием производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса 1-й распределительной ячейки 14.1, на входы установки в нуль которых единичный сигнал поступает через управляющий вход 31 распределительной ячейки 14.1. При этом значение единицы сдвигается в (1+1)-й разряд управляющего регистра 15.

С приходом синхросигнала )- го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение разряда b n -4i j сомножителя В , в каждый следующий до (1+1)- го разряда регистра 7 сдвигается значение поступивших в предыдущих тактах разрядов сомножителя В , в (1+ +1 )-й разряд регистра 7 сдвигается значение разряда Ъп сомножителя В.. На выходе элементов И 12.2-12.1 первой группы формируются старшие разряды различных по весу частичных произведений а ,-Ь „. (.ц, а fb „ На сумматорах 13.2-13.1 они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.2-14.1.

По синхросигналу С, n-го такта в первый разряд регистра 6 записывается значение младшего разряда а сомножителя А , во второй разряд регистра 6 и второй триггер 9 сдви

гается значение разряда а

n-i

сомножителя А , в каждый следующий разряд сдвигается значение предыдущего разряда сомножителя А , в n-й разряд регистра 6 сдвигается значение разряда а сомножителя А,. На выходе элементов И 12.1-12.(п-1) формируются младшие разряды различных по весу разрядов частичных произведений

а11э1. an-ibf Ha сумматорах 13.1- 13.tn-l) они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14,1-14.(п-1 ).

Во время действия синхросигнала 1}л n-го такта с выхода (п-1 )-го разряда управляющего регистра 15 единичный управляющий сигнал поступает через (п-1)-й элемент И 16.(n-l) второй группы на первый вход (п-1)-го

5 элемента И 17.(n-l) третьей группы. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы (п-1)-й распределительной ячейки

0 14.(п-1) на выход 19 устройства поступает информация, прошедшая через третий информационный выход 34 распределительной ячейки 14.(n-l), (п-1)-й элемент И 17.(п-1) третьей

5 группы, элемент ИЛИ 18. Одновременно с этими действиями производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса (п-1)-й распредели0 тельной ячейки 14.(п-1). При этом значение единицы сдвигается в n-й разряд управляющего регистра 15.

По синхросигналу Ј. n-го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение

5

0

старшего разряда Ъ сомножителя В., в каждый следующий разряд регистра 7 сдвигается значение предыдущего разряда сомножителя В в n-й разряд регистра 7 сдвигается значение младшего разряда Ъ сомножителя В1. На выходе элементов И 12.2 - 12.(п-1)

первой группы формируются старшие разряды различных по весу разрядов частичных произведений а пи b г,...,

п

,,. На сумматорах 13.2

13.(п-1) они суммируются соответственно со значениями промежуточной суммы частичных произведений и,- результат записывается в лервые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.2 - 14.(п-1).

В следующем такте начинается ввод второй пары сомножителей, а для первой пары сомножителей А, и В заканчивает работу первый каскад конвейера.

С приходом синхросигнала $

л

(п+1)-го такта в первый разряд регистра 6 записывается значение старшеработу второй каскад конвейера, а для второй пары сомножителей А и В2 начинает работать первый каскад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1425659A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Устройство для суммирования частичных произведений | 1988 |

|

SU1580354A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для умножения , и может быть использовано при построении арифметических устройств электронных вычислительных машин. Устройство для умножения содержит регистры первого и второго сомножителей, два триггера, элемент И, группу элементов И-ИЛИ, первую и вторую группы элементов И, группу сумматоров, группу распределительных ячеек, управляющий регистр, элемент ИЛИ. С целью сокращения оборудования в устройство введена третья группа элементов И. Каждая распределительная ячейка группы содержит два фиксатора суммы, каждый из которых состоит их основного и дополнительного триггеров, два фиксатора переноса, каждый из которых состоит из основного и дополнительного триггера и два элемента И-ИЛИ. 2 ил.

о разряда а - сомножителя AZ. Одно- конвейера.

5

С приход + 2)-го т стра 6 зап да а2 сом ряд регист сдвигается ножителя А И 12.1 фор произведен

временно с выхода n-го разряда управ ляющего регистра 15 единичный управляющий сигнал поступает через п-й элемент И 16.п второй группы на первый вход n-го элемента И 17.п третьей группы, а также на вход первого разряда управляющего регистра 15. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы n-й распределительной ячейки 14.п на выход 19 устройства поступает нулевая информация,прошедшая через третий информационный выход 34 n-й распределительной ячейки 14.П, n-й элемент И 17.п третьей группы, элемент ИЛИ 18. В это же время производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28,2 суммы и переноса n-й распределительной ячейки 14.п. При этом значение единицы сдвигается в первый разряд управляющего регистра 15.

Во время действия синхросигнала С (п+1)-го такта на выходах элементов И 12 первой группы формируются младшие разряды частичных произведений предыдущей пары сомножителей А и В п: а Ъ4 ,.. . , а ,Ь п. На сумматорах 13 они суммируются соответственно со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.

С приходом синхросигнала i(n + + 1 )-го такта в первый разряд регистра 7 и в первый триггер 8 записываются значения младшего разряда Ьр сомножителя B.J.

Во время действия синхросигнала t 4 (п+1 )-го такта на выходах элементов И 12 формируются старшие разряды частичных произведений предыдущей пары сомножителей: а,Ът,...а пЬ1 . На сумматорах 13 они суммируется соответственно со значениями промежуточной суммы частичных произведений, результат записывается в первые фиксаторы 25.1 и 27.1 суммы и перекоса распределительных ячеек 14.

Со следующего такта для первой пары сомножителей А1 и В, начинает

конвейера.

5

0, (п +

10

15

С приходом синхросигнала + 2)-го такта в первый разряд регистра 6 записывается значение разряда а2 сомножителя А., во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда ач сомножителя А 2. На выходе элемента И 12.1 формируется первое частичное произведение я.Ъ . На сумматоре

п

20 в качестве промежуточного значения суммы частичных произведений.

Одновременно с этим с выхода первого разряда управляющего регистра 15 через первый элемент И 16.1 вто25 рой группы единичный управляющей

сигнал поступает на первый вход первого элемента И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки 14.1 и входы уста30 новки в нуль триггеров разрядов регистров 6 и 7, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7. Под действием.этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 27.1 переноса первой распределительной ячейки 14.1 через третий информационный выход 34 этой распределительной ячейки, iicpiif/f; элемент И 17.1 третьей грукпы, элемент ИЛИ 18 проходит нулевая информация на вход 19 устройства. В это же время производится обнуление дополнительных триггеров фиксаторов 25,2, 26.2, 27.2, 28.2 суммы и переноса ь.. ;чиЛ распределительной ячейки 14.1 и,начиная с дополнительного триггера второго разряда регистра, обнуляются триггеры регистров 6 и 7. При этом

5Q значение единицы сдвигается во второй разряд управляющего регистра 15.

С приходом синхросигнала (п + + 2)-го такта в первый разряд регистра 7 и в первый триггер 8 записывает,. ся значение разряда Ъ п сомножителя В, во второй разряд регистра 7 сдвигается значение разряда Ъ 1} сомножителя В.2. По синхросигналу 3 (п+2)-го такта на сумматоре 13.2 сум40

45

мируются (п-1)-е разряды двухрядного кода произведения первой пары сомножителей АЧ и Bf, и получаемое при этом значение n-го разряда округленного результата записывается в основной триггер первого фиксатора 25.1 суммы второй распределительной ячейки 14.2.

Со следующего такта начинается вывод n-разрядного округленного про- изведения первой пары сомножителей А. и В..

С приходом синхросигнала

(п +

+ 3)-го такта в первый разряд регист- J5 pa 6 записывается значение разряда а- сомножителя А, во второй разряд

регистра 6 и второй триггер 9 сдвигается значение разряда а7 сомножителя А, , в третий разряд регистра 6

V2

сдвигается значение разряда а, сомножителя А 2. На выходе элементов И 12.1 и 12.2 формируются младшие разряды второго частичного произведения: а-2Ъп-1 п-1 На сумматорах 13.1 и 13.2 они суммируются с промежуточным значением суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.1 и 14.2.

Во время действия синхросигнала tl1 (n+3)-ro такта с выхода второго разряда управляющего регистра 15 единичный управляющий сигнал поступает через второй элемент И 16.2 второй группы на первый вход второго элемента И 17.2 третьей группы и на управляющий вход 31 второй распределительной ячейки 14.2. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы второй распределительной ячейки 14.2 на выход 19 устройства поступает значение n-го разряда произведения первой пары сомножителей А и В. Одновременно производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса второй распределительной ячейки 14.2. При этом значение единицы сдвигается в третий разряд управляющего регистра 15.

С приходом синхросигнала 2 (п+3)-го такта в первый разряд регистра 7 и в первый триггер 8 записываются значения разряда сомножителя Ва, во второй разряд регистра

Ъ

7 сдвигается значение разряда

сомножителя В,

М-1

разряд - значение младшего Ъ„ сомножителя В„ . На

а в третий разряда эле

5

0

мента И 12.2 формируется старший разряд второго частичного произведения а2Ъп. На сумматоре 13.2 он суммируется с промежуточным значением суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса второй распределительной ячейки 14.2.

По синхросигналу 2(п+3)-го такта на сумматоре 13.3 выполняется сложение (п-2)-х разрядов двухрядного кода произведения первой пары сомножителей А и В и полученное при этом значение (п-1 )то,разряда округленного результата записывается в основной триггер первого сЬиксатора 25.1 суммы третьей распределительной ячейки 14.3.

5 Аналогичные действия выполняются устройством для умножения в течение следующих тактов работы. Особенностью 2п-го такта является получение сразу двух разрядов результата - второго

0 и первого как значение суммы и переносов. По синхросигналу Ј 2п-го такта в первый разряд регистра 6 записывается значение разряда ап сомножителя А, во второй разряд регистра 6 и второй триггер 9 сдвигается

5

0

5

0

5

значение разряда л „, сомножителя А , в каждый следующий разряд сдвигается значение предыдущего разряда сомножителя А, в n-й разряд регистра 6 сдвигается значение разряда а , сомножителя А 2. На выходе элементов И 12.1 - 12. (п-1) формируются младшие разряды различных по весу разрядов частичных произведений: ,..., ап, Ъ. На сумматорах 13.1 - 13.(п-1) они суммируются со значениями промежуточной суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.1 - 14.(п-1). Во время действия синхросигнала , 2п-го такта с выхода (п-1)-го разряда управляющего регистра 15 единичный управляющий сигнал поступает через (п-1)-й элемент И 16.(п-1) второй группы на первый вход (п-1)- го элемента И 17.(п-1) третьей группы. Под действием этого единичного

управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы (п-1)-й распределительной ячейки 14;(п-1) на выход 19 устройства поступает значение третьего разряда произведения первой пары сом ножителеи А, и В1 . Одновременно производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28,2 суммы и переноса (n- l )-й распределительной ячейки 14,(n-l). При этом значение единицы сдвигается в разряд управляющего регистра 15.

По синхросигналу 02 2п-го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение старшего разряда b сомножителя Вл в каждый следующий разряд регистра 7 сдвигается значение предыдущего разряда сомножителя В, в п-й разряд регистра 7 сдвигается значение младшего разряда Ъ п сомножителя Ва. На выходе элементов И 12.2 - 12.(п-1) первой группы формируются старшие разряды различных по весу разрядов частичных произведений а п, b-г,..., ). На сумматорах 13.2-13.(п-1) они складываются соот ветственно со значениями промежуточной суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.2 14.(п - 1).

Во время действия синхросигнала г 2п-го такта на сумматоре 13.п выполняется сложение старших разрядов двухрядного кода произведения первой пары сомножителей АП и В,, и полученные при этом значения второго и первого разрядов округленного результата записываются соответственно в основной триггер первого фиксатора 25.1 суммы n-й распределительной ячейки 14.п и в основной триггер первого фиксатора 27.1 переноса первой распределительной ячейки 14.1.

Со следующего такта начинается ввод и устройство третьей пары сомножителей А3 и Вл. Для второй пары сомножителей А2 и В2 заканчивается первый каскад конвейера.

С приходом синхросигнала ,(2п+ +1)-го такта в первый разряд регистра 6 записывается значение старшего разряда ад сомножителя А 3. На

выходах элементов И 12 первой группы формируются младшие разряды частичных произведении предыдущей пары сомножителей А, и В2: а „Ьт ,... ,а„Ъп. На сумматорах 13 они суммируются соответственно со значениями промежуточной суммы частичных произведений, и результат записывается во вто10 рые фиксаторы 26.1 и 28.1 суммы и переноса распределительных ячеек 14.

Во время действия синхросигнала D1 (2n+l)-ro такта с выхода п-го разряда управляющего регистра I5

J5 единичный управляющий сигнал поступает через n-й элемент И I6.n второй группы на первый вход n-го элемента И 17.п третьей группы, а также на вход первого разряда управляющего

20 регистра 15. Под действием этого единичного управляющего сигнала с выхода основного триггера первого фиксатора 25.1 суммы n-й распределительной ячейки 14.п на выход 19 устройств

25 поступают значения второго разряда округленного произведения первой пары сомножителей А и В1. Одновременно производится обнуление дополнительных триггеров фиксаторов 25,2, 30 26.2, 27.2, 28.2 суммы и переноса

n-й распределительной ячейки I4.n с помощью единичного сигнала,прошедшего через управляющий вход 31 п-й распределительной ячейки. При этом

а- значение единицы сдвигается в первый разряд управляющего регистра 15.

С приходом синхросигнала 2 (2п+1)-го такта в первый разряд регн-4Q стра 7 и в первый триггер 8 записывается значение младшего разряда сомножителя В3. Во время действия синхросигнала 2г (2n+l)-ro такта на входах элементов И I2 формируют45 ся старшие разряды различных, по весу разрядов частичных произведений предыдущей пары сомножителей А г и В7 : а ,Ъ „ . . . , anb, . На сумматорах 13.2 - 13.п они суммируются соответ50 ственно со значениями промежуточной суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса распределительных ячеек 14.2 - 14.п.

ее На первом сумматоре 13.1 значение первого разряда произведения первой пары сомножителей AJ и В1 суммируется с нулевой информацией и перезаписывается в основной триггер перво19

1580352

го фиксатора 25.1 суммы первой распределительной ячейки 14.1.

Со следующего такта для третьей пары сомножителей АЗ и В3 начинается первый каскад конвейера, для второй пары сомножителей А1 и В начинается второй каскад конвейера. Для первой пары сомножителей А и В заканчивается вывод результата.

Во время действия синхросигнала 21 (2п+2)-го такта первый разряд регистра 6 записывается в значении разряда аг сомножителя АЗ, во второй разряд регистра 6 и во второй триггер 9 сдвигается значение разряда а, сомножителя А 3. На выходе элементов И 12.1 формируется первое частичное произведение . На сумматоре 13.1 оно суммируется с нулевым значением суммы частичных произведений, и результат записывается во вторые фиксаторы 26.1 и 28.1 суммы и переносов распределительной ячейки 14.1 в качестве промежуточного значения суммы частичных произведений.

По синхросигналу такта с выхода первого разряда упfi(2n+2)-ro

равляющего регистра 15 единичный уп- 30 сомножителя АЗ. На выходе элементов

И 12.1 и 12.2 формируются младшие разряды второго частичного произведе ния ajb , а., . На сумматорах

равляющии сигнал поступает через первый элемент И 16.1 второй группы на первый вход первого элемента И 17.1 третьей группы, управляющий вход 31 первой распределительной ячейки 14.1 и входы установки в нуль триггеров разрядов регистров 6 и 7, начиная с дополнительных триггеров вторых разрядов регистров 6 и 7.Под действием единичного управляющего сигнала с выхода основного триггера первого фиксатора 27.1 суммы первой распределительной ячейки 14,1 через третий информационный выход 34 этой распределительной ячейки, первый элемент И 17.1 третьей группы, элемент ИЛИ 18 на выход 19 устройства поступает старший разряд произведения первой пары сомножителей А1 и В . В это время производится обнуление дополнительных триггеров фиксаторов 25.2, 26.2, 27.2, 28.2 суммы и переноса первой распределительной ячейки 14,1 и, начиная с дополнительного триггера разряда регистра, обнуляются триггеры регистров 6 и 7, При этом значение единицы сдвигается ро второй разряд управляющего регистра 15.

20

Во время действия синхросигнала г (2п+2)-го такта в первый разряд регистра 7 и первый триггер 8 записывается значение разряда Ъ ft , сомножителя В,, во второй разряд регистра 7 сдвигается значение разряда Ъп сомножителя В .

По синхросигналу у (2п+2)-го такта на сумматоре 13.2 суммируются (п-1)-е разряды двухрядного кода произведения второй пары сомножителей А7 и В2, и получаемое при этом значение n-го разряда округленного результата записывается в основной триггер первого фиксатора 25.1 суммы второй распределительной ячейки 14.2. Закончен вывод произведения первой пары сомножителей. Со следующего такта начинается вывод произведения второй пары сомножителей.

С приходом синхросигнала (2п+3)-го такта в первый разряд регистра 6 записывается значение разря- 5 да аэ сомножителя А, во второй разряд регистра 6 и второй триггер 9 сдвигается значение разряда а сомножителя АЭ, в третий разряд регистра 6 сдвигается значение разряда а.

5

0

5

0

И 12.1 и 12.2 формируются младшие разряды второго частичного произведения ajb , а., . На сумматорах

Во время действия синхросигнала Јл (2п+3)-го такта с выхода второго разряда управляющего регистра 15 единичный управляющий сигнал поступает через второй элемент И 16.2 вто5 Р°й группы на первый вход второго элемента И 17.2 третьей группы и на управляющий вход 31 второй распределительной ячейки 14.2. Под действием этого единичного управляющего сиг-

0 нала с выхода основного триггера первого фиксатора 25.1 суммы второй распределительной ячейки 14.2 на выход 1 9 устройства поступает значение n-го разряда произведения второй па5 ры сомножителей Аг и В2. Одновременно производится обнуление дополнительных триггеров фиксаторов 25.2,

При этом значение единицы сдвигается в третий разряд управляющего регистра 15.

С приходом синхросигнала (2п+3)-го такта в первый разряд регистра 7 и в первый триггер 8 записывается значение разряда Ъп ножителя В-, во второй разряд регистра 7 сдвигается значение разряда Ъ .. . сомножителя В а, а в третий

сомразряд - значение младшего разряда сомножителя В3. На выходе элемента И 12.2 формируется старший разряд второго частичного произведения На сумматоре 13.2 он суммируется с промежуточным значением суммы частичных произведений, и результат записывается в первые фиксаторы 25.1 и 27.1 суммы и переноса второй распределительной ячейки 14.2.

По синхросигналу г (2п+3)-го такта на сумматоре 13.3 выполняется сложение (п-)-х разрядов двухрядного кода произведения второй пары сомножителей А и В2, и полученное при этом значение (п-1)-го разряда округленного результата записывается в основной триггер первого фиксатора 25.1 суммы третьей распределительной ячейки 14.3.

Процесс получения результата для каждой следующей пары сомножителей аналогичен.

Таким образом, устройство для умножения за п тактов формирует двухрядный код очередной пары сомножителей (первый каскад конвейера). Полченный двухрядный код произведения этой пары сомножителей преобразуется в окончательный результат на следующих п тактах работы устройства (второй каскад конвейера) одновременно с формированием устройством двухрядного кода произведения следующей пары сомножителей (первый каскад конвейера). Оба каскада конвейера выполняются на одних и тех же обрабатывающих элементах, для которых достигнуто эффективное совмещение операций.

Формула изобретения

10

15

20

сумматоров, группу распределительных ячеек, управляющий регистр,элемент ИЛИ, причем выход первого разряда регистра первого сомножителя соединен с первым входом элемента И и информационным входом первого триггера, выходы 1-х разрядов регистров первого и второго сомножителей (i 2,...п, где п - разрядность сомножителей) соединены соответственно с первым и вторым входами (i-1)-го элемента И-ИЛИ группы, первый и второй входы n-го элемента И-ИЛИ группы соединены соответственно с выходами первого и второго триггеров,выход элемента И и выходы (i-l)-x элементов И-ИЛИ группы соединены соответственно с первыми входами элементов И первой группы, вторые входы которых объединены и соединены с выходом п-го элемента И-ИЛИ группы, вход первого слагаемого j-ro сумматора (J 1,...,п) соединен соответственно

25 с выходом j-ro элемента И первой группы, выход суммы j-ro сумматора группы (j I,...,n) соединен соответственно с первым информационным входом j-й распределительной ячейки группы, выход переноса первого сумматора группы соединен с вторым информационным входом второй распределительной ячейки группы, выход переноса n-го сумматора группы соединен с вторым информационным входом (п- -1)-й распределительной ячейки группы, выход переноса К-го сумматора группы (К 2,...,n-l) соединен соответственно с третьим информационным входом (К-1)-й и вторым информационным входом (К+1)-й распределительных ячеек группы,третий информационный вход n-й распределительной ячейки группы соединен с

45 входом нулевого потенциала устройства, первый тактовый вход которого соединен с синхровходом регистра первого сомножителя, синхровходом первого триггера, вторым входом элемента И, третьими входами элементов

30

35

40

50

И-ИЛИ группы и первым синхровходом первой распределительной ячейки группы, второй синхровход которой соединен с синхровходом регистра второго сомножителя, синхровходом второго триггера, четвертыми входами элементов И-ИЛИ группы и вторым тактовым входом устройства, первый и второй информационные выходы J-й распределительной ячейки группы соединены соответственно с входом второго слагаемого и входом переноса j-ro сумматора группы, выход j-ro элемента И второй группы соединен с управляющим входом j-й распределительной ячейки группы, выход n-го элемента И второй группы соединен с входом первого разряда управляющего регистра,выходы разрядов которого соединены с первыми входами соответствующих элементов И второй группы, входы первых разрядов регистров первого и второго сомножителей и информационный вход вто- рого триггера соединены с информационным входом устройства, установочный вход которого соединен с входом установки управляющего регистра, отличающееся тем, что, с целью сокращения оборудования, в него введена третья группа элементов И, причем выход переноса n-го сумматора группы соединен с вторым информационным входом первой распредели- тельной ячейки группы, третий информационный выход j-й распределительной ячейки группы соединен соответственно с первым входом j-ro элемента И третьей группы, второй вход входом распределительной ячейки,инрого соединен соответственно с вы- ходом j-ro элемента И второй группы, выход первого элемента И второй группы соединен с входами установки в О, начиная с второго разряда,регистров первого и второго сомножителей, выходы элементов И третьей группы соединены с входами элемента ИЛИ, выход которого является выходом устройства, синхровход управляющего регистра, вторые входы элементов И второй группы, первые синхровходы распределительных ячеек группы,начиная с второй распределительной ячейки группы, соединены с первым тактовым входом устройства, вторые синхровходы распределительных ячеек группы, начиная с второй распределительной ячейки группы, соединены с вторым тактовым входом устройства.

5

0

5

0

5

формационные входы основных триггеров первого и второго фиксаторов переноса соответственно с вторым и третьим информационными входами распределительной ячейки, выходы первого и второго элементов И-ИЛИ соединены соответственно с вторым и первым информационными выходами распределительной ячейки, выход основного триггера первого фиксатора суммы соединен с третьим информационным выходом распределительной ячейки, входы установки в О дополнительных триггеров всех фиксаторов суммы и переноса соединены с управляющим входом распределительной ячейки, вход разрешения приема основных триггеров вторых фиксаторов суммы и переноса, дополнительных триггеров первых фиксаторов суммы и третьи входы первого и второго элементов И-ИЛИ соединены с первым синхровходом распределительной ячейки, вход разрешения приема основного триггера первого фиксатора суммы, дополнительных триггеров вторых фиксаторов суммы и переноса и четвертые входы первого и второго элементов И-ИЛИ соединены с вторым i синхровходом распределительной ячейки,причем в распределительных ячейках, кроме второй, вход разрешения приема, основного триггера первого фиксатора переноса соединен с вторым синхровхо- дом распределительной ячейки, вход разрешения приема дополнительного триггера Первого фиксатора переноса

соединен с первым синхровходом распределительной ячейки, во второй распределительной ячейке вход разрешения приема основного триггера первого фиксатора переноса соединен с первым синхровходом распределительной ячейки.

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1987 |

|

SU1425659A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-12-19—Подача