Известны нараллельные накапливающие сумматоры со сквозным переносом на ферриттранзисторных ячейках, содержащие триггеры, ячейки сквозного переноса и логические схемы обращения кода.

Предлагаемый сумматор отличается тем, что в нем выходы ячеек сквозного переноса каждого предыдущего разряда подключены ко входам схем обращения кода следующих разрядов, осуществляющих задержку поразрядных переносов.

Это позволяет сократить число элементов, повысить надежность устройства.

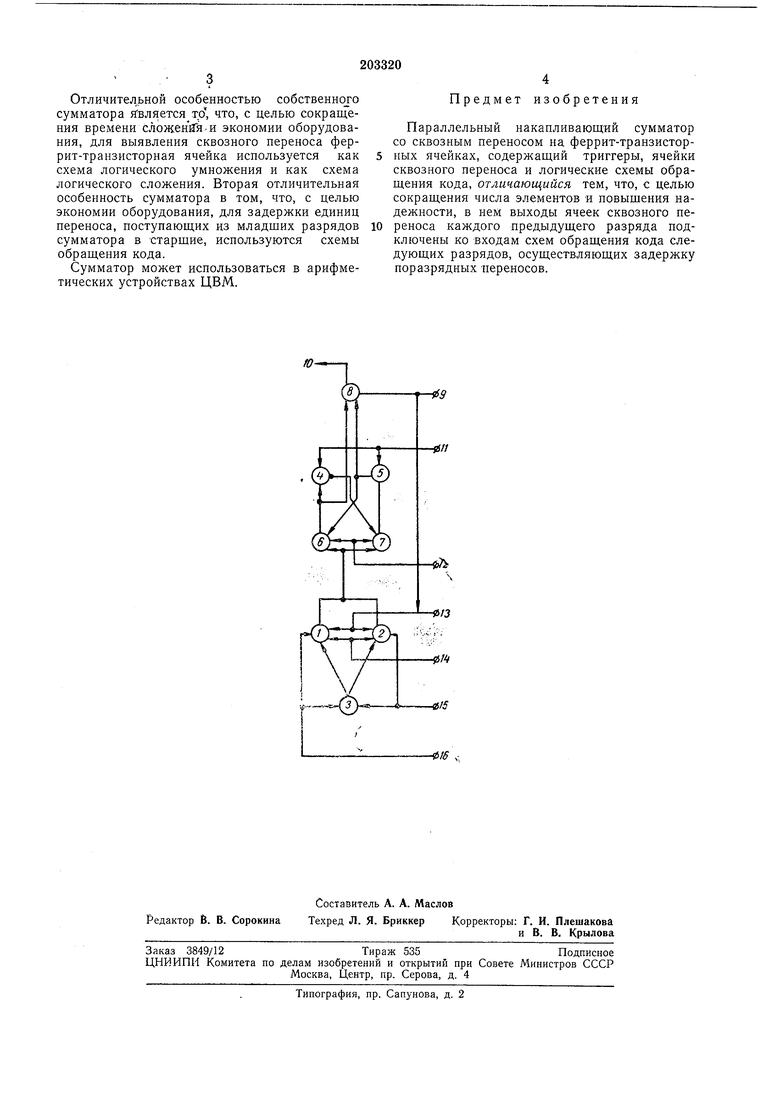

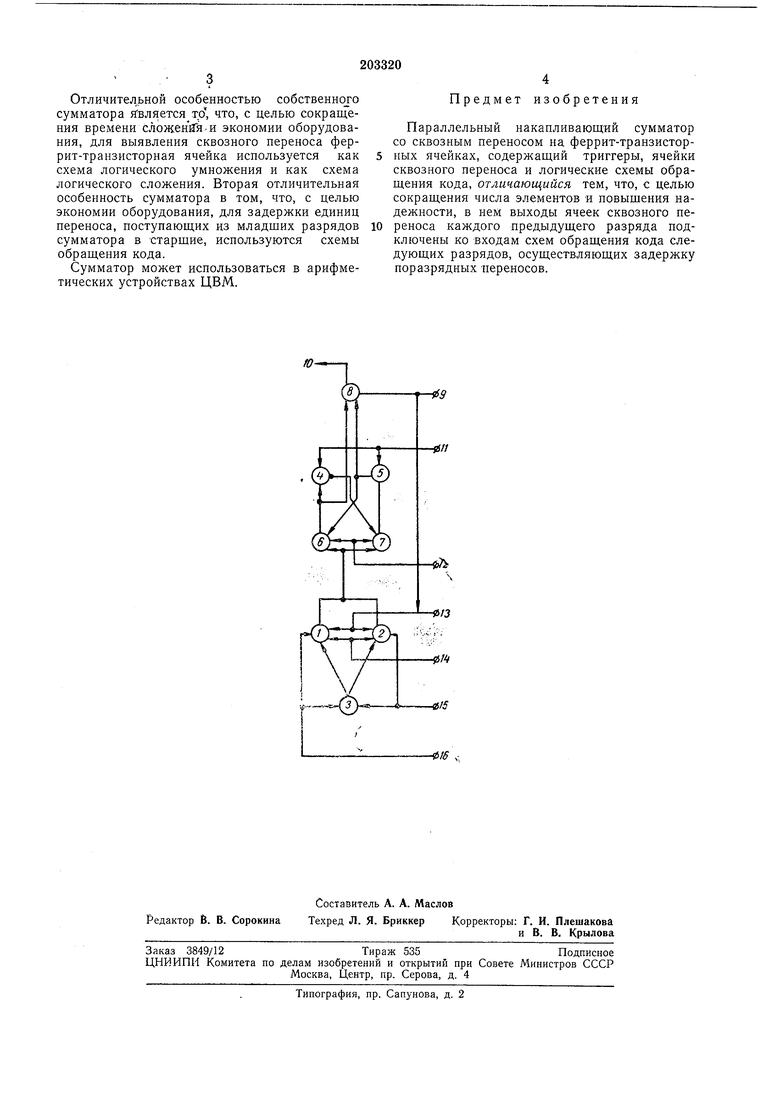

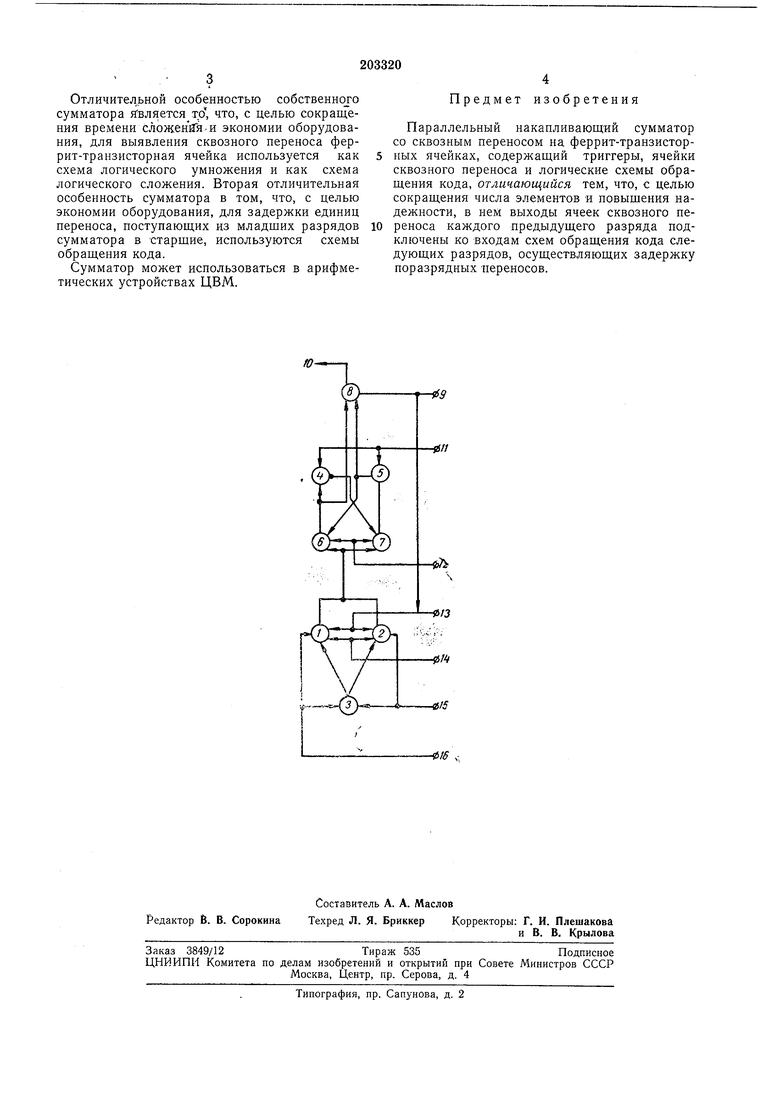

Функциональная схема т-го разряда сумматора приведена на чертеже.

Схема каждого разряда сумматора состоит из схемы «И для обращения кода чисел, поступающих на вход сумматора (ячейки 1, 2, 3), триггера на ячейках 4, 5, 6, 7 для образования поразрядной суммы по формуле:

5 с(а& + ай) + с(аЬ -Ь аЬ}.

Ячейки 4, 5 работают в режиме формирователей задержки (обрабатывают по заднему фронту входных сигналов).

Кроме того, в состав каждого разряда сумматора входит ячейка сквозного переноса 8 для образования переноса в следующий старший разряд по формуле:

е с(аЬ -}-аЬ) + аЬ.

Сигнал сквозного переноса подается на клемму 9. С клеммы 10 сигнал сквозного переноса подается на старшие разряды. На

клемму // подается сигнал подмагничивания. Клемма 12 служит для установки на нуль сумматора. Клемма 13 является входом разряда. По клемме 14 производится установка в нуль схем обращения кода. На клемму 15 подается сигнал считывания обратным кодом, а по клемме 16 - сигнал считывания прямым кодом.

Выход ячейки 10 заведен на вход схемы обращения кода соседнего старшего разряда,

где происходит задержка сигналов поразрядного переноса до завершения сквозного переноса.

По такту считываются схемы обращения кода для передачи на сумматор прямого или

обратного кода слагаемых, по такту tz формируются единицы сквозного переноса, по такту /3 считываются прямым кодом схемы обращения кода, и на сумматоре устанавливается результат операции сложения двух

Отличительной особенностью co6cTBeHHOjo сумматора Является то , что, с целью сокращения времени сложенйя-и экономии оборудования, для выявления сквозного переноса феррит-транзисторная ячейка используется как схема логического умножения и как схема логического сложения. Вторая отличительная особенность сумматора в том, что, с целью экономии оборудования, для задержки единиц переноса, поступающих из младших разрядов сумматора в старшие, используются схемы обращения кода.

Сумматор может использоваться в арифметических устройствах ЦВМ.

4 Предмет изобретения

Параллельный накапливающий сумматор со сквозным переносом на феррит-транзисторных ячейках, содержащий триггеры, ячейки сквозного переноса и логические схемы обращения кода, отличающийся тем, что, с целью сокращения числа элементов и повышения надежности, в нем выходы ячеек сквозного переноса каждого предыдущего разряда подключены ко входам схем обращения кода следующих разрядов, осуществляющих задержку поразрядных переносов.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1973 |

|

SU409220A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| Быстродействующий параллельный преобразователь кода Баркера в двоичный код | 1960 |

|

SU147026A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1314386A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

Даты

1967-01-01—Публикация