Известные устройства выборки информации (команд), состоящие из ферритовых матриц и двух кольцевых счетчиков, производят выборку команд из оперативной памяти, для чего в них используется совпадение токов по координатам X н У.

В описываемом устройстве, содержащем ферритовую матрицу и д|1« кадиц цьи eMpftiiiKB-, выборка компид производится путем записи с последующим чтением, что дает возможность создать 1адежные и экономичные системы выборки кома.нд из долговременного запоминающего устройства в специализированных -цифровых вычислительных маши.нах.

Это достигается тем, что в устройстве выходы одного кз кольцевых Счетчиков подключены к шинам записи О(дио1}ремснио во все столбцы матрицы, выходы второго счетчика подключены к соответствующим шинам считывания информации из каждого столбца, а выход последнего разряда второго счетчика соединен с щипама сдвига первого.

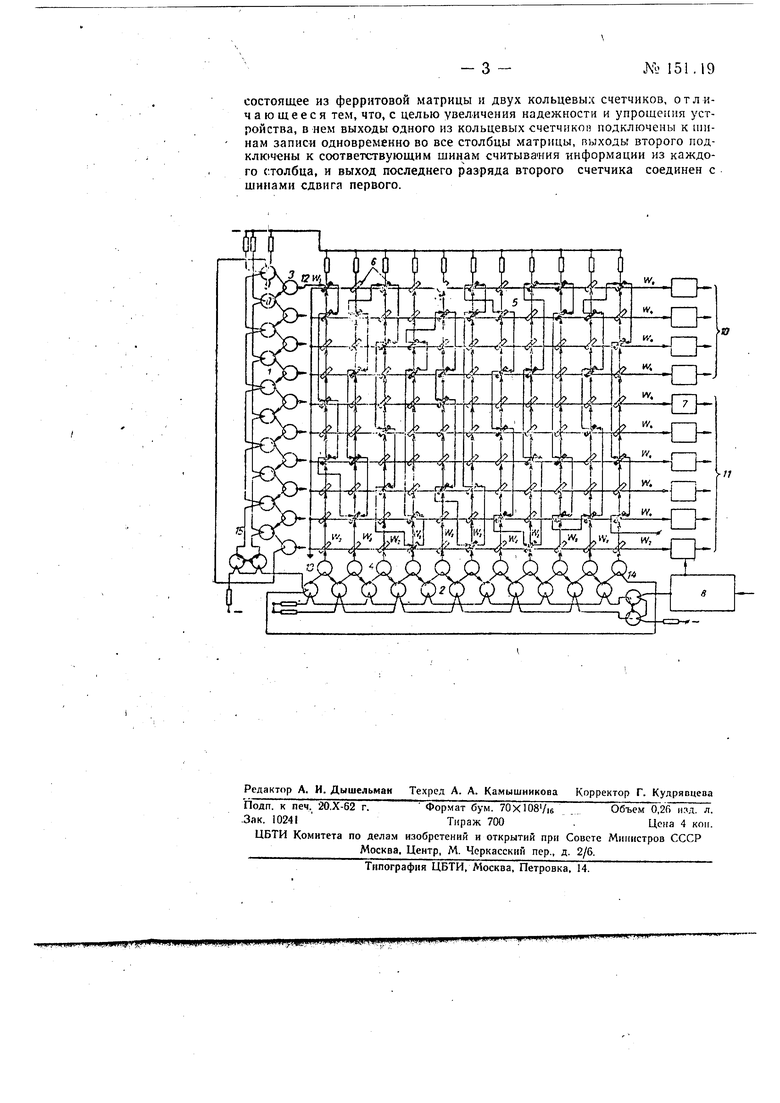

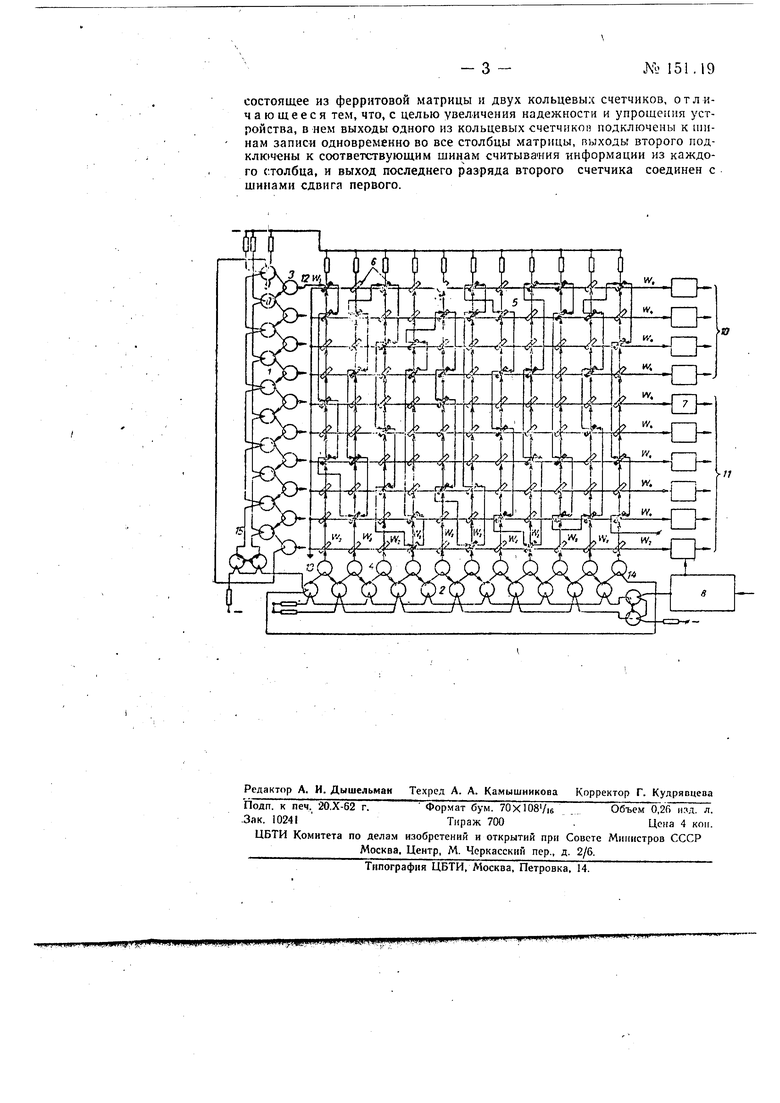

На чертеже приведена функциональная схема устройства.

В состав схемы входят: счетчик команд, выполненный из двух кольцевых счетчиков / 2 с формирователями записи 3 и считывания 4, матрица 5 команд из ферритов 6 с прямоугольной петлей гистерезиса, усилители 7 считывания и местное управление 5.

Устройство выпол.няет следующие функции.

Подсчет числа выполненных соманд, выборку адреса команд в устройстве, хранение команд, выборку кода команды по адресу команды и выдачу их в дешифраторы операций и адресов запоминающих устройств чисел м коэффициентов.

В приведенной схеме кольцевые счетчики построены на ферритотранзисторных ячейках. Счет производится сдвигом единицы в кольцевых счетчиках по двухтактной системе. Входными импульсами на пер№ 151119- 2 пый разряд счетчика 2, подлежащими пересчету, служг;;т сигналы окончания операции, которые производят единицы з счетчике. Сигнал переноса (переполнения) со старшего разряда счетчика 2 поступает нп сдвиг единицы счетчика / и перезаписывается iiepBi iii разряд счетчика 2.

Такая система отсчета щэи наличии матрицы 5 из запоминлющих элементов позволяет просто осуществить дешифрацию адреса команды при построении счетчика команд па число импульсных (динамических) элементах - феррнто-транзисторкых ячейках, п то время как прилеиение Д|:адны. дешифраторов сов JCTHO с импульсными элементами затруднительно.

С целью обеспечения возможности зыпол)1сния дешифрации кодои операций и адресов на диодно-трлнсформаториых матрицах, каждый из кодоз представляется в виде двухразрядного позиционного кода с основанием «/. Дешифрация адреса командь происходит следующим образом.

При сдвиге единицы в счетчике / выходным импульсом ячейки 9 производится запуск мощного формирователя записи 3, выходноГг HNJпульс которого .поступает в Ц1ин записи -з, пронизырающую по четыре феррита (на чертеже зачернены) в каждо.м столбце матрицы 5. Матрица набрана .таким образом, что число ферритов в каждом столбце равно сумме числа разрядов двухразрядных кодов операции 10 и адреса 11. а число столбцов равно числу разрядов счетчпка 2. Шина записи пронизывает в каждом столбце два феррита, соответствующие коду операции /О, и два феррита, соответствующие коду адреса /У чисел и коэффициентов, и при прохождении по ней импульса тока в них записываются единицы. Таким образом, при записи происходит как бы задание кодов операции и.адреса в каждом столбце. Выборка кода команды по адресу происходит при движении единицы по счетчику 2.

При этом выходной импульс с каждого разряда счетЧик а 2 через формирователь считывания 4 подается в шину считывания г соответствующего столбца ферритов 6, перемагничивая четыре феррита, соответствующие кодам адреса и операции. Ферриты, находящиеся в одной строке матрицы, прошиты общей выходной обмоткой W. Каждая такая обмотка соответствует определенному разряду в коде операции или адреса. (Поэтому при каждом сдвиге счетчика 2 на четырех выходных обмотках появляются сигналы, поступаюЩИе на усилители 7 счить вания. С выхода усилителей считывания выбранные коды адреса и операции поступают на диодно-трансформаторные дешифраторы операций и адресов (на чертеже не показано). Для того, чтобы в рез льтате суммирования помех в выходных обмотках № при записи команд не происходило срабатывания усилителей чтения, схема их-выполнена с введением стробирующего каскада. Количество .команд, которое быть воспроизведено с ломощью такой схемы, определяется произведением чисел разрядов первого и второго кольцевых счетчиков.

Увеличение надежности работы устройства достигнуто тем, что выходы 12 кольцевого счетчика 2 подключены к шинам записи W одновременно во все столбцы матрицы 5, выходы J3 кольцевого счетчика 2 подключены к шинам считывания информации Из каждого столбца, а выход И последнего разряда кольцевого счетчика 2 соединен с шинами сдвига /5 кольцевого счетчика /.

Устройство Выборки команд из долговременного запоминающего устройства в специализированных цифровых вычислительных машинах.

Предмет изобретения

состоящее из феррнтовой матрицы и двух кольцевых счетчиков, отличающееся тем, что, с целью увел.ичения надежности и упрощения устройства, в нем выходы одного из кольцевых счетчикон подключены к тинам записи одновременно во все столбцы матрицы, пыходы второго подключены к соответствующим шинам считывания информации из каждого столбца, и выход последнего разряда второго счетчика соединен с щинами сдвига первого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный сумматор параллельного действия на феррит-транзисторных элнментах | 1958 |

|

SU122940A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ДЕШИФРАЦИИ ДАННЫХ | 2006 |

|

RU2319197C1 |

| ПАРАЛЛЕЛЬНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU231223A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

Авторы

Даты

1962-01-01—Публикация

1961-07-31—Подача