Изобретение относится к специгши- зированным средствам вычислительной техники и может быть использовано дл построения релейных корреляторов., определяющих оценку взаимной корреля- ционной функции двух сигналов.

Цель изобретения - расширение динамического диапазона релейного коррелятора при незначительном усложнеНИИ устройства,

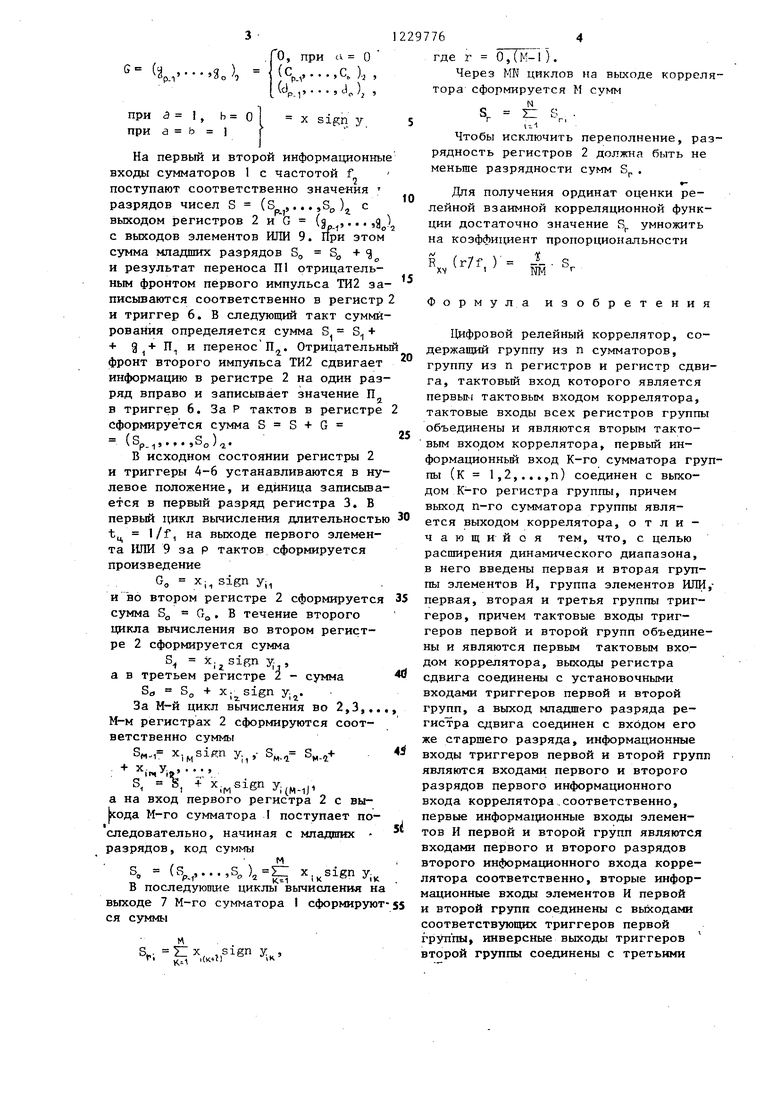

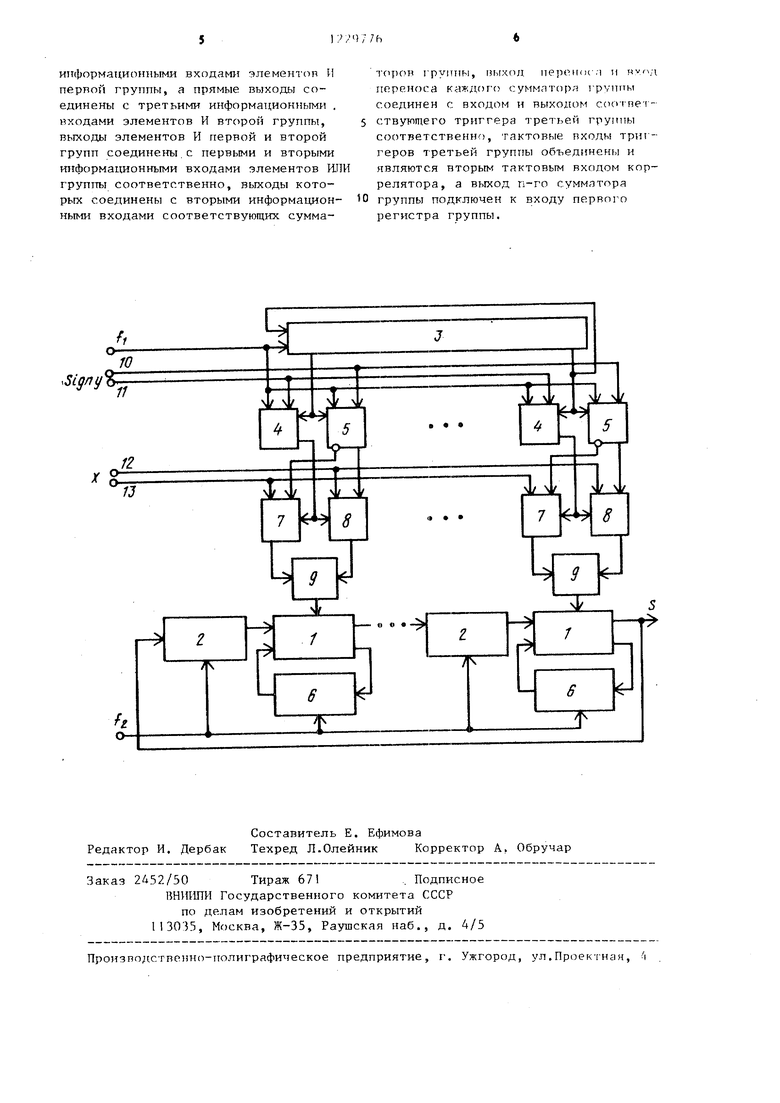

На чертеже изображена структурная схема релейного коррелятора.

Коррелятор содержит ь су шаторов п регистров 2, регистр 3 сдвига, первую 4, вторую 5 и третью 6 групшл триггеров,- первую 7 и вторую 8 группы элементов И, группу элементов ИЛИ вход 10 первого раз14яда первого информационного входа коррелятора, вход 1 второго разряда первого ин- формационного входа коррелятора, вход 2 первого разряда второго информационного входа коррелятора, вход 13 второго разряда второго информационного входа коррелятора.

В цифровом релейном корреляторе определяется оценка релейной взаимно корреляционной функции двух сигналов X и у.

R,/) (t+i) sign y(t) , где М - знак математического ожидания ;

sign у а(- ) ,

Г 1, при а 1, b о sign у- I О, при а О

-1, при а b 1.

Сигналы а и ь поступают на входы первого и второго разрядов первого информационного входа коррелятора. Сигнал а определяет интервалы времени анализа сигнала y(t), а сигнал Ь можно сформировать, например, пропуская y(t) через компаратор.

Так как арифметические операции в корреляторе выполняются над последовательными кодами, то двоичные коды второго исследуемого сигнала х подаются на входы первого и второго разрядов второго информационного входа коррелятора последовательно. Для преобразователя сигнала x(t) в такие коды можно, например, использовать аналого-цифровой преобразователь,, информация с выходов которого записьта- ется в регистры сдвига, выходы кото- рых подключены к входам первого и второго разрядов второго информа1 он- ного входа коррелятора. Старшие раз-

S 0 5

0

5

0

5

5

ряды двоичных кодов сигнала х определяют его знак, а разрядность двоичных кодов - динамический диапазон коррелятора, на входы 12 и 13 коррелятора, поступают соответственно - разрядные последовательные двоичные коды положительных и отрицательных значений входного сигнала х (Ср,,,.. ,С к -х (dp . . , ,do),i начиная с шaдшиx разрядов С и d , причем -X + 1 .

Коррелятор работает следующим образом.

На первый и второй тактовые входы коррелятора поступают тактовые импульсы ТИ1 и ТИ2, частоты следования

которьгх соответственно равны f, и f1

.f f э где Р- разрядность регистра 2). Число р определяет динамический диапазон коррелятора. Частота f является частотой дискретизации входных сигналов по оси времени. Значения сигналов х. и у, соответствуют моментам времени t M(i-l)+k-lJ/f, , где i 1,N, N - количество усреднений, М - число определяемых ординат оценки взаимной релейной корреляционной функции, которое равно числу сумматоров 1. Каждое значение х. поступает в коррелятор за Р тактов. Значения а. и Ь первого сигнала у поступают на счетные входы триггеров 4 и 5 соответственно с частотой f . Если в регистре 3 единица находится в k-м разряде и нули в остальных разрядах, то на входы установки k-x триггеров 4 и 5 поступает высокий разрешающий потенциал и отрицательный фронт импульса ТИ1 записывает в эти триггеры числа 4 и ь. и сдвигает единицу

IК

в (к +1) -и разряд регистра 3. При этом содержимое остальных триггеров не изменяется. После прохождения t-n импульсов ТИ в триггеры 4 и 5 с номерами 1 , 2,... ,t-ri записываются соответственно числа « я. h. . В триггерах 4 и 5 формируются

1 PTt i h

сдвинутые во времени коды сигнала у. Девшфратор, собранный на элементах И 7, 8 и ИЛИ 9, реализует логическую функцию

a CAaAbvdAaAb В нем производится перемножение входных сигналов. ЗаР тактов работы коррехштора через этот дешифратор П)Ьходят последовательно двоичные числа:

),

1 , Ь О b 1

О, при а О

|Чи I J Ч.1- . г 5

X sign у

На первый и второй информационны входы сумматоров 1 с частотой f поступают соответственно значения разрядов чисел S (Sp,... jS ) с выходом регистров 2 и G (§„. «3 с выходов элементов ИЛИ 9. При этом сумма младших разрядов S S + «3 и результат переноса П1 отрицательным фронтом первого импульса ТИ2 записываются соответственно в регистр и триггер 6. В следующий такт суммирования определяется сумма S S + + П и перенос П,. Отрицательны фронт второго импульса ТИ2 сдвигает информацию в регистре 2 на один разряд вправо и записывает значение П, в триггер 6. За Р тактов в регистре сформируется сумма S S + G

р-1 о 1

В исходном состоянии регистры 2 и триггеры 4-6 устанавливаются в нулевое положение, и единица записывается в первый разряд регистра 3. В первый цикл вычисления длительностью t 1/f, на выходе первого элемента ИЛИ 9 за Р тактов сформируется произведение

G, Х; sign у(

и во втором регистре 2 сформируется сумма Sg GO. В течение второго цикла вычисления во втором регистре 2 сформируется сумма S, x.sign V ,

а в третьем регистре 2 - сумма S- 5„ + у,,.

За М-й цикл вычисления во 2,3,,. М-м регистрах 2 сформируются соответственно суммы

x.sisn у.,- 3„., S.+ .

,,

1 - x.sign у.

(M-lJ

а на вход первого регистра 2 с вы- ода М-го сумматора I поступает последовательно, начиная с младших разрядов, код суммы

м

S, {Sp,..., x.sign у,

в последующие циклы вычисления на выходе 7 М-го сумматора I сформируют ся суммы

В„, Их,,,., sign у .

ки

(кЛ1

20

25

30

5

5

где г 0,(М-1).

Через MN циклов на выходе коррелятора сформируется М сумм

N с 5- с

г , г, lil

Чтобы исключить переполнение, разрядность регистров 2 должна быть не меньше разрядности сумм S, .

Дпя получения ординат оценки релейной взаимной корреляционной функции достаточно значение S, умножить на коэффициент пропорциональности

,)- A..S,

Формула изобретения

Цифровой релейный коррелятор, содержащий группу из п сумматоров, группу из п регистров и регистр сдвига, тактовый вход которого является первым тактовым входом коррелятора, тактовые входы всех регистров группы объединены и являются вторым такто- вьгм входом коррелятора, первый информационный вход К-го сумматора группы (к 1,2,...,п) соединен с выходом К-го регистра группы, причем выход п-го сумматора группы является выходом коррелятора, отличающийся тем, что, с целью расширения динамического диапазона, в него введены первая и вторая группы элементов И, группа элементов ИЛИ,- первая, вторая и третья группы триггеров, причем тактовые входы триггеров первой и второй групп объединены и являются первым тактовым входом коррелятора, выходы регистра сдвига соединены с установочными входами триггеров первой и второй групп, а выход мпадшего разряда ре- гис тра сдвига соединен с входом его же старшего разряда, информационные входы триггеров первой и второй групп являются входами первого и второго разрядов первого информационного входа коррелятора . соответственно, первые информационные входы элементов И первой и второй групп являются входами первого и второго разрядов второго информационного входа коррелятора соответственно, вторые информационные входы элементов И первой и второй групп соединены с выходами соответствующих триггеров первой группы, инверсные выходы триггеров второй группы соединены с третьими

информационными входами элементов И первой грунны, а прямые выходы соединены с третьими информационными входами элементов И второй группы, выходы элементов И первой и второй групп соединены.с нервыми и вторыми информационными входами элементов ИЛ группы соответственно, выходы которых соединены с вторыми информацион- ными входами соответствующих сумматоров группы, иьгход neiKMroc.-i и переноса каждого сумматорл группы соединен с входом и выходом соотг е-|- ствующего триггера третьей группы соответственно, тактовые входы геров третьей группы объединены и являются вторым тактовым входом коррелятора, а выход п-го сумматора группы подключен к входу первого регистра группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Коррелятор | 1984 |

|

SU1180927A1 |

| Устройство для выделения среднего из нечетного количества чисел | 1988 |

|

SU1647554A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Цифровой коррелятор | 1983 |

|

SU1130875A1 |

| Устройство для одновременного вычисления двух многочленов | 1987 |

|

SU1439580A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Цифровой коррелятор | 1980 |

|

SU942038A1 |

| Коррелометр | 1982 |

|

SU1026144A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для построения релейных корреляторов, определяющих оценку взаимной корреляционной функции двух сигналов. Цель изобретения - расширение динамического диапазона релейного коррелятора при незначительном усложнении устройства - достигается за счет введения в известное устройство двух групп элементов И, группы элементов ИЛИ и трех групп триггеров с соответствующими функциональными связями. 1 ил. tsD Ю СО VI а

| Цифровой коррелятор | 1980 |

|

SU942038A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой коррелятор | 1983 |

|

SU1130875A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-07-23—Подача