Изобретение относится к электротехнике и может быть использовано в устройствах электропитания узлов автоматики, вьпислительной и измерительной техники и средств связи.

Цель изобретения - повышение эф- фективности стабилизапии напряжений на выходе ка,налов за счет учета потребления нагрузок в данный момент времени,, путем адаптивного слежения за выходными напряжениями.

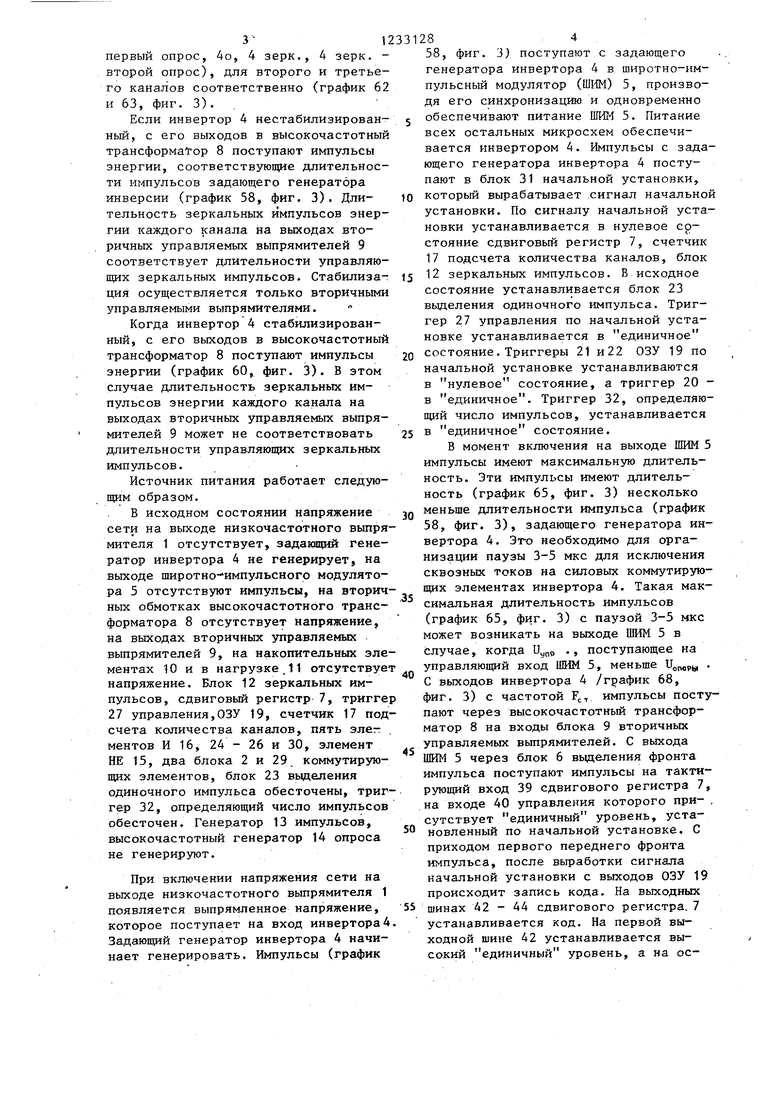

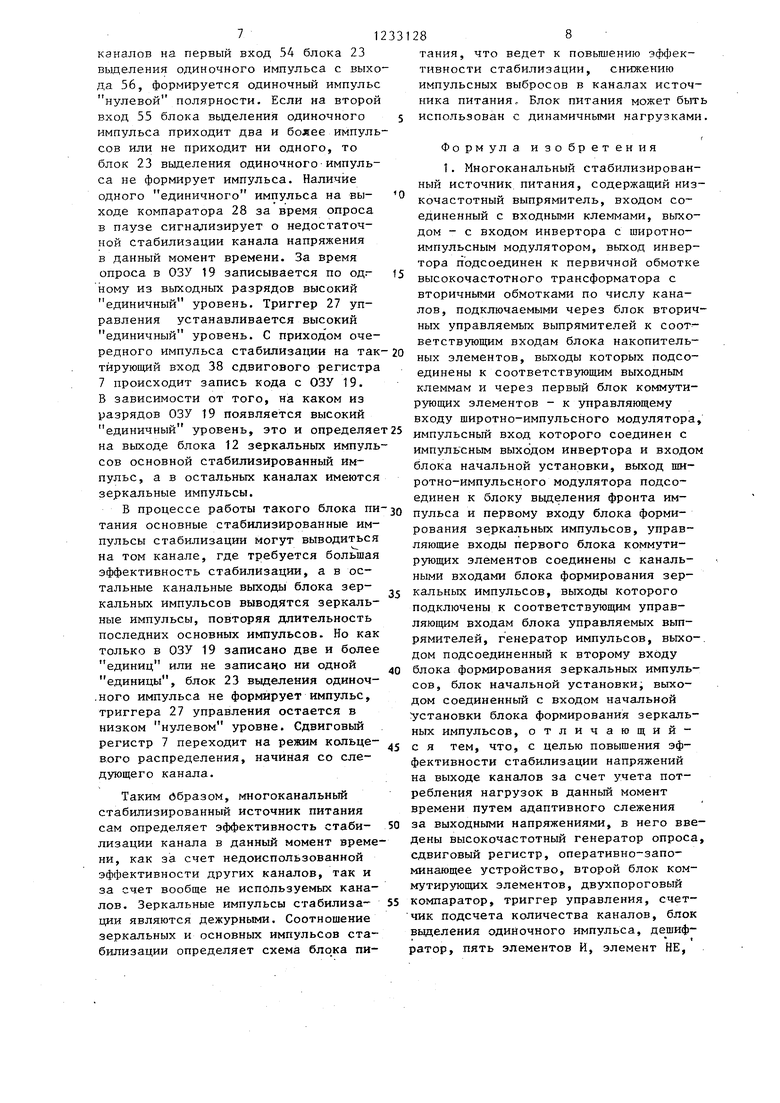

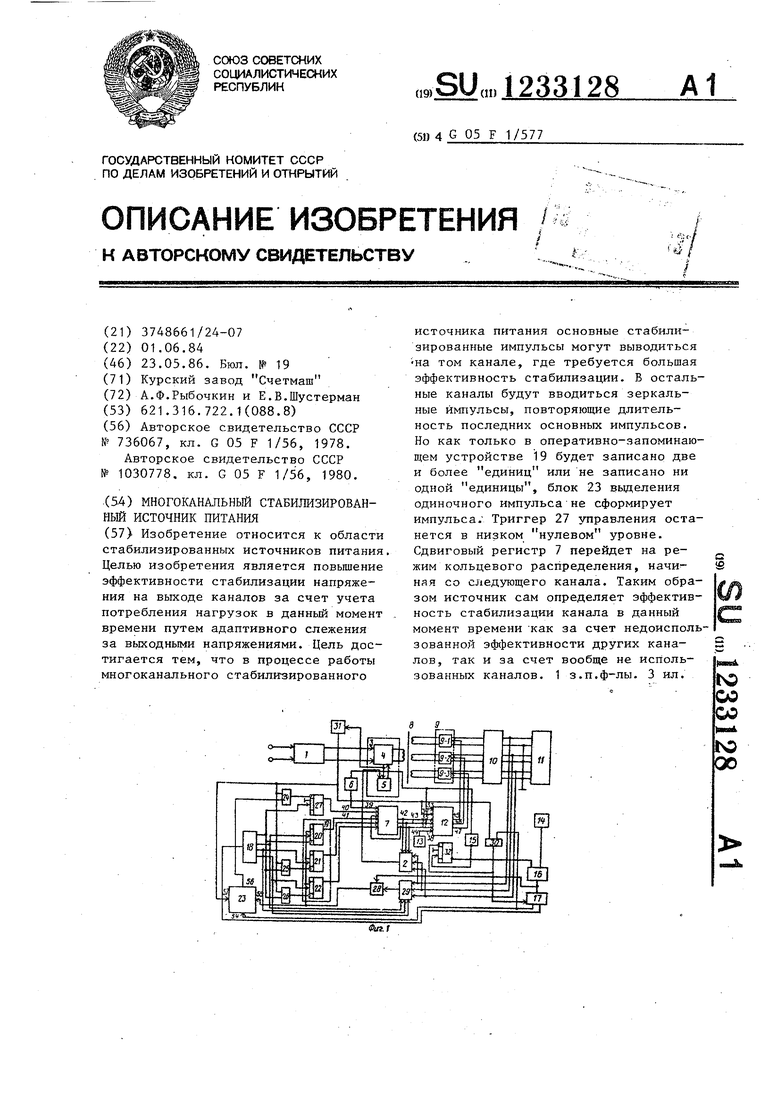

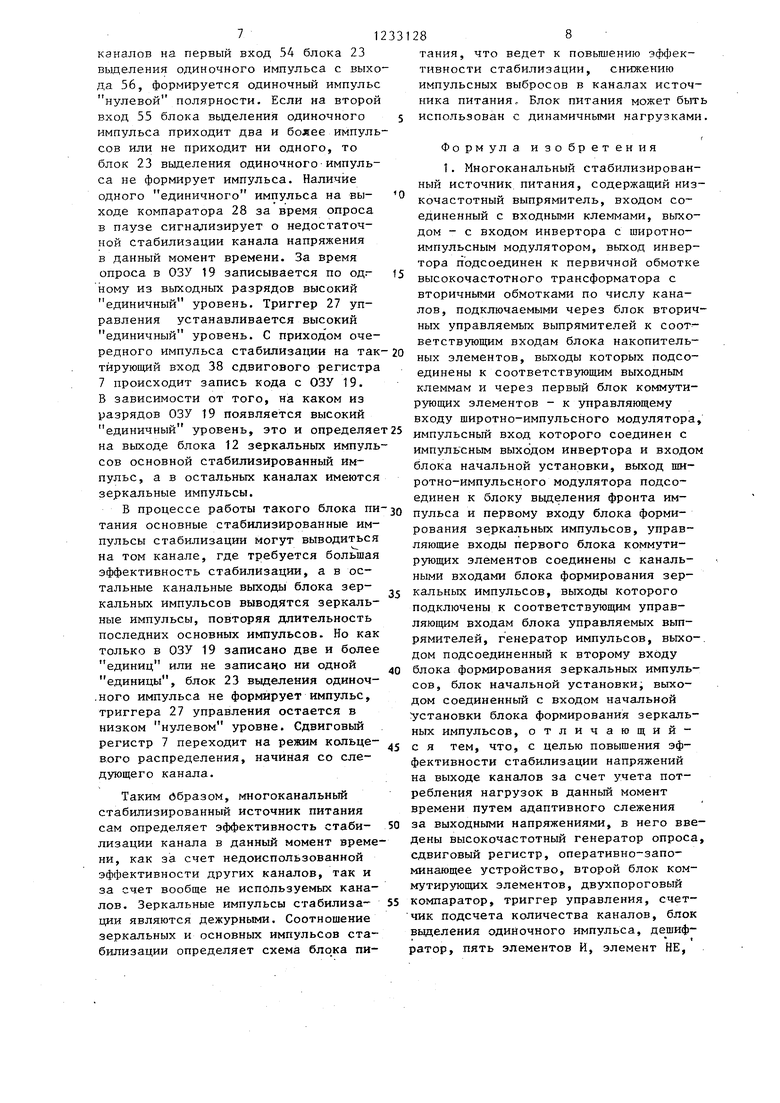

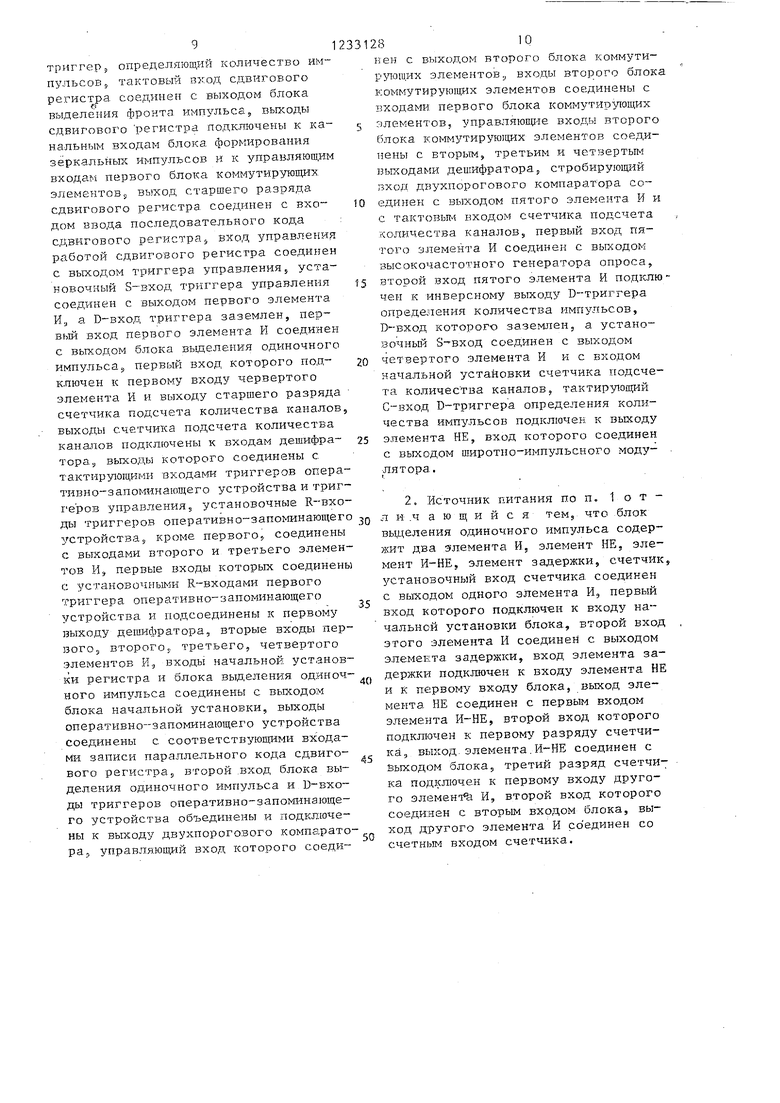

На фиг. 1 приведена структурная блок-схема предлагаемого многоканального источника питания; на фиг. 2 - , принципиальная электрическая схема блока выделения одиночного импульса, на фиг 3 - графики, поясняющие принцип действия многоканального источника питания.

Источник питания содержит низкочастотный выпрямитель 1, первый блок 2 коммутирующих элементов, блок 3,включающий инвертор 4 и широтно-импульс- ный модулятор 5 5 блок 6 выделения фронта импульса, сдвиговый регистр 7 высокочастотный трансформатор 8, блок 9 вторичных управляемых выпрямителей, блок 10 накопительньк элементов, блок 11 нагрузок,подключенных к выходным клеммам,блок 12 формирования зеркальных импульсов, генератор 13 импульсов., высокочастотный генератор 14 опроса, элемент НЕ 15, пятый элемент И 16, счетчик 17 подсчета количества каналов, дешифратор 18, оперативно-запоминающее устройство (ОЗУ) 19, триггеры 20-22 ОЗУ, блок 23 вьщеления одиночного импульса, первый 24,, второй 25J третий 26 элементы И, триггер 27 управления., двух- пороговый компаратор 28, второй блок 9 коммутирующих элементов, четвер- ло1Й элемент И 30, блок 31 начальной установки, триггер 32,, определяющий число импульсов, первый вход 33 блока 12 формирования зеркальных импульсов, вход 34 начальной установки, канальные входь 35-37, второй вход 38 блока 12 формирования зеркальных импульсов,тактирующий вход 39 сдвигового регистра 7, вход 40 управления сдвигового регистра .7, вход 41 ввода последовательного кода одвиго- вого регистра 7, выходные шины 42-44 сдвигового регистра 7, выходные шины 45 - 47 блока 12 формирования зеркальных импульсов.

Блок 23 выделения одиночного импульса содержит элемент НЕ 48, элемент И-НЕ 49, счетчик 50, два элемента И 51 и 52, элемент 53 за.держ5 ки, первый 54 и второй 55 входы,выход 56, вход 57 начальной установки. На фиг. 3 использованы следующие обозначения: 58- график импульсов задающего генератора инвертора 4;

0 59 - силовые стабилизированные импульсы на выходе инвертора 4; 60 - импульсы на выходе широтно-импульс- ного модулятора 5; 61-63 - импульсы управления первым 9-1, вторым 9-2 и

15 тратим 9-3 вторично управляемыми выпрямителями на 45-47 - выходных шинах блока 12 формирования зеркальных импульсов Ьоответственно (случай, когда сдвиговый регистр 7 работает 20 по кольцу); 64 - тактируюБЩе импульсы на вьпсоде блока выделения фронта импульсов; 65 - импульсы на выходе широтно-импульсного модулятора 5; 66 - импульсы на выходе элемента

25 НЕ 15 67 - импульсы на выходе элемента И 16; 68 - силовые импульсы на выходе инвертора 4.

Сдвиговый регистр 7 -используется в двух режимах; в режиме работы расп30 ределения импульсов по коггьцу и в режиме -параллельной записи с выходов ОЗУ 19 в сдвиговый регистр 7.

Блок 12 формирования зеркальных импульсов предназначен для запоминадс НИН ,цлительности отстабилизированно- го импульса.

Сдвиговый регистр 7 при работе по кольцу поочередно включает канальные входы 35 - 37 блока 12 формирования

40 зеркальных импульсов, на входах которых поочередно устанавливаются высокие единичные уровни lo, 2о, Зо, 4о, 5о, 6о и т,д, (графики 61 - 63, фиг. 3). В те моменты, когда обслу45 живается очередной канальный вход - остальные отключены. При непосредственном управлении блоком 9 вторичных управляемых выпрямителей с выходов сдвигового регистра 7 в режиме коль50 цевого распределения частоты импульсов энергии с выходов вторичных управляемых выпрямителей 9 ка7кд,ого ка- на.на умеигзшилась бы в три раза при трех каналах. Чтобы этого не происхо55 дило, провалы во время опроса заполняются зеркальными импульсами, повторяющими длительность основного импульса (график 61: 1о,1 зерк., 1 зерк,первый опрос, 4о, 4 зерк., 4 зерк. - второй опрос), для второго и третьего каналов соответственно (график 62 и 63, фиг. 3).

Если инвертор 4 нестабилизирован- ньй, с его выходов в высокочастотный трансформатор 8 поступают импульсы энергии, соответствующие длительности импульсов задающего генератора инверсии (график 58, фиг. 3). Дли- тельность зеркальных импульсов энергии каждого канала на выходах вторичных управляемых выпрямителей 9 соответствует длительности управляющих зеркальных импульсов. Стабилиза- ция осуществляется только вторичными управляемыми выпрямителями.

Когда инвертор 4 стабилизированный, с его выходов в высокочастотный трансформатор 8 поступают импульсы энергии (график 60, фиг. 3). В этом случае длительность зеркальных импульсов энергии каждого канала на выходах вторичных управляемых выпрямителей 9 может не соответствовать длительности управляющих зеркальных импульсов.

Источник питания работает следующим образом.

В исходном состоянии напряжение сети на выходе низкочастотного выпрямителя 1 отсутствует, задающий генератор инвертора 4 не генерирует, на выходе широтно- импульсного модулятора 5 отсутствуют импульсы, на вторим- ных обмотках высокочастотного трансформатора 8 отсутствует напряжение, на выходах вторичных управляемых выпрямителей 9, на накопительных элементах 10 и в нагрузке.11 отсутствует напряжение. Блок 12 зеркальных импульсов, сдвиговый регистр 7, триггер 27 управления,ОЗУ 19, счетчик 17 подсчета количества каналов, пять элементов И 16, 24 - 26 и 30, элемент НЕ 15, два блока 2 и 29, коммутирующих элементов, блок 23 вьщеления одиночного импульса обесточены, триг- гер 32, определяющий число импульсов обесточен. Генератор 13 импульсов, высокочастотный генератор 14 опроса не генерируют.

При включении напряжения сети на выходе низкочастотного выпрямителя 1 появляется выпрямленное напряжение, которое поступает на вход инвертора 4 Задающий генератор инвертора 4 начинает генерировать. Импульсы (график

5 5

0 5

о

5

0

58, фиг. 3) поступают с задающего генератора инвертора 4 в широтно-нм- пульсный модулятор (ШИМ) 5, производя его синхронизацию и одновременно обеспечивают питание ШИМ 5. Питание всех остальных микросхем обеспечивается инвертором 4. Импульсы с задающего генератора инвертора 4 поступают в блок 31 начальной установки, который вырабатывает сигнал начальной установки. По сигналу начальной установки устанавливается в нулевое ср- стояние сдвиговый регистр 7, счетчик 17 подсчета количества каналов, блок 12 зеркальных импульсов. В исходное состояние устанавливается блок 23 вьщеления одиночного импульса. Триггер 27 управления по начальной установке устанавливается в единичное состояние. Триггеры 21 и22 ОЗУ 19 по начальной установке устанавливаются в нулевое состояние, а триггер 20 - в единичное. Триггер 32, определяющий число импульсов, устанавливается в единичное состояние.

В момент включения на выходе ШИМ 5 импульсы имеют максимальную длительность. Эти импульсы имеют длительность (график 65, фиг. 3) несколько меньше длительности импульса (график 58, фиг. 3), задающего генератора инвертора 4. Эт-о необходимо для организации паузы 3-5 МКС для исключения сквозных токов на силовых коммутирующих элементах инвертора 4. Такая максимальная длительность импульсов (график 65, фиг. 3) с паузой 3-5 мкс может возникать на выходе ШИМ 5 в случае, когда И ., поступающее на управляющий вход ШИМ 5, меньше Uonopj, . С выходов инвертора 4 /график 68, фиг. 3) с частотой F,. импульсы поступают через высокочастотный трансформатор 8 на входы блока 9 вторичных управляемых выпрямителей. С выхода ШИМ 5 через блок 6 вьщеления фронта импульса поступают импульсы на тактирующий вход 39 сдвигового регистра 7, на входе 40 управления которого при- . сутствует единичный уровень, установленный по начальной установке. С приходом первого переднего фронта импульса, после выработки сигнала начальной установки с выходов ОЗУ 19 происходит запись кода. На выходных шинах 42 - 44 сдвигового регистра, 7 устанавливается код. На первой выходной шине 42 устанавливается высокий единичный уровень, а на остальных выходных шинах 43 и 44 - низкий нулевой уровень.

Одновременно с записью кода в сдвиговый регистр 7 на первый вход 33 блока 12 зеркальных импульсов поступает единичный импульс с выхода ШИМ 5, так при наличии высокого единичного уровня на первом канальном входе 35 блока 12 зеркальных импульсов на выходной шине 45 воспроизводится остабилизированный импульс напряжения 1о (график 61, фиг. 3), который поступает на управляемый выпрямитель 9 первого канала. На первом управляющем входе блока 2 коммутирующих элементов появляется единичный уровень, что обеспечивает коммутацию обратной связи первого канала. Напряжение с выхода первого канала поступает через коммутирующий элемент блока 2 коммутирующих элементов на управляющий вход ШИМ 5. Остальные каналы закрыты низкими нулевыми уровнями. Между импульсами стабилизации имеется пауза низкого нулевого У1ЭОВНЯ. Как только первый импульс стабилизации высокого единичного уровня (график 60, фиг. 3) заканчивается, на выходе элемента НЕ 15 формируется высокий единичный импульс паузы (график 66, фиг. 3), который поступает на С-вход D-триггера 32, устанавливая на его инверсном выходе высокий единичный уровень. Пятый элемент И 16 обеспечивает прохождени импульсов с высокочастотного генератора 14 опроса на вход счетчика 17 подсчета количества каналов.

Частота генератора 14 выбирается, исходя из того, чтобы за время паузы 3-5 МКС просчитать все каналы источника питания один раз (график 67, фиг. 3) Как только произведет подсче счетчик 17 с помощью четвертого мента И 30, триггера 32 становится в исходное нулевое состояние, ожидая новую паузу. С выходов счетчика 17 двоичный код поступает на входы де- ишфратора 18, с первого выхода дешифратора низкий нулевой импульс устанавливает триггеры 20 - 22 ОЗУ .9 в низкие нулевые уровни, а положительный перепад этого импульса поступает на С-вход триггера 27 управления, также устанавливая его в низкий нулевой уровень. В начальный момент времени (время переходного процесса) двухпороговый компаратор

установлен в высокий единичный

0

5

0

5

0

5

0

5

28

уровень. Управляющее напряжение на вход компаратора 28 поступает с выхода второго блока 29 коммутирующих элементов. Импульсные сигналы управления низкого уровня поступают на второй блок 29 коммутирующих элементов с второго, третьего и четвертого выходов дешифратора 18. Выходное напряжение компаратора 28 стробирует- ся. ОЗУ 19 записывает высокие единичные уровни. С приходом второго тактирующего импульса стабилизации одновременно на тактирующий вход 38 сдвигового регистра 7 и на первый вход 33 блока 12 зеркальных импульсов (а на выходе 40 управления сдвигового регистра 7 установлен низкий нулевой уровень) высокий единичный уровень с выходной шины 42 сдвигового регистра 7 переходит на выходную шину 43. Соответственно на выходной шине 46 блока 12 зеркальных импульсов формируется основной импульс стабилизации высокого единичного уровня 2о (график 62, фиг.З), а на первой выходной шине 45 воспроизводится первый зеркальный импульс 1 зерк. (график 61, фиг. 3).

Во время переходного процесса сдвиговый регистр 7 работает как кольцевой распределитель. Как только на выходе двухпорогового компаратора 28 начинают попеременно появляться низкие уровни и высокие единичные уровни, наступает установившийся режим работы блока питания.

Блок 23 вьщеления одиночного импульса предназначен для формирования одиночного импульса и работает следующим образом.

В момент включения питания с приходом сигнала начальной установки через элемент И 51 осуществляется установка счетчика 50 в исходное состояние. По первому разряду устанавливается низкий нулевой уровень, а на втором и третьем разрядах высокие единичные уровни. Если на второй вход 55 блока выделения одиночного приходит один импульс с выхода двухпорогового компаратора 28 за время опроса всех каналов, то по последнему сигналу нулевой полярности, поступившему со старшего разряда счетчика 17 подсчета количества

71

каналов на первый вход 54 блока 23 выделения одиночного импульса с выхода 56, формируется одиночный импульс нулевой полярности. Если на второй вход 55 блока выделения одиночного импульса приходит два и более импульсов или не приходит ни одного, то блок 23 выделения одиночного импульса не формирует импульса. Наличие одного единичного импульса на вы- ходе компаратора 28 за время опроса в паузе сигнализирует о недостаточной стабилизации канала напряжения в данный момент времени. За время опроса в ОЗУ 19 записывается по од- ному из выходньпс разрядов высокий единичный уровень. Триггер 27 управления устанавливается высокий единичный уровень. С приходом очередного импульса стабилизации на так тирующий вход 38 сдвигового регистра

7происходит запись кода с ОЗУ 19.

8зависимости от того, на каком из разрядов ОЗУ 19 появляется высокий единичный уровень, это и определяе на выходе блока 12 зеркальных импульсов основной стабилизированный импульс, а в остальных каналах имеются зеркальные импульсы.

В процессе работы такого блока пи тания основные стабилизированные импульсы стабилизации могут выводиться на том канале, где требуется большая эффективность стабилизации, а в остальные канальные выходы блока зеркальных импульсов выводятся зеркальные импульсы, повторяя длительность последних основных импульсов. Но как только в ОЗУ 19 записано две и более единиц или не записано ни одной единицы, блок 23 выделения одиноч- .ного импульса не формирует импульс, триггера 27 управления остается в низком нулевом уровне. Сдвиговьй регистр 7 переходит на режим кольце- вого распределения, начиная со следующего канала.

Таким йбразом, многоканальный стабилизированный источник питания сам определяет эффективность стаби- лизации канала в данный момент времени, как за счет недоиспользованной эффективности других каналов, так и за счет вообще не используемых каналов. Зеркальные импульсы стабилиза- дин являются дежурными. Соотношение зеркальных и основных импульсов стабилизации определяет схема бло.ка пи

s Оf5 20

25

зо .,

0 5

5

1288

тания, что ведет к повышению эффективности стабилизации, снижению импульсных выбросов в каналах источника питания. Блок питания может быть использован с динамичными нагрузками.

Формула изобретения

1. Многоканальный стабилизированный источник питания, содержащий низкочастотный выпрямитель, входом соединенный с входными клеммами, выходом - с входом инвертора с широтно- импульсным модулятором, выход инвертора подсоединен к первичной обмотке высокочастотного трансформатора с вторичными обмотками по числу каналов, подключаемыми через блок вторичных управляемых выпрямителей к соответствующим входам блока накопительных элементов, выходы которых подсоединены к соответствующим выходным клеммам и через первый блок коммутирующих элементов - к управляющему входу широтно-импульсного модулятора, импульсный вход которого соединен с импуль сным выходом инвертора и входом блока начальной установки, выход ши- ротно-импульсного модулятора подсоединен к блоку выделения фронта импульса и первому входу блока формирования зеркальных импульсов, управляющие входы первого блока коммутирующих элементов соединены с канальными входами блока формирования зеркальных импульсов, выходы которого подключены к соответствующим управляющим входам блока управляемых выпрямителей, генератор импульсов, выхо-. дом подсоединенный к второму входу блока формирования зеркальных импульсов, блок начальной установки; выходом соединенный с входом начальной установки блока формирования зеркальных импульсов, отличающий- с я тем, что, с целью повышения эффективности стабилизации напряжений на выходе каналов за счет учета потребления нагрузок в данный момент времени путем адаптивного слежения за выходными напряжениями, в него введены высокочастотный генератор опроса, сдвиговый регистр, оперативно-запоминающее устройство, второй блок коммутирующих элементов, двухпороговый компаратор, триггер управления, счетчик подсчета количества каналов, блок выделения одиночного импульса, дешиф , I

ратор, пять элементов И, элемент НЕ,

91

триггерj определяющий количество импульсов ;, тактовый вход сдвигового регистра, соединен с выходом блока выделения фронта импульса, вьшоды сдвигового регистра подключены к ка- нальным входам блока формирования зеркальных импульсов и к управляюш,им входам первого блока коммутирующих элементов5 вьжод старшего разряда сдвигового регистра соединен с входом ввода последовательного кода сдвигового регистра5 вход управления работой сдвигового регистра соединен с выходом триггера управленияj установочный 8--вход триггера управления соединен с выходом первого элемента Ид а D-вход триггера заземлен, первый вход первого элемента И соединен с выходом блока выделения одиночного импульса5 первый вход которого подключен к первому входу червертого элемента И и выходу старшего разряда счетчика подсчета количества каналов выходь счетчика подсчета количества каналов подключены к входам дешифратора, выходы которого соединены с тактирующими входами триггеров оперативно-запоминающего устройства и триг г е ров управления, установочные R-BXO ды триггеров оперативно запо шнающег устройства, кроме nepBoroj соединены с выходами второго и третьего элементов И, первые входы которых соединен с установочньми Е входами первого триггера оперативно-запоминающего устройства и подсоединены к первому выходу дешифратора, вторые входы первого, второго, третьего, четвертого элементов И, входы начальной установки регистра и блока выделения одиноч кого импульса соединены с выходом блока начальной установки, выходы оперативно-запоминающего устройства соединены с соответствующими входами записи параллельного кода сдвигового регистра, второй .вход блока выделения одиночного импульса и ды триггеров оперативно-запоминающего устройства объединены и подключены к выходу двухпорого:вого компарато

ра, управляющий вход которого соедиto

t5

20

31

g

25

5

0

5

0

2810

кеи с выходом второго блока ког-даути- рующих элементов,, входы второго блока коммутирующих элементов соединены с входами первого блока коммутирующих элементов, управляющ1 е входы второго блока коммутирующих элементов соединены с вторьш,, третьим и четвертьш зькодами дешифратора; стробирующ1-б:й вход Д1 ухпорогового компаратора соединен с выходом пятого элемента И и с тактовьи входом счетчика подсчета количества каналов, первый вход пятого 3JzeMeHTa И соединен с выходом зысокочастотного генератора опроса, второй вход пятого элемента И подключен к инверсному выходу D-триггера определения количества импульсов, D-вход которого заземлен, а установочный З- Вход Соединен с выходом четвертого элемента И и с входом начальной установки счетчика подсчета количества каналов, тактирующий С-вход D-триггера определения количества импульсов подключен; к выходу элемента НЕ, вход которого соединен с выходом широтно-импульсного моду- ля тора..

2. Источник питания по п. 1 о т - л и .4 а ю щ и и с я тем, что блок вьщеления одиночного импульса содержит два элемента И, элемент НЕ, элемент И-НЕ, элемент задержки, счетчик, установочный вход счетчика соединен с выходом одного элемента И, первый вход которого подключен к входу начальной установки блока, второй вход , этого элемента И соединен с выходом элемента задержки, вход элемента задержки подключен к входу элемента НЕ и к первому входу блока, выход элемента НЕ соединен с первым входом элемента И-НЕ, второй вход которого подключен к первому разряду счетчика, выход.элемента.И-НЕ соединен с Выходом блока, третий разряд счетчн- ка подключен к первому входу другого элемент И, второй вход которого соединен с вторым входом блока, выход другого элемента. И со единен со счетньм входом счетчика.

г

fj

j:

w

л

5

/TV

Р

ss

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| Устройство для опроса источников дискретных сообщений | 1980 |

|

SU955015A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1984 |

|

SU1156053A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1436111A1 |

Изобретение относится к области стабилизированных источников питания. Целью изобретения является повышение эффективности стабилизации напряжения на выходе каналов за счет учета потребления нагрузок в данный момент времени путем адаптивного слежения за выходными напряжениями. Цель достигается тем, что в процессе работы многоканального стабилизированного источника питания основные стабилизированные импульсы могут выводиться на том канале, где требуется большая эффективность стабилизации. В остальные каналы будут вводиться зеркальные импульсы, повторяющие длительность последних основных импульсов. Но как только в оперативно-запоминающем устройстве 19 будет записано две и более единиц или не записано ни одной единицы, блок 23 вьщеления одиночного импульса не сформирует импульса. Триггер 27 зшравления останется в низком нулевом уровне. Сдвиговый регистр 7 перейдет на режим кольцевого распределения, начи ная со следзпощего канала. Таким образом источник сам определяет эффективность стабилизации канала в данный момент времени как за счет недоиспользованной эффективности других каналов, так и за счет вообще не использованных каналов. 1 з.п.ф-лы. 3 ил. 3 3 а (О ю со 00

Фаг. 2

Редактор О.Юрковецкая

Составитель В.Ищенко Техред В.Кадар

Заказ 2769/49Тираж 836Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

44

J

Корректор А.ТЯСКО

| Многоканальный стабилизированный источник питания | 1977 |

|

SU736067A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многоканальный стабилизированный источник питания | 1982 |

|

SU1030778A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-05-23—Публикация

1984-06-01—Подача