Изобретение относится к нычисли- , тельной технике и предназначено для одновременного умножения нескольких синхронно поступающих Г Шадшимн разря дами вперед дворгчных чисел.

Целью изобретения является расширение функциональных возможностей за счет одновременного умножения К со- множителей.

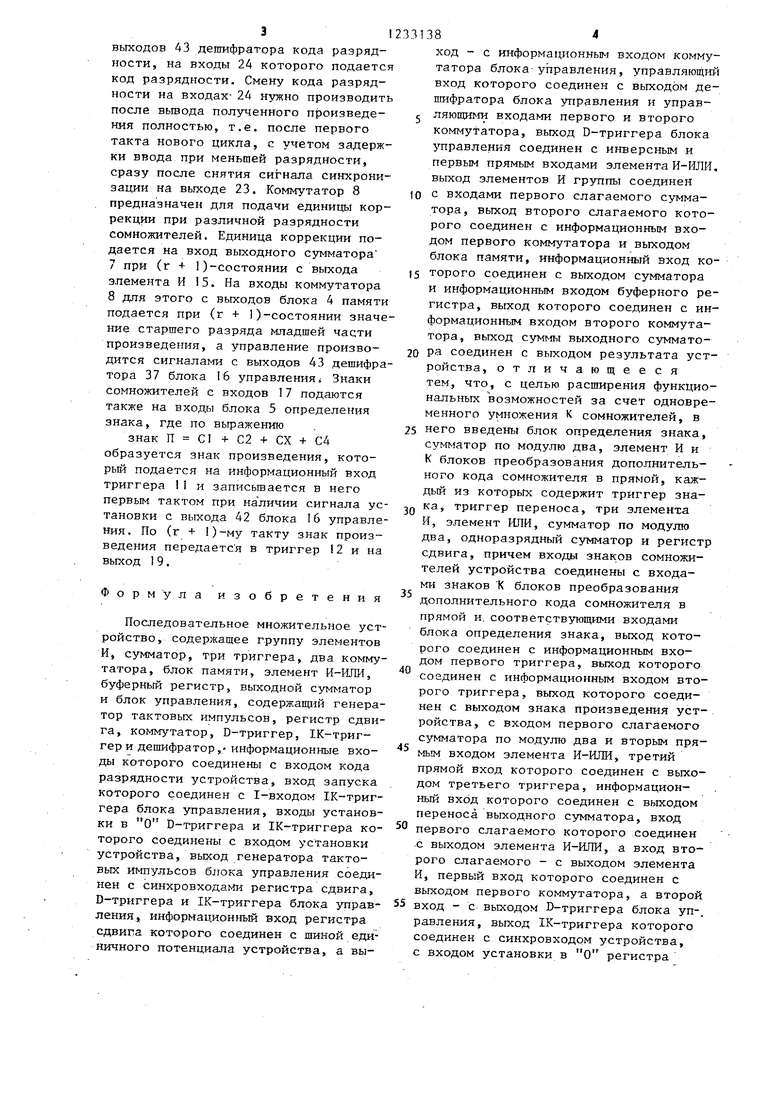

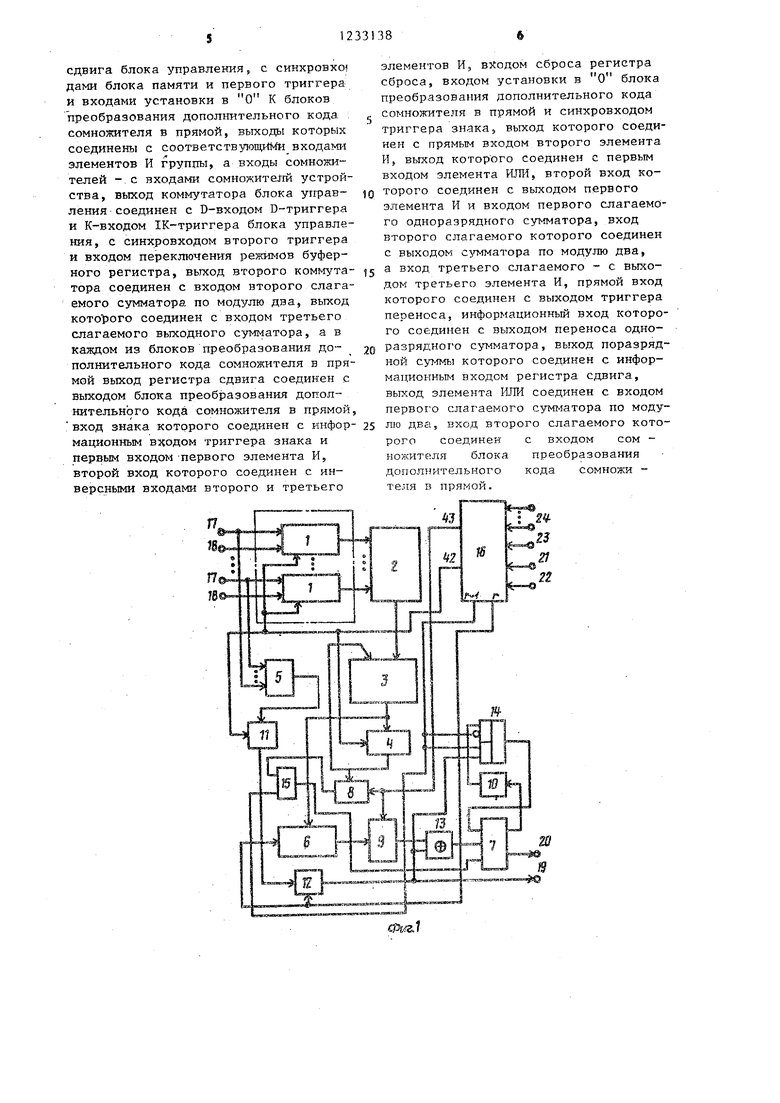

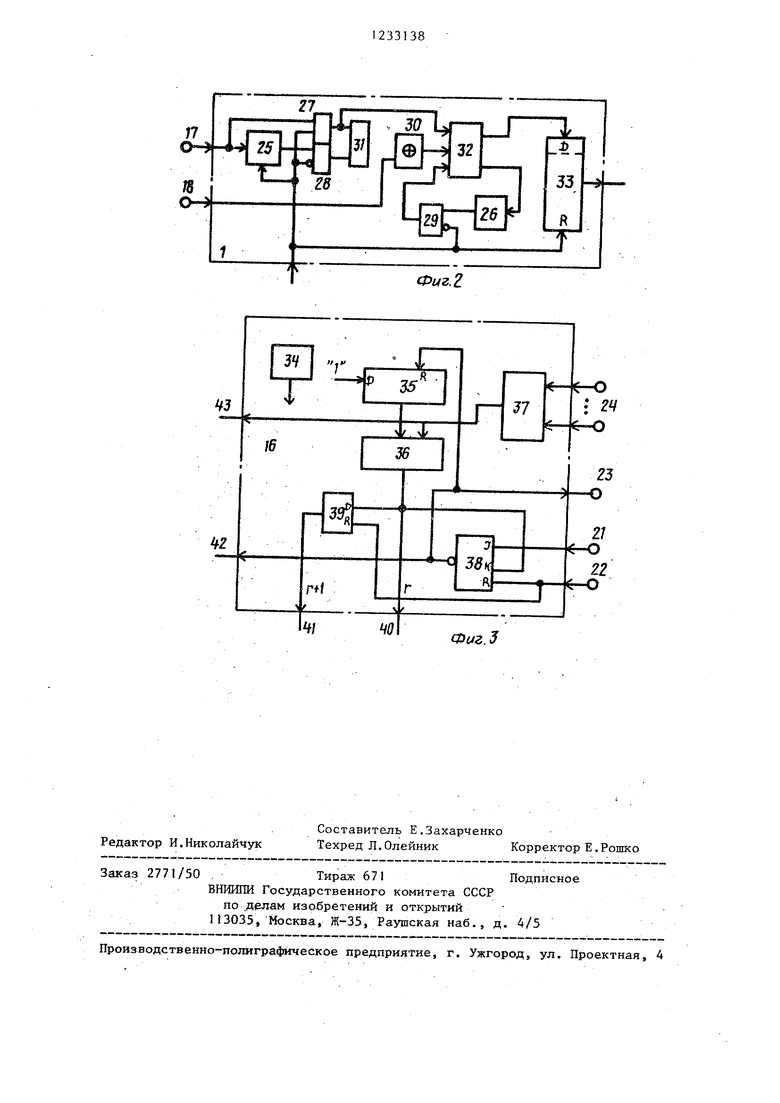

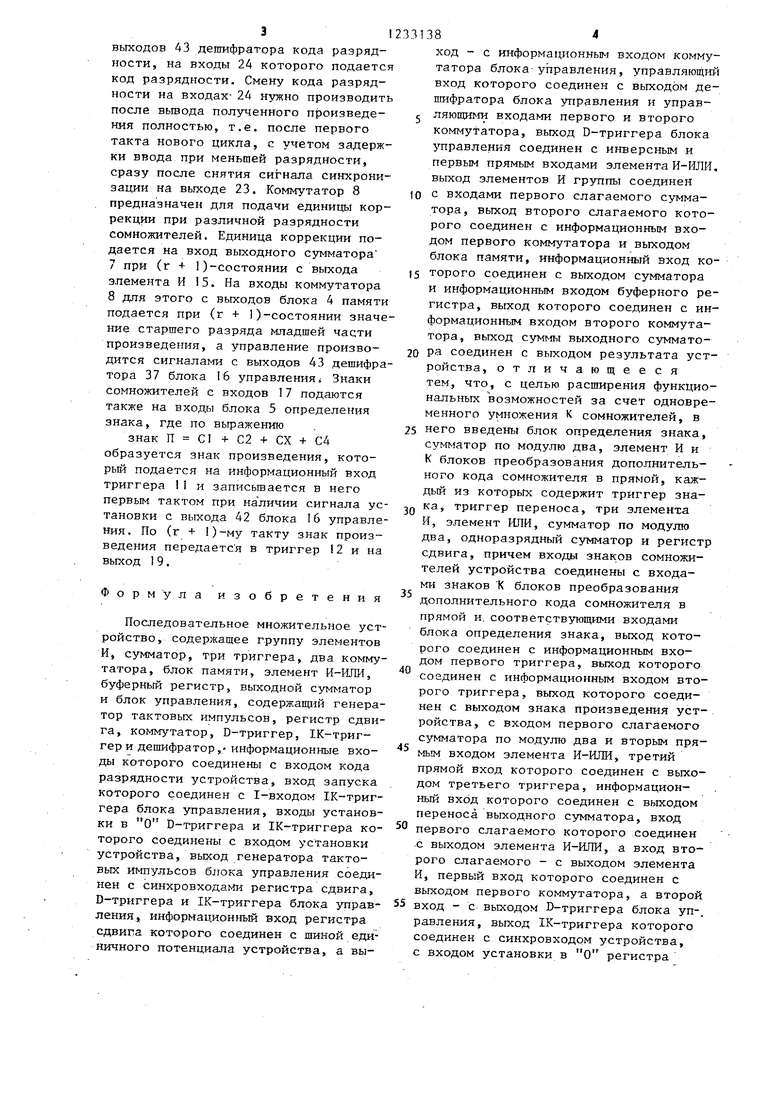

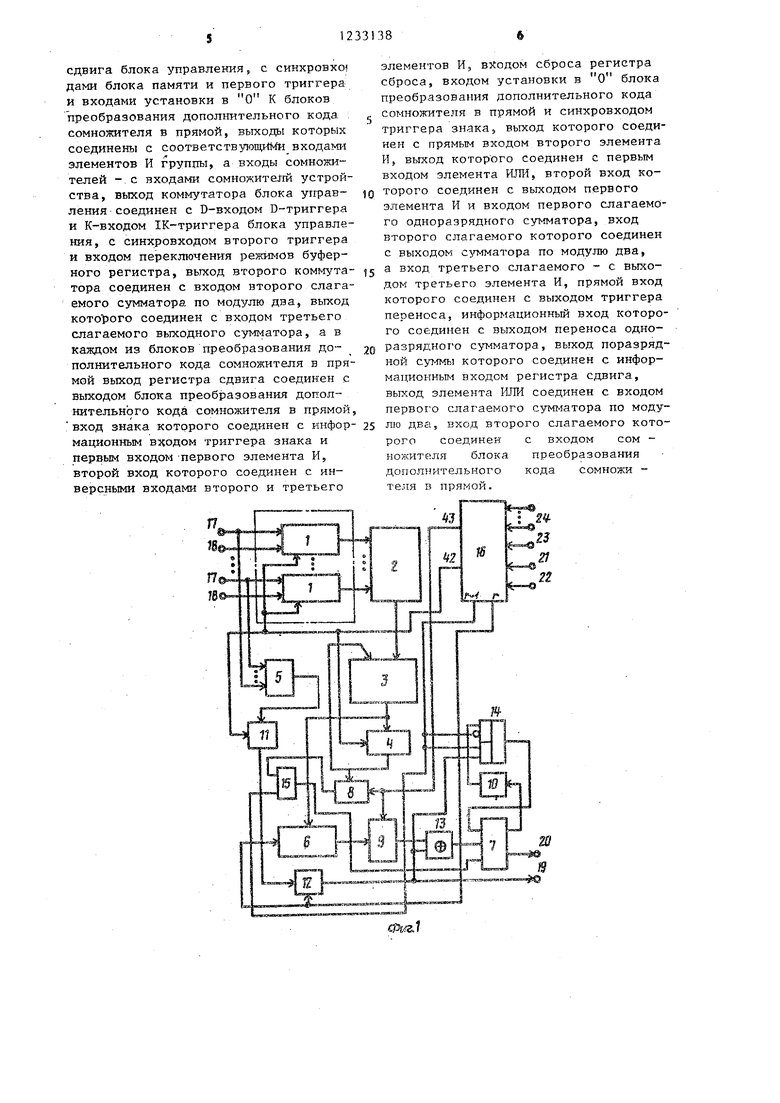

На фиг.. 1 изображена функциональная схема последовательного множительного устройства; на фиг,2 .- функциональная схема блока преобразования дополнительного кода сомножителя в прямой; на фиг.З - схема блока, уп равления.

Устройство (фиг.) содержит К блоков 1 преобразования дополнительного кода сомножителя в прямой, группу элементов И 2, сумматор 3, блок 4 памяти, блок 5 определения знака, буферный регистр 6, выходной сумьштор 7, два коммутатора 8 и 9, три триггера 10-125 сумматор 13 по модулю два, элемент, И-ВДИ 14, элемент И 15, блок 16 управления, входы 17 знаков сомножителей устройства, входы 18 сомно- .- жителей устройства, выход 9 знгпса произведения устройства, выход 2.0 . результата устройства, вход 21 запус- ка устройства, вход 22 установки устройства, выход 23 синхронизации и . входы 24 кода разрядности устройства.

Блок преобразования дополнительного кода сомножителя в прямой (фиг.2) содержит триггеры 25 и 2§ соответственно знака и переноса, три элемента И 27-29, сумматор 30 по модулю два, элемент ИЛИ 31, одноразрядный сумматор 32 и регистр 33 сдвига.

Блок 16 управлегшя (фиг.З) содер- ясит. генератор 34 тактовых импульсов, регистр -35 сдвига, коммутатор 36, дешифратор 37, 1К триггер 38, В-триг гер 39,-выход 40 г-состояния, выход 41 (г + 1)состояния, выход 42 установки и выходы 43 дешифратора кода разрядности. .

Устройство работает следующим образом.

Сомножители подаются в дополнительных кодах младшими: разрядаш вперед, на входь 18. Знаки поступают одновременно с младшими разрядами со- .множителей на входы 17. Сомножители записаны в виде правил11.ных дробей и содержат г разрядов без учета знака. Произведение вьщается в дополнитель

5

0

5

ном коде младшими разрядами вперед, знак выдается по отдельной шине.

С каждым тактом б.олее младший раз- ряд сомножителей замещается в блоках преобразования дополнительного кода сомножителя в прямой более старшим. Частичные произведения второго такта суммируются с результатом первого такта, сдвинутым -на К 4 разряда вправо в сторону младших разрядов, что дает результат второго такта. Затем частичные произведения третьего такта cyls миpyютcя с результатом второго тактаJ сдвинутым.на К 4 разряда вправо, что дает результат третьего такта. Знак сомножителя с входа 1,7 передается на вход одноразрядного сумматора 32 и на вход сумматора 30 по модулю два. Если знак равен единице (сомножитель отрицания), то разряды сомножителя с входа 18 подаются - на вход сумматора 32 инвертированны-. ми. При отрицательном сомножителе на сумматоре 32 образуется его положи- тельшьш эквивалент, который вводится н регистр 33. Положительный сомножитель вводится в регистр 33 без изменения. Значения разрядов регистров 33 через элементы И 2 группы подаются на входы сумматора 3 нескольких чисел, а результат с .его выходов - на соответствующие входы блока 4 памяти, выходы которого соединены с входами сумматора 3 со смещением на К 4 разрядов вправо в сторону младших разрядов. Каждым тактом на выходах сумматора 3 образуется результат данного такта, старшая часть которо- го подается на параллельные входы буферного регистра 6. В это время на вход ра зрешения записи буферного регистра 6 подается г-4остояние с выхода 41 блока 16 управления. По (г -I- )-му такту в буферный регистр

5 6 записывается старшая часть произведения, разряд которой подается через коммутатор 9 на вход выход- ного сумматора 7, а затем на выход 20. На cyMi iaTope 13 по модулю два

Q производится инверсия произведения:, если оно отрицательно, триггер 10 и элемент И-1ШИ 14 служат для запоминайся текущего переноса и введения дополнительной единицы младшего разря;; да при инверсии произведения. Комму-- татор 9 ну7кен для вьгоода произведения КЗ буферного регистра 6 при раз- личной разрядности и управляется с

0

5

0

31

выходов 43 дешифратора кода разрядности, на входы 24 которого подается код разрядности. Смену кода разрядности на входах- 24 нужно производить после вьгоода полученного произведе- кия полностью, т.е. после первого такта нового цикла, с учетом задержки ввода при меньшей разрядности, сразу после снятия сигнала синхронизации на выходе 23. Коммутатор 8 предназначен для подачи единицы коррекции при различной разрядности сомножителей. Единица коррекции подается на вход выходного сумматора

7при (г 1)-состоянии с выхода элемента И 15. На входы коммутатора

8для этого с выходов блока 4 памяти подается при (г + 1)-состоянии значение старшего разряда младшей части произведения, а управление произво- дится сигналами с выходов 43 дешифратора 37 блока 16 управленияi Знаки сомножителей с входов I7 подаются

также на входы блока 5 определения знака, где по вьфажению .

знак П С1 + С2 + СХ + С4 образуется знак произведения, который подается на информационный вход триггера 1 и записьшается в него первым тактом при на личии сигнала ус тановки с выхода 42 блока 16 управления. По (г + I)-му такту знак произведения передается в триггер 2 и на выход 19.

Формула изобретения

Последовательное множительное устройство, содержащее группу элементов И, сумматор, три триггера, два коммутатора, блок памяти, элемент И-ИЛИ, буферный регистр, выходной сумматор и блок управления, содержащий генератор тактовых импульсов, регистр сдвига, коммутатор, D-триггер, 1К-триг- гери дешифратор,-информационные вхо- ды которого соединены с входом кода разрядности устройства, вход запуска которого соединен с 1-входом 1К-триг- гера блока управления, входы установки в О В-триггера и 1К-триггера ко- торого соединены с входом установки устройства, выход генератора тактовых импульсов блока управления соединен с синхровходами регистра сдвига, D-тритгера и 1К-триггера блока управ- ления, информационный вход регистра сдвига которого соединен с шиной единичного потенциала устройства, а вы

)о

i

0

5

„

5

0

0 5

38

ход - с информационным входом коммутатора блока-управления, управляющий вход которого соединен с выходом дешифратора блока управления и управ- ляюшими входами первого и второго коммутатора, выход D-триггера блока ттравления соединен с инверсным и первым прямым входами элемента И-ИЛИ, выход элементов И группы соединен с входами первого слагаемого сумматора, выход второго слагаемого которого соединен с информационным входом первого коммутатора и выходом блока памяти, информационный вход которого соединен с выходом сумматора и информационным входом буферного регистра, выход которого соединен с информационным входом второго коммутатора, выход суммы выходного сумматора соединен с выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет одновременного умножения К сомножителей, в него введены блок определения знака, сумматор по модулю два, элемент И и К блоков преобразования дополнительного кода сомножителя в прямой, каждый из которых содержит триггер знака, триггер переноса, три элемента И, элемент ИЛИ, сумматор по модулю два, одноразрядный сумматор и регистр сдвига, причем входы знак;ов сомножителей устройства соединены с входами знаков К блоков преобразования дополнительного кода сомножителя в прямой и. соответствующими входами блока определения знака, выход которого соединен с информационным входом первого триггера, выход которого соединен с информационным входом второго триггера, выход которого соединен с выходом знака произведения устройства, с входом первого слагаемого сумматора по модулю два и вторым прямым входом элемента И-ИЛИ, третий прямой вход которого соединен с выходом третьего триггера, информационный вход которого соединен с выходом переноса выходного сумматора, вход первого слагаемого которого соединен .с выходом элемента И-ИЛИ, а вход второго слагаемого - с выходом элемента И, первый вход которого соединен с выходом первого коммутатора, а второй вход - с выходом D-триггера блока уп-. равления, выход 1К-триггера которого соединен с синхровходом устройства, с входом установки в О регистра

сдвига блока управленияs с синхровхо дами блока памяти и первого триггера и входами установки в О К блоков преобразования дополнительного кода сомножителя в прямой, выходь которых соединены с соответствующими входами элементов И группы, а входы сомножителей -, с входами сомножитехгй устройства, выход коммутатора блока управления соединен с D-входом D-триггера и К-входом 1К-триггера блока управления, с синхровходом второго триггера и входом переключения реясимов буферного регистра, выход второго коммута- тора соединен с входом второго слагаемого сумматора по модулю два, выход которого соединен с входом третьего слагаемого выходного с умматора, а в каждом из блоков преобразования до- полнительного кода сомножителя н прямой выход регистра сдвига соединен с выходом блока преобразования дополнительного кода сомножителя в прямой вход знака которого соединен с инфор- мационным входом триггера знака и первьвм входом -первого элемента И, второй вход которого соединен с инверсными входами второго и третьего

элементов И, сброса регистра сброса, входом установки в О блока преобразования дополнительного кода сомножителя в прямой и синхровходом триггера знака, выход которого соединен с прямым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и входом первого слагаемого одноразрядного сумматора, вход второго слагаемого которого соединен с выходом c-STviMaTopa по модулю два, а вход третьего слагаемого - с выходом третьего элемента И, прямой вход которого соединен с выходом триггера переноса, информационный вход которого соединен с выходом переноса одноразрядного сумматора, выход поразрядной которого соединен с информационным входом регистра сдвига, выход элемента РШИ соединен с входом первого слагаемого сумматора по модулю два, вход второго слагаемого которого соединен с входом сом - ножитешя блока преобразования допол ительного кода сомножи - теля в прямой.

Редактор И.Николайчук

Составитель Е.Захарченко

Техред Л.Олейник Корректор Е.Рошко

Заказ 2771/50 ,Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по .делам изобретений и открытий И3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

Изобретение относится к области вычислительной техники и предназначено для одновременного умножения нескольких синхронно поступающих младшими разрядами вперед двоичных чисел. Целью Изобретения является расширение функциональных возможностей за счет одновременного умножения нескольких чисел. Устройство перемно жает К синхронно поступающих младшими разрядами вперед двоичных чисел, знаки чисел подаются одновременно с младшими разрядами чисел. Произведение выдается младшими разрядами вперед, знак произведения вьщается по отдельной шине. Цикл умножения состоит из (г + 1) такта, все такты одинаковой длительности. Устройство может работать с числами различной разрядности, определяемой кодом разрядности, максимальная разрядность чи- ил. а S (/)

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969 | |||

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-10-05—Подача