первые выходы которых соединены соответственно с входами элементов памяти первой группы, вторые выходы сумматоров второй группы соединены соответственно с входами элементов памяти второй группы, первые выходы З-т сумматоров второй группы соединены соответственно с входами Ll-()l разрядов первоготраэрядного буферного регистра, вход т-го разряда которого соединен с выходом т- го элемента памяти первой группы, вторые выходы 4-ni сумматоров второй группы соединены соответственно с входами tl-(m-2)l разрядов второгот-разрядного буферного регистра, входы т-1 и т-го разрядов которого соединены с.шиной нулевого потенциала, выходы t 1-(14-1)1-го элементов памяти первой группы соединены соответственно с третьими входами (3-tn)-ro сумматоров второй группы, третьи входы первого, ивторого сумматоров которой соединены с шиной нулевого потенциала, выходы элементов памяти второй группы соединены соответственно с третьими входами сумматоров первой группы, выходы l(im+l)-(К.+1 )1 элементов памя ти первой группы соединены соответственно с m-k входами первого ftn-к.)канального селектора устройства, выходы пп-к разрядов первого буферного регистра-соединены соответственно с т- входами второго (tn-к)-канального селектора устройства, выход которого соединен с первым входом первого одноразрядного сумматора, выходы tn-. разрядов второго буферного регистра соединены соответственно с M-vi. входами третьего (т-к.)канального релектора устройства, выход которого соединен с вторвал входом первого одноразрядного сумматора, выходы первого, второго и третьего триггеров соединены соответственно с первым, вторым и тре-, тьим входами второго одноразрядного сумматора, первый выход которого соединен с третьим входом первого одноразрядного сумматора, а второй

выход соединен с первым входом элемента И-ЙЛИ, второй и третий входы элемента И-ИЛИ объединены и соединены с входами разрешения записи первого и второго буферных регистров, тактовыми входами четвертого и пятого триггеров, первым входом первого элемента И и с вторым выходом синхронизации блока управ ления, четвертый вход элемента И-ИЛИ соединен с выходом (nvк)-канального селектора устройства, пятый вход элемента И-ИЛИ соединен с выходом четвертого триггера и его первым установочным входом, шестой вход элемента И-ИЛИ соединен с первым входом второго элемента И it с выходом индикации окончания операции блока управления, выход пятого триггера соединен с его первым установочным входом и с вторым входом второго элемента И, выход которого соединен с установочным входом первого триггера, выход элемента И-ИЛИ соединен с установочным входом второго триггера, первый выход первого одноразрядного сумматора соединен с вторым входом первого элемента И, выход которого соединен с установочным входом третьегб триггера, второй выход первого одноразрядного сумматора является выходом устройства, вторые установочные входы четвертого и пятого триггеров соединены соответственно с выходами nepBtjx разрядов первого и второго регистров сомножителей, т-к. выходы дешифратора блока управления соединены соответственно с управлякхцими входами первого, второго и третьего (т-к)-канальных селекторов устройства, выкоды регистра блока управления соединены соответственно с установочными входами CCH+l) - (гп+1)1-го разрядов первого и второго регистров сомножителей, первый выход синхронизации блока управления соединен с входами разрешения записи первого и второго регистров сомножителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательное множительное устройство | 1982 |

|

SU1156065A1 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для одновременного вычисления двух многочленов | 1987 |

|

SU1439580A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

ПОСЛЕДОВАТЕЛЬНОЕ МНОЖИТЕЛЬ НОЕ УСТРОЙСТВО, содержащее первый и второй регистры сомножителей, группу элементов И, первую группу из m одноразрядных сумматоров, ;первый и второй элементы И, первый и второй одноразрядные сумматоры, первый, второй и третий триггеры,;} причем разрядные выходы первого и второго регистров сомножителей соединены соответственно с первыми и вторыми входами элементов И группы, выходы которых соединены соответственно с первыми и вторьми входами сумматоров первой группы, о т ли чающееся тем, что, с целью повышения быстродействия устройства за счет уменьшения времени длительности такта, в него введены первый и второй т-разрядные буферные регистры, вторая группа иэ m+l одноразрядных су влаторов, первая и вторая группы изгп+1 элементов памяти, первый, второй и третий (т-V)-канальные селекторы, четвертый и пятый триггеры, элемент И-ИЛИ и блок управления, содержащий генератор тактовых импульсов, регистр, первый и втордй элементы ИЛИ, (т-О-канальный селектор, дешифратор, первый и второй Ь -триггеры, Э -триггер, причем выход генератора тактовых импульсов соедданен с тактовыми входами регистра, первого и второго 1 -триггеров, . di -триггера и является тактовьам выходом блока управления,т-ь входы (т-к.) -канального селектора соединены соответственно с выходами (m-l)-()T разрядов регистра и являются выходами блока управления, первый вход первого элемента ИЛИ соединен с входом внешней синхронизации блока управления, а выход первого элемента ИЛИ соединен с входом установки в единицу первого D-триггера и является первым выходом синхронизации блока управления, выход первого D-триггера соединен с входами установки в единицу второго В-триггера, Э -триггера и явля§ ется вторым выходом синхронизации блока управления, входы установки в ноль первого и второгоТ)-триггеров и вход сброса 3 -триггера объединены и соединены с установочньм входом блока управления,..первый вход второго элемента ИЛИ соединен „. с выходом первого Т5-триггера, второй вход второго элемента ИЛИ соединен с инверсным выходом 3(-триггера, Q Л 1 который является третьим выходом синхронизации блока управлеиия, а выход второго элемента ИЛИ соединен с входом установки в ноль СП регистра, вход установки в ноль ЗК.-триггера является входом запуска блока управления, а его прямой выход - установочньм выходом блока управления, выход второгоD-триггера является выходом индикации окончания операции блока управлеиия, I О9г (-)1 входы дешифратора являются входами кода разрядности блока управления, выходы дешифратора соединены с управляющими входами (т-к.)-канального,селектора и являются выходами блока управления, причем первые и вторые выходы сумматоров первой группы соединены соответственно с первыми и вторыми входгикщ сумматоров второй группы.

f

Изобретение относится к области вычислительной техники и предназна-, чено для умножения чисел, поступающих синхронно в дополнительном коде младшими разрядами вперед.

Известно устройство для умножения.п-разрАдных чисел, поступаквдих в дополнительном коде младшими-разрядами вперед, содержащее регист1%1 множимого и множителя, группу элементов И, группу последовательных одиоразрщ(ных сумматоров, отдельные элементы И, ИЛИ Cl ,

Недостатком данного устройства является пропуск половины рабочих циклов умножения, в течение которых

Ъыдаются младшие разряды произведения и логарифмическая зависимость длительности такта от разрядности чисел.

Наиболее близким по технической сущности к изобретению является устройство для умножения последовательных п-разрядных двоичных кодов, содержащее п-разрядный распределитель, ()-разрядный сдвиговый регистр, первую и вторую группу элементов И, группу последовательных одноразрядных сумматоров, первый и в торой 1Н. -триггеры, элемен т ИЛИ, элемент задержки, первый последовательный одноразрядный сумматор,, первый элемент И, второй последовательный одноразрядный сумматор, (п-1)-разрядный статический регистр каждый единичный разрядный вход которого соединен с выходом соответствукидего элемента И первой группы, а каждый единичный разрядный выход подключён к первому входу соответствующего элемента И второй группр, информационный вход )разрядного сдвигового регистра соединен с шиной множимого и вторым входом первого элемента И второй группы, единичный выход 1-го разряда сдвигового регистра подключен к второму входу (1+1)-го элемента И второй группы (I а 1,2,.. ,п -1) , выосод (i. +1) -го элемента И второй группы соединен с первым входом I -го последовательного одноразрядного сукматора группы, единичный вход разряда п -разрядного распределителя подключен к первому входу {1.+1)-го элемента И первой груп гаа, причем первый вход первого элемента И первой группы и вход тэаспределителя соединены с выходом элемента ИЛИ, один из входов которого подключен к шине управления, а другой вход подсоединен к элементу задержки, выход которого связан с единичным выходом -ГО разряда распределителя, вторые входы элементов И первой группы подключены к шине множителя, а входы синхронизации первого и второго 1Ц, Триггеров соединены с единичным выходом (п-1)-го разряда распределителя, причем информационньй вход первого TH-триггера подключен к шине множимого, а информационный вход второго ТН-триггера соединен с ШИНОЙ множителя, единичный выход (п-1)-го разряда распределителя под ключей к первому входу первого последовательного одноразрядного сумматора, второй вход которого подключен к нулевому выходу последне.го разряда сдвигового регистра, а вход соединен с первым входом первого элемента И, второй вход которого подключен к единичному выходу второго D -триггера, а выход соединен с первым входом второго последовательного одноразрядного сумматора, третью группу элементов И, груп|Пу элементов НЕ, три дополнительных последовательных одноразрядных сумматора, три дополнительных элемен.ти Ии один дополнительный элемент НЕ US-триггер и f -разрядный элемент

задержки, нулевой вход г-го разряда| статического регистра соединен с единичным выходом (i-3)-ro разряда распределителя, причем нулевой вход первого разряда статического

регистра подключен к единичному выходу ()-го разряда распределителя, нулевой выход второго разряда статического регистра соединен с единичным выходом п-го разряда.распределителя, а нулевой вход третьего разряда статического регистра подключен к выходу элемента ИЛИ, шина множителя через последователь- но соединенные (Л-разрядный элемент

задержки и дополнительный элемент НЕ связана с первым входом первоЛ) дополнительного последовательного . сумматора, второй вход которого подключен к единичному выходу ( разряда распределителя, а выход

подключен к первому входу первого дополнительного элемента И, второй вход которого подсоединен к единичному выходу первого TH Триггера, а его выход соединен с первым входом

второго дополнительного последовательного однораз.рядного cyNwaTopa, второй вход которого подключен к выходу второго последовательного одноразрядного сумматора, а выход

соединен с первил входом третьего дополнительного одноразрядного сумматора, второй вход; которого подключен к выходу второго дополнительного элемента И, а выход соедийен с первым входом третьего дополнительного элемента И, второй вход которого подключен к единичному выходу -триггера, а выход соединен с шикой произведения, причем нулевой и единичный входы Яз-триггера

соединены соответственно с единичными выходами (п-2)-го и (n-l) разрядов распределителя, входы второго дополнительного элемента И подключены к единичным выходам Ъ триггеров и к единичнсдасу выходу (п-З)-го разряда распределителя, первый вход v-ro элемента И третьей группы подсоединен к входу соответствующего элемента НЕ группы/ выход

которого соединен с единичным выходом (i-l)-ro разряда распределителя, а другой вход подключен к выходу (i-l)-ro последовательного одноразрядного сумматора группы, а

выход соединен с вторым входом

«--го последовательного одноразрядного сумматора группы, причем первый вход первого элемента И третьей группы через соответствующий элемент НЕ группы соединен с выходо элемента ИЛИ, другой вход подключен к выходу первого элемента И второй группы, а выход соединен с вторым входом первого последовательного одноразрядного сумматора группы, выход последнего элемента И третьей группы подключен к второму входу второго последовательного одноразрядного сумматора, причем нулевые входы Dt-триггеров соединены с единичным выходом (п-2)го разряда распределителя С 2.

Недостатками этого устройства являются большая длительность такта соответствующая максимальному времени пробега сигнала по последовательной суммирующей цепи, и зависимость длительности такта от разрядности сомножителей.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается те что в последовательное множительное устройство, содержащее первый и второй регистры сомножителей, группу элементов И, первую группу из гг одноразрядных сумматоров, первый и второй элементы И, первый и второй одноразрядные сумматоры, первый, второй и третий триггеры, причем разрядные выходы первого и второго регистров сомножителей соединены соответственно с первыми и вторыми входами элементов И группы, выходы которых соединены соответственно с первыми и вторыми входами сумматоров первой группы, введены первый и второй т-разрядные буферные регистры, вторая группа из т+1 одноразрядных сумматоров, первая и вторая группы из и+1 элементов памяти, первый, второй и третий ( )канальные селекторы, четвертый и пятый триггеры, элемент И-ИЛИ и блок управления, содержащий генератор тактовых импульсов, регистр, первый и второй элементы ИЛИ, (m-tc)-канальный селектор, дешифратор, первый и второй 7)-триггеры, ок.-триггер, причем выход генератора тактовых импульсов соединен с тактовыми входами регистра, первого и второго В-триггера,ЗК-триггера и является тактовым выходом блока уп равления, пл-к входы (m-v)-канальног селектора соединены соответственно выходами L(m-l)-(к-1)1 разрядов регистра и являются выходами блока управления, первый вход первого элемента ИЛИ соединен с входом внешне синхронизации блока управления, а вход первого элемента ИЛИ соединен с

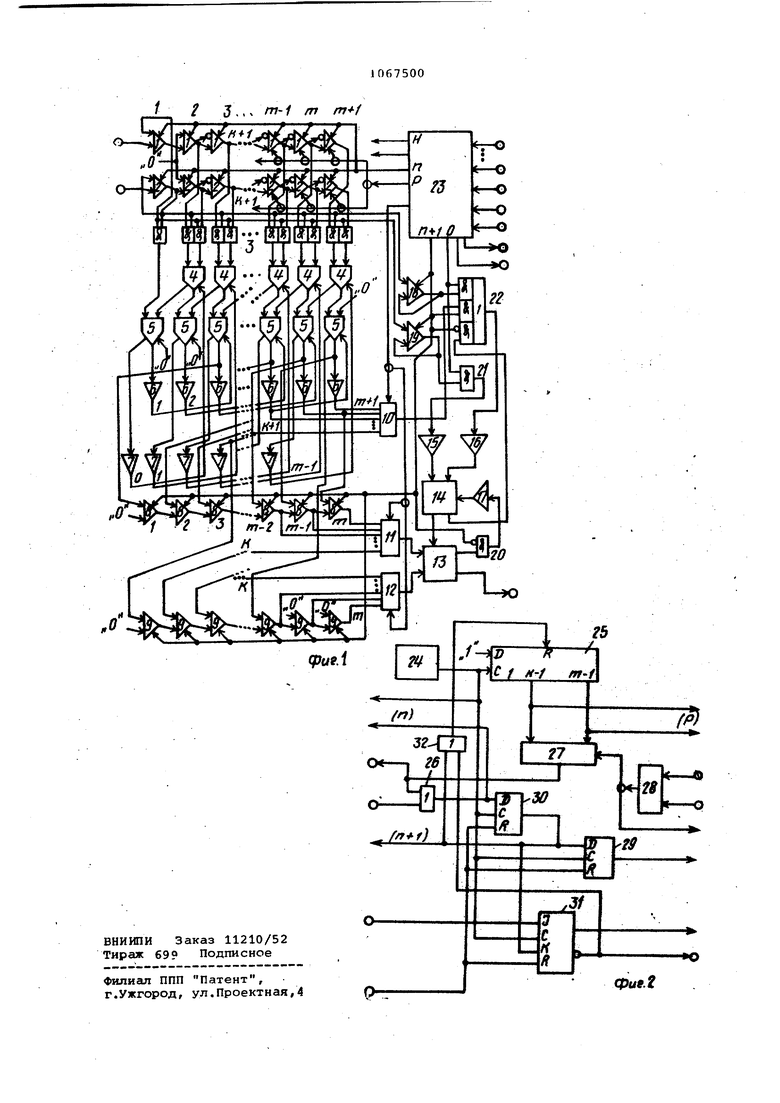

входом установки в единицу первого D-триггера и является первым выходо синхронизации блока управления, выход первого ts-триггера соединен с входами установки в единицу второго D-триггера, Oti -триггера и является вторым выходом синхронизации блока управления, входы установки в ноль первого и второго Т5-триггеров и вхо сброса ЦК--триггера объединены и соединены с установочным входом блока управления, первый вход второго элемента ИЛИ соединен с выходом первого З)-триггера, второй вход второго элемента ИЛИ соединен с инверсным выходом Jls.-триггера, который является третьим выходом синхронизации блока управления, а выход второго элемента ИЛИ соединен с входом установки в ноль регистра, вход установки в ноль 1 -триггера является входом запуска блока управления,, а его прямой выход - установочным выходом блока управления, выход второго D-триггера является выходом индикации окончания операции блока управления, tog, (m-i) входы дешифратора являются входами кода разрядности блока управления, управляющие входы (т-к)-канального селектора являются выходами блока управления, причем первые и вторые выходы cyTviMaTopOB первой группы соединены соответственно с первыми и вторыми входами сумматоров второй группы, первые выходы которых сое-, динены соответственно с входами элементов памяти первой группы, вторые выходы сумматоров второй группы соединены соответственно с входами элементов памяти второй группы, первые выходы З-т сумматоров второй группы соединены соответственно с входами l-(m-l)l разрядов первого wi-разрядного буферного регистра, вход tn-ro разряда которого соединен с ззыходом tn-ro элемента памяти первой группы, вторые выходы 4-т сумматоров второй группы соединены соответственно с входами l-(tn-2)l разрядов второго m-разрядного буферного регистра, входы т-1 и т-го разрядов которого соединены с шиной нулевого потенциала, выходы 1-(т-1го элементов памяти первой группы соединены соответственно с третьими входами {3-т)-го сумматоров второй группы, третьи входы первого и второго сумматоров которой соединены с шиной нулевого потенциала. выходы элементов памяти второй группы соединены соответственно с третьими входами сумматоров первой группы Выходы {tri+l) - (vt +1) элементов памяти первой группы соединены соответственно с т-к входами первого (т-к)-канального селектора устроййтва, выходы m-ii разрядов первого буферного регистра соединены соответственно с m-tc входами второго (ftl-к)-канального селектора устройства, выход которого соединен с-пер вым входом первого одноразрядного сумматора, выходы т-к разрядов второго буферного регистра соединены соответственно с т-к входами третьего (т-)-канального селектора устройства, выход которого соединен с вторым входом первого одноразрядного сумматора, выходы первого, второго и третьего триггеров соединены соответственно с первым, вторим и третьим входами первого одноразрядного сумматора, первый выход которого соединен с третьим входим первого одноразрял ного сумматора, а второй выход соединен с первым входом элемента И-ИЛ второй и третий входы элемента И-ИЛ объединены и соединены с входами разрешения записи первого и второго буферных регистров, тактовыми входами четвертого и пятого триггеров, первым входом первого элемента И и с вторым выходом синхронизации блока управления,- четвертый вхб элемента И-ИЛИ соединен с выходом (т-к.)г канального селектора устройст ва, пятый .вход элемента И-ИЛИ соеди нен с выходом четвертого триггера и с его первым установочным входом, шестой вход элемента И-ИЛИ соединен с первым входом второго элемента И и с выходом индикации окончания one рации блока управления, выход пятого триггера соединен с его первым установочным входом и с вторым входом второго элемента И, выход которого срединен с установочным входом первого триггера, выход элемента И-ИЛИ соединен с установочным входо второго триггера, первый выход первого одноразрядного сумматора соединен с вторым входом первого элемента И, выход которого соединен с установочишл входом третьего тригге ра, второй выход первого одноразряд ного сумматора явлйется выходом уст ройства, вторые установочные входы четвертого и пятого триггеров соединены соответственно с выхода первых разрядов первого и второго регистров сомножителей, 1-IS. staxomi дешифратора блока управления соединены соответственно с управляспцими входами первого, второго и третьего )-канальных селектсчров устройства, выходы регистра блока управления соединены соответственно с установочными входами С(+1)- (w+1 )J го разрядов первого и второго рехтистров,.сомножителей, первый выход синхранизации блока управления соединеи с входами разрешения записи первого и второго регистров сомножителей На фиг.1 представлена функциональная схема устройства; на фиг.2 функциональная схема блока управления. Устройство содержит первый и второй регистры 1,2 сомножителей, группу элементов И 3, первую и вторую группы одноразрядных сумматоров 4,5, первую и вторую группы элементов 6,7 памяти, первый и второй буферные регистры 8,9, первый, второй и третий )-канальные селекторы 10-12, первый и второй одноразрядные суммат.оры 13,14, первый-пятый триггеЕЯЛ 15-19, первый и второй элементы И 20,21, элементы И-ИЛИ 22 И блок 23 управ ле ни я, причем разрядные выходы первого и второго регистров 1,2 сомножителей соединены соответственно с первыми и вторыми входами элементов И 3 группы, первые н вторые вы- , ходы сумматоров 4 первой группы соединены соответственно с первыми и вторыми входами сумматоров 5 второй группыf первые выходы которых соединены соответственно с входа ми с . элементов 6 памяти первой групгйл, вторые выходы сумматоров 5 второй группы соединены соответственно : входами элементов 7 памяти второй группы, первые выходы З-гп Сумматоров 5 второй группы соединены соответственно с входами 11-|tn-l)1 разрядов первого буферного регистра 8, . вход т-го разряда которого соединен с выходом т-го элемента Б памяти первой группы, вторые выходы 4-т суьолатороа 5 второй группы соединены соответственно с входами Cl-(tn-2)l разрядов второго буферного регистра 9, входы tn-1 и tn-ro разрядов которого соединены с шиной нулево го пот енци ала, выходы 11 - (in-1)1го элементов 6 .памяти первой группы соединены соответственно с третьими входами З-т сугФлаторов 5 второй группы, третьи входы первого и второго сумма ачэроь которой соединеиы с шиной нулевого потенциала выхода элементов 7 памяш второй группы соединены соответственно с третьими входами сумматоров 4 первой группы, . выходы .(m+l)-{ti.+in эяемемтов 7 памяти второй группы сседивены соответственно с входами первого ftn-K.)- канального сеяектора 10, выходы разрядов первого вуферного регистра 8соединены соответственно с т-к входэ второго (ад-к)-канальиого селектоЕ а 11, выход которого соединен с первым входсм первого одноразрядиохю сумматора 13, выходы tn-« разрядов второго буферного регистра 9 соединены соответственно с to-fc входами третьего (т-к)-каналыч ного селектора 12, выход которого соединен с вторым входсвд первого однораэрядного сумматора 13, выходы триггеров 15-17 соединены соответственно с входами второго одноразрядного сумматора 14, первый выход которого соединен с третьим входом одноразрядного сумматора 13, а второй выход соединен с первым входом элемента И-ИЛИ 22, второй и третий входы элемента И-ИЛИ 22 объединены и соединены с входами разрешения записи первого и второго буферных регистров 8,9, тактовыми входами триггеров 18,19, первым входом первого элемента И 20 и с вторым выходом синхронизации блока 23 управления, четвертый вход элемента И-ИЛИ 22 соединен с выходом (т-«)-канального селектора 10, пятый вход элемента И-ИЛИ 22 соединен с выходом четвертого триггера 18 и его первым установочным входом, шестой вход элемента И-ИЛИ 22 соединен с первьш входом второго элемента И 21 и с выходом индикации окончания операции блока 23 управления, выход пятого триггера 19 соединен с его первым установочным входом и с вторым входом второго элемента И 21, выход которого соединен с установочным входом первого триггера 15, выход элемента И-ИЛИ 22 соединен с установочным входом второго триггера 16, первый выход первого одноразрядного сумматора. 13 соединен с вторым входом первого элемента И 20, выход которого соединен с установочным входом третьего триггера 17, второй выход первого одноразрядного сумматора 13 является выходом устройства вторые установочные входы триггеров 18,19 соединены соответственно с выходами первых разрядов первого и второго регистров 1,2 сомножителей, т-к, выходы дешифратора блока 2 управления соединены соответственно с управляющими входами (т- к) -канальных селекторов 10-12, выходы регистра блока 23 управления соединены соответственно с установочными вхо дами (к+1) - (rn-fl)}-го разрядов первго и второго регистров 1,2 сомножителей, первый выход синхронизации блока 23 управления соединен с входами разрешения записи первого и ,второго регистров 1,2 сомножителей

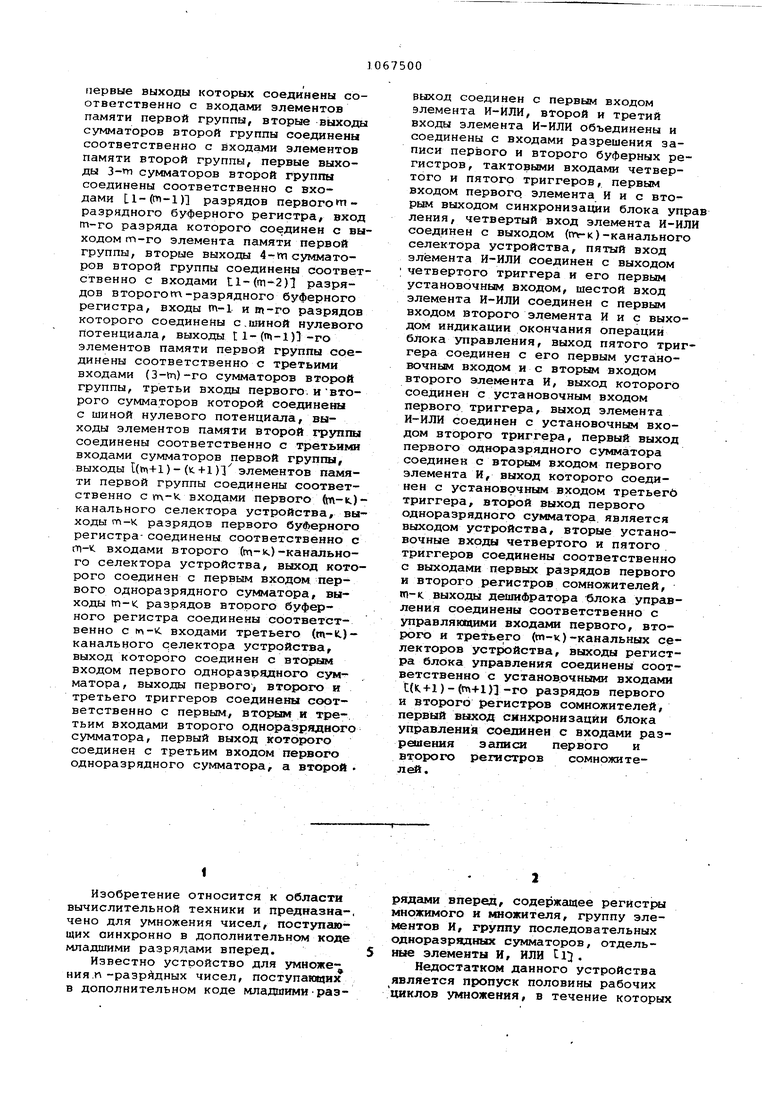

Блок 23 управления содержит генератор 24 тактовых импульсов , регистр 25, первый элемент ИЛИ 26, (iri-K.)-канальный селектор 27, дешифратор 28, первый и второй D-триггеры 29,30,Jls-триггер 31 и второй элемент ИЛИ 32, причем выход генератора 24 тактовых импульсов соединен с тактовыми входами регистра 25 первого и второго Т5-триггеров 29, 30,ЛК -триггера 31 и является тактовым выходом блока 23 управления, т-к входы (т-)-канального селектора соединены соответственно с выходами С(11-1) - (.-1) разрядов регистра 25 и являются выходами блока 23 управления, первый вход первого элемента ИЛИ 26 соединен с выходом (т-1C)-канального селектора 27, второй вход первого элемента ИЛИ 26 соединен с входом внешней синхронизации блока 23 управления, а выход первого элемента ИЛИ 26 соединен с входом установки в единицу первого Ь-триггера 29 и является первым выходом синхронизации блока 23 управления, выход первого D-триггера 29 соединен с входами установки в единицу второго D-триггера 30,ЗК-триггера 31 и является вторым выходом синхронизации блока 23 управления, входы установки в ноль первого и второго В-триггеров 29,30 и вход сброса Ж-триггера 31 объединены и соединены с установочным входом блока 23 управления, первый вход второго элемента ИЛИ 32 соединен с выходом первого D-триггера 29, второй вход второго элемента ИЛИ 32 соединен с инверсным выходом ЗК-триггера 31, который является третьим выходом синхронизации блока 23 управления, а выход второго элемента ИЛИ 32 соединен с входом установки в ноль регистра 25 вход установки в ноль JK-триггера 31 является входом запуска блока 23 управления, а его прямой выход установочным выходом блока 23 управления, выход второго D-триггера 30 является выходом индикации окончания операции 23 управления, вхо-. ды дешифратора 28 являются входами кода разрядности блока 23 управ,ления, а управляющие входы ((п-К)-канального селектора 27 соединенные .соответственно с выходами дешифратора 28, являются выходами блока 23 управления.

Устройство работает следующим образом.

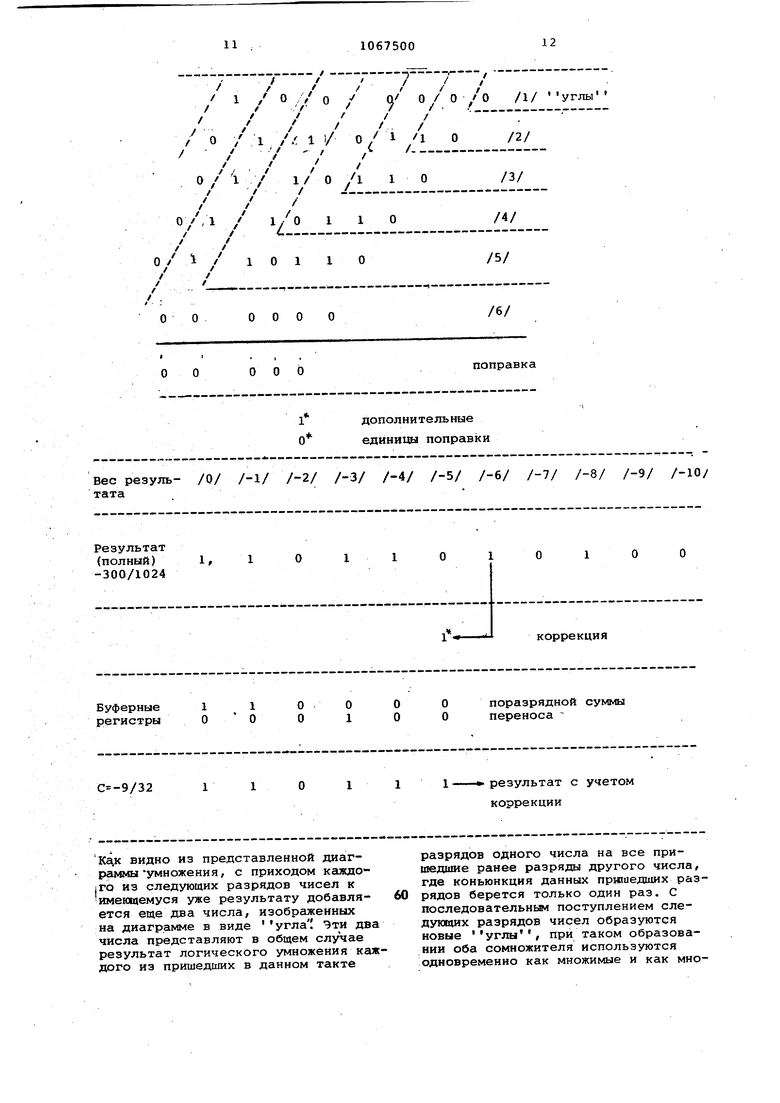

В качестве примера возьмем умножение двух шестираэрядных чисел, выраженных в виде правильных дробей в дополнительном коде Х -10/32, Y 30/32. Результат умножения C XY -300/1024- 9/32 . Вес чисел /О/ /-1/ /-2/ /-3/ /-4/ /X -;iO/32 1. 1 О 1 1 О У 30/32 0. 1 1 1 1 О

000

О О Вес резуль- /О/ /-1/ /-2/ /-3/ /-4/ тата

С -9/32

1 видно из представленной диаграммы умножения, с приходом калщо(Го из следующих разрядов чисел к имеющемуся уже результату добавляется еще два числа, изображенных на диаграмме в виде угла1 Эти дв числа представляют в общем случае результат логического умножения ка дого из пришедших в данном такте

поправка

дополнительные единицы поправки

результат с учетом коррекции /-5/ /-6/ /-7/ /-8/ /-9/ /-10/ разрядов одного числа на все пришедшие ранее разряды другого числа, где коньюнкция данных пришедших раз рядов берется только один раз. С последовательным поступлением следующих разрядов чисел образуются новые углы, при таком образовании оба сомножителя используются одновременно как множимые и как мно жители. Пусть до прихода младишх разрядов чисел есть два числа, выраженные нулями. После прихода мла ших разрядов к этим числам добавляется /1/ угол. Образуем из них два числа результата, полученн с запоминанием переносов, в виде поразрядных сумм и переносов. Посл прихода следующих разрядов к двум числам результата первого такта до бавляются два числа /2/ угла. Образуем из этих четырех чисел следующие два числа результата вто рого такта в виде поразрядных сумм и переносов. С приходом следующих разрядов процесс образования двух чисел результата из четырех исходных .повторяется. При образовании двух чисел результата очередного такта сигнал распространяется через данный и следующий за данным разряды, т.е. через два одноразрядных сумматора. До прихода знаковых разрядов этот процесс повторяется без изменения, п пактом записываются знаковые разряды и образуются два числа результата п такта. Следующим п+1 тактом к двум числам результата п такта нужно добавить два числа поправк и получить результат п +1 такта также в виде двух чисел. Для получения поправки в п+1 такте необходимо оп делить коньюнкцию знаковых разрядов каждого из чисел на все ранее пришедшие разряды другого числа, взятые в инверсном значении. Таким образом, для получения результата с учетом поправки в виде; двух чисел по п +1 такту нужно произвести ин-, версный сдвиг чисел, в этом случае поправка получится в виде угла приче м, в первых разрядах регистров приема сомножителей нужно запомнить значения знаковых разрядов, а во в рые разряды записать нули. Регистры сомножителей должны .иметь для этого m+l разряд и требуемую коммутирующую логику. Процесс умножения с пол чением двух чисел результата для чи сел приведенного примера представлен и рассмотрен в таблице состояНИИ. После п+1 такта образуются дв числа, для получения общего результата умножения нужно сложить эти два числа вместе со значениями дополнительных единиц поправки и значением старшего разряда младшей части результата (коррекции). Полученное значение является общим результатом умножения с учетом коррекции. Для этого оба числа результата п+1 такта переписываются по п+2 такту в буферные регистры 8,9, младшие их разряды подаются на входы дополнительного сумматора 13, а значение коррекции подается на сумматор 14, на выходе устройства получается младший разряд результата. Приемная часть устройства готова к умножению следующих чисел, одновременно с их умножением выдается результат предыдущего цикла. После первого такта на сумматор 14 подаются дополнительные единицы поправки, затем с каждым тактом происходит вывод результата из буферных регистров 8,9. После n-j такта на выходе появляется значение знакового разряда результата. Таким образом, при умноженииоба сомножителя используются одновременно как множимые и как множители. Результат умножения формируется в два этапа, сначала одновременно с вводом чисел получают два числа первого этапа, затем из двух чисел первого этапа, единиц поправки и коррекции последовательно получают результат умноженяя в виде одного числа. Младший разряд результата появляется на выходе в одном такте с подачей младших разрядов следующих чисел. Цикл умножения состоит из п+2 тактов, каждый такт имеет постоянную длительность, не зависящую от разрядности чисел п и равную Т где t - время пробега сигнала через одноразрядный сумматор, tu. - время пробега сигнала через элемент И„ Наибольший технико-экономический эффект от применения предлагаемого множительного устройства можно получить при его реализации в виде набора интегральных микросхем (с ведущими и ведомыми устройствами), так как высокое быстродействие при непре клвном цикле работы делают его универсальным последовательным умножителем чисел, записанных в дополнительных кодах,, что, в свою очередь, позволит унифицировать типы последовательных умножителей.

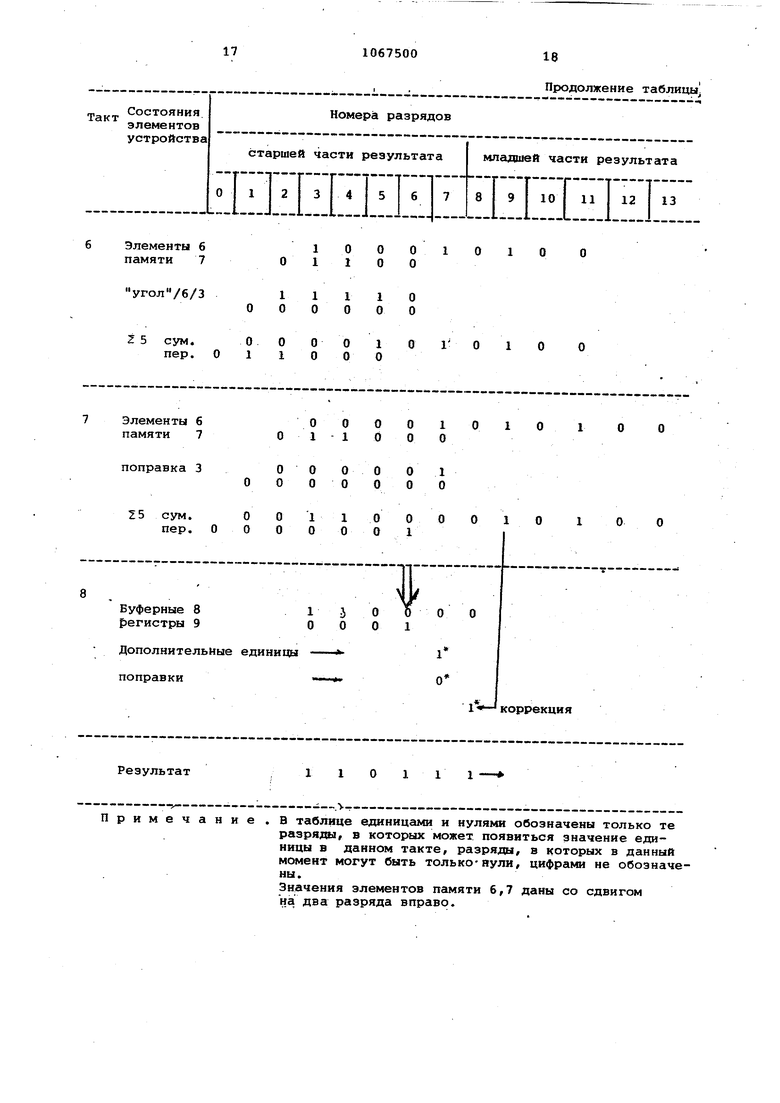

Состояния Такт элементов устройства

старшей части результата

1:.1....1..1....1:.1..1..1..1.1

Элементы 6 памяти 7

L5 сум. пер.

00

Элементы б памяти 7

угол /2/3

О О

15 сум.

1

пер. О

О

Элементы 6

1 О памяти 7

О О

5 сум.О

О О

пер. 1 О

угол /4/3

О 1

О

1

15 сум.101

пер. 00 О О

Элементы 6

1

О памяти 7

1 О

5 сум.

О 1

О О пер.

Номера разрядов

младшей части результата

12 13 Примечание

Продолжение таблицы В таблице единицами и нулями обозначены только те разряда, в которых может появиться значение единицы в данном такте, разряды, в которых в данный момент могут быть только-нули, цифрами не обозначены. Значения элементов памяти 6,7 даны со сдвигом на два разряда вправо.

/ 5.,х m-/ /7т

U

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Приспособление для отопления печей нефтью | 1922 |

|

SU458A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения последовательных п-разрядных двоичных кодов | 1978 |

|

SU769541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-15—Публикация

1981-12-23—Подача