Изобретение относится к вычислительной технике, может быть использовано при разработке быстродействующих устройств умножения чисел, удобных для изготовления в составе больших интегральных схем (БИС), и является усовершенствованием устройства по авт.сво № 888109с

Цель изобретения - повышение достоверности результата вычислений устройства.

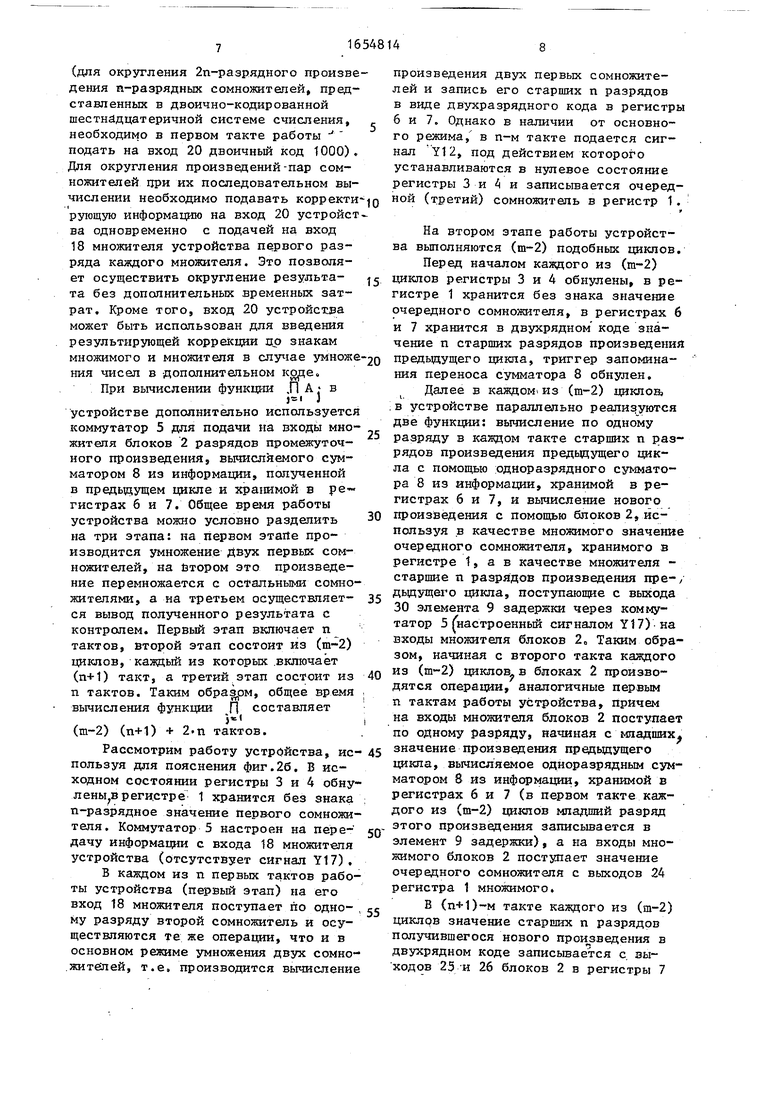

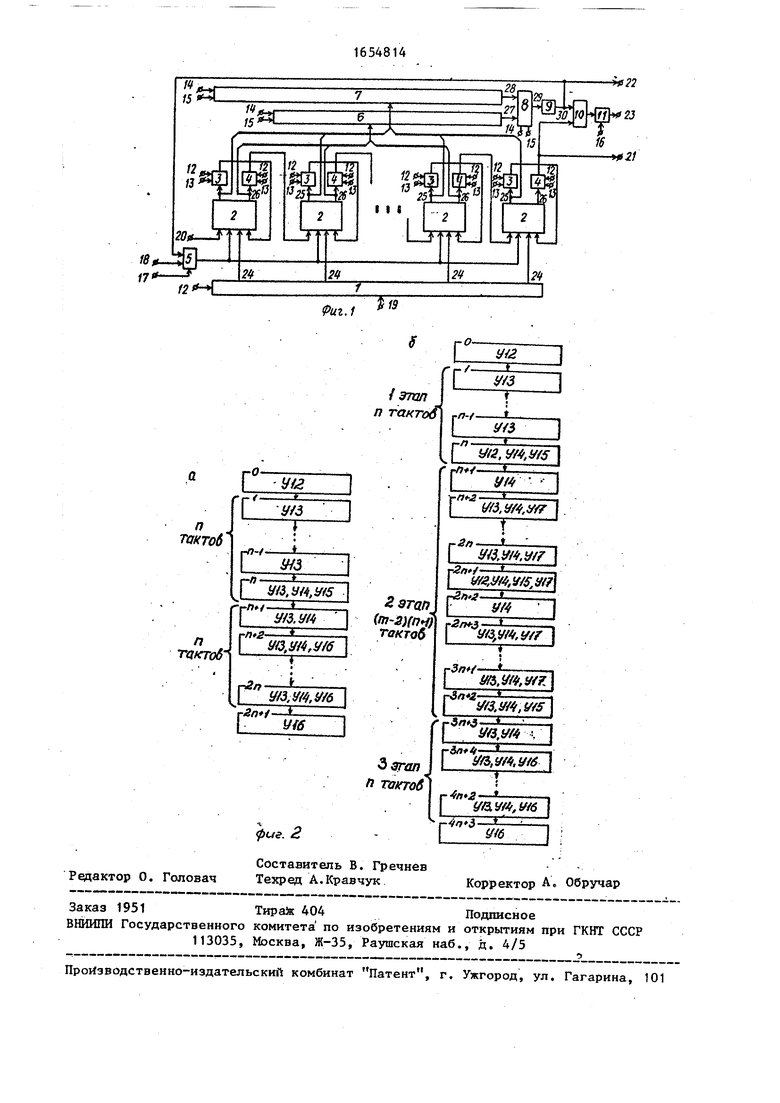

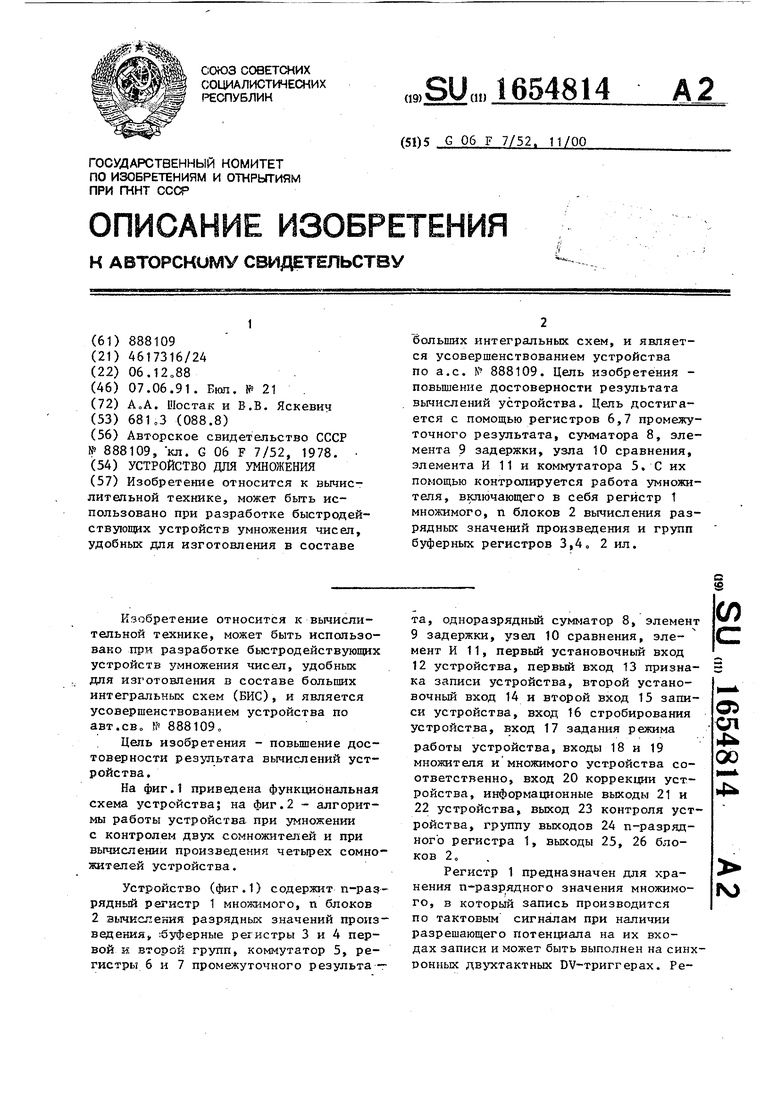

На фиг.1 приведена функциональная схема устройства; на фиг.2 - алгоритмы работы устройства при умножении с контролем двух сомножителей и при вычислении произведения четырех сомножителей устройства.

Устройство (фиг.1) содержит п-раз- рядный регистр 1 множимого, п блоков 2 вычисления разрядных значений произведения, буферные регистры 3 и 4 первой и второй групп, коммутатор 5, регистры 6 и 7 промежуточного результа та, одноразрядный сумматор 8, элемент 9 задержки, узел 10 сравнения, элемент И 11, первый установочный вход 12 устройства, первый вход 13 признака записи устройства, второй установочный вход 14 и второй вход 15 записи устройства, вход 16 стробирования устройства, вход 17 задания режима

работы устройства, входы 18 и 19 множителя и множимого устройства соответственно, вход 20 коррекции устройства, информационные выходы 21 и 22 устройства, выход 23 контроля устройства, группу выходов 24 п-разряд- ног о регистра 1, выходы 25, 26 блоков 2 о

Регистр 1 предназначен для хранения n-разрядного значения множимого, в который запись производится по тактовым сигналам при наличии разрешающего потенциала на их входах записи и может быть выполнен на синхронных двухтактных DV-триггерах. Ре(Л

05 О1

-U

00

1Ч

гистры 3 и 4 предназначены для хранения «соответственно старшего и младшего разрядов разрядных произведений, формируемых блоками 2. Регистры 6 и 7 предназначены для хранения п старших разрядов произведения сомножите- лей в двухрядном коде и представляют собой сдвиговые регистры, в которых под управлением потенциала на входах управления сдвигом осуществляется либо прием информации с информа - ционных входов, либо перезапись ее из старших в младшие разряды. Регистры 6 и 7 могут быть реализованы на синхронных двухтактных DV-тригге- рах, запись в которые осуществляется при наличии разрешающего потенциала на их входах записи, лричем разрядность регистра 6 равна (n-1), a разрядность-регистра 7 равна п. На фиг.1 условно не показаны цепи синхронизации всех регистров устройства, однако используется общая цепь синхронизации всех регистров устройства, образующая общую цепь синхронизации устройства.

Блоки 2 предназначены для вычисления значений разрядных произвед е- ний по формуле

F X«Y + A +

где Х9 Y - соответствующие разряды

сомножителей;

А, В - разрядные слагаемые, пос- тупающие на входы первого и вторых слагаемых блока 2.

Блоки 2 могут быть реализованы ,

самыми различными методами и средствами в зависимости от требований к быстродействию, регулярности структуры и т.д., в частности, возможно выполнение в виде ПЗУ (постоянного запоминающего устройства) или в виде комбинационных схем, синтез, которых может быть произведен любым из известных методов по таблице

истинности функционирования блока.

Одноразрядный сумматор 8 с запоминанием переноса предназначен для преобразования двухрядного кода произведения сомножителей в однорядный код. Этим самым вычисляются п старших разрядов произведения из инфор- мации, хранимой в регистрах 6 и 7. Одноразрядный сумматор 8 может быть реализован на основе комбинационно

Q 5 0 5

0

5

5

0

0

го сумматора и синхронного DV-тригге- ра для запоминания переноса, имеющего входы установки в нулевое состояние и записи. Запись в этот триггер производится при наличии разрешающего потенциала на V-входе. Синхро- вход триггера запоминания переноса соединен с общей цепью синхронизации устройства.

Элемент 9 задержки предназначен для формирования необходимой задержки значений разрядов произведения, требуемой при вычислении произведения нескольких сомножителей, а также при выполнении контроля формируемого результата. Элемент 9 задержки может быть реализован на основе одноразрядного регистра, построенного на синхронных двухтактных DV-тригге- рах, запись в которые осуществляется при наличии разрешающего потен-, циала на их V-входах (входе записи элемента 9), а синхровходы (не показаны) соединены с общей цепью синхронизации устройства.

Устройство работает следующим образом.

Рассмотрим работу устройства для следующих случаев:

умножение двух сомножителей с контролем (основной режим работы устройства);те

вычисление функции ,П А - произведение нескольких сомножителей с контролем.

Для пояснения работы устройства на фиг.2 представлены граф-схемы алгоритма функционирования устройства для основного режима умножения двух n-разрядных сомножителей с контролем (а) и при вычислении функfn

ции .П А-с контролем (где А: - п-раз- рядньш1 сомножители) для случая m 4(6).

На фиг.2 приняты следующие обозначения: Y12-Y17 - сигналы на входах 12-17 устройства соответственно.

Предполагается, что при наличии сигналов Y15 и Y14 осуществляется запись с выходов 25 и- 26 блоков 2 в регистры 7 и 6 соответственно, а при отсутствии Y15 и наличии Y14 производится сдвиг информации в регистрах 6 и 7. Также предполагается, что при наличии потенциала на Y17,,B коммутаторе 5 осуществляется передача с выхода элемента 9 задержки, а при

51

его отсутствии - передача с входа 18 множителя устройства

Устройство в основном режиме (фиг„2а) работает следующим образом.

В исходном состояли (вершина 0, фиг.2а) регистры 3 и 4 обнулены, в регистре 1 хранится без знака п-раз- рядное значение множимого, коммута- тор 5 настроен на передачу инфсрма- ции с входа 18 множителя устройства.

В каждом из (п-1) первых тактов работы устройства на его вход 18 поступает по одному разряду значение множителя, начиная с младшего раз ряда. При этом в i-м блоке 2 производится умножение разряда множителя, поступающего на его вход множителя с выхода коммутатора 5, на i-й разряд множимого, поступающего на его вход множимого с выхода 24-го разряда регистра 1 множимого, и прибавление к младшему разряду получившегося при этом двухразрядного произведения через входы первого и второго слага- емых 1-го.блока 2 соответственно старшего разряда произведения 1-го бло ка 2, сформированного в предыдущем такте и хранимого в i-м регистре 3, и младшего разряда произведения (i+1)- го блока 2, сформированного в предыдущем такте и хранимого в (i-H)-M регистре 4.5 Сформированные i-м блоком 2 старший и младший разряды произведения с его выходов 25 и 26 записываются сигналом Y13 в i-e регистр 3 и 4 соответственно.

В n-м такте работы устройства в блоках 2 производится аналогичное умножение множимого на n-й разряд

множителя, однако по окончании этого такта одновременно с записью информации с выходов 25 и 26 блоков 2 (которая представляет собой значение старших п разрядов произведения двух сомножителей з двухрядном коде) в регистры 3 и 4 производится их запись соответственно в регистры 7 и б по сигналам Y14 и Y15 а также осуществляется обнуление триггера запо минания переноса одноразрядного сумматора 8 (вершина п, фиг.2). При этом в течение первых п тактов из устройства через его информационный выход 21 выводится по одному разря- ду в каждом такте п младших разрядов произведения„

В течение последующих п тактов на вход 18 множителя устройства под14-6

eiCH нулевая информация, при этом в кзддом такте на первый вход узла 10 сравнения поступает по одному разряду,начиная с младших, старшие п разрядов произведения, формируемые одноразрядным сумматором 8 из информации, хранимой в регистрах 6 и 7, а на второй вход узла 10 сравнения поступают одноименные разряды произведения с выхода регистра 4, формиру- блоками 2 из информации, хранимой в регистрах 3 и 4 Подавая сигнал Y16, разрешают прохождение информации об ошибке с выхода узла 10 сравнения на выход 23 контроля устройства .

Вывод из устройства значения старших п разрядов произведения проиэво дится в течение последних п тактов через его первый информационный выход 21 либо через его второй информационный выход 22-по одному разряду в каждом такте. Причем при выводе результата через второй выход 22 устройства появляется возможность сразу после окончания первых п тактов работы устройства начать вычисление произведения новой пары сомножителей. В этом случае по окончании n-го такта подается сигнал на установочный вход 12 устройства, по которому производится обнуление регистров 3 и 4, а также запись нового значения множимого в регистр 1. Этим устройство подготавливается к вычислению произведения новой пары сомножителей, значение множителя которой подается па вход 18 устройства по одному разряду в каждом из последующих п тактов, в течение которых устройство работает аналогично первому умножению. Значение младших п разрядов нового произведения выводится из устройства через его первый информационный выход 21 по одному разряду в кахщом такте, одновременно с выводом через второй информационный выход 22 устройства старших разрядов предыдущего произведения В этом случае контроль за функционированием устройства невозможен.

До сих пор предполагалось, что на вход 20 коррекции устройства во всех тактах его работы подается нулевая информация. В тех же случаях, ког ра требуется получить округленное произведение, необходимо в первом такте работы устройства на его вход 20 подать корректирующую информацию

(для округления 2п-разрядного произведения n-разряднык сомножителей, представленных в двоично-кодированной шестнадцатеричной системе счисления, необходимо в первом такте работы J подать на вход 20 двоичный код 1000). Для округления произведений-пар сомножителей при их последовательном вычислении необходимо подавать корректив рующую информацию на вход 20 устройства одновременно с подачей на вход 18 множителя устройства первого разряда каждого множителя. Это позволяет осуществить округление результа- та без дополнительных временных затрат. Кроме того, вход 20 устройства может быть использован для введения результирующей коррекции до знакам множимого и множителя в случае умножен ния чисел в дополнительном коде.

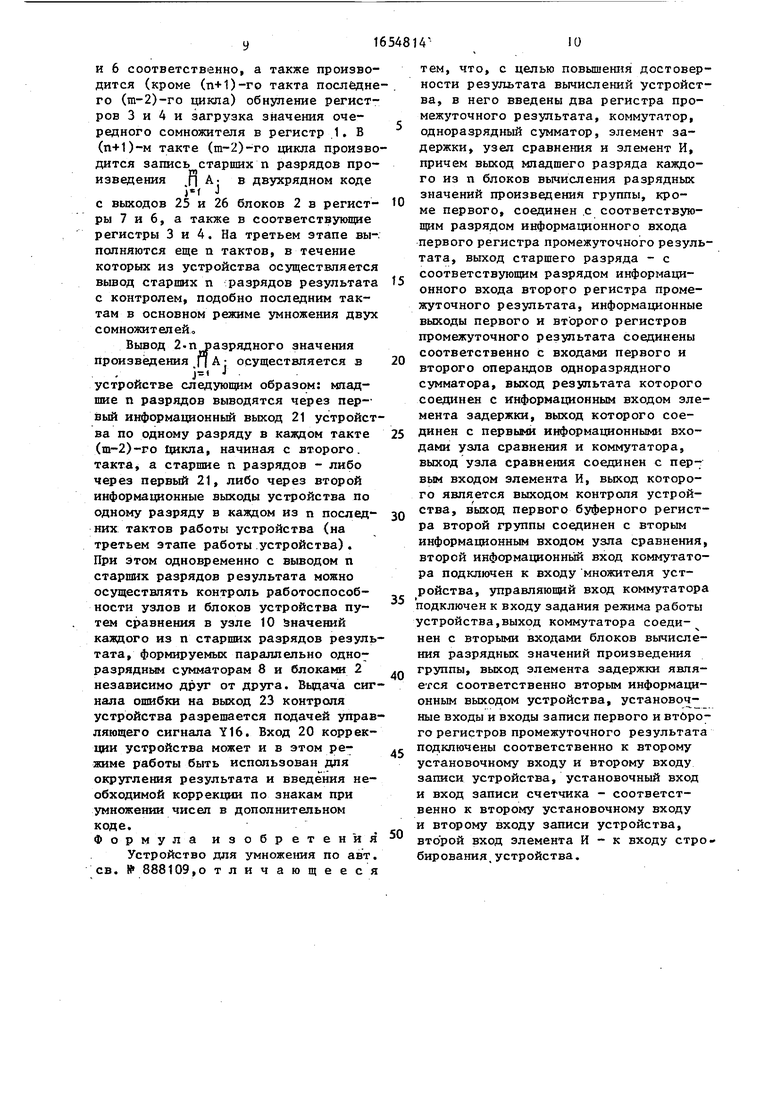

При вычислении функции .ПА- в

)i J

устройстве дополнительно используется коммутатор 5 для подачи на входы мно- жителя блоков 2 разрядов промежуточного произведения, вычисляемого сумматором 8 из информации, полученной в предыдущем цикле и хранимой в регистрах б и 7. Общее время работы устройства можно условно разделить на три этапа: на первом этапе производится умножение двух первых сомножителей, на втором это произведение перемножается с остальными сомножителями, а иа третьем осуществляет- ся вывод полученного результата с контролем. Первый этап включает п тактов, второй этап состоит из () циклов, каждый из которых включает (п+1) такт, а третий этап состоит из п тактов. Таким образом, общее время

вычисления функции П составляет

}(

(т-2) (п+1) + 2-п тактов.

Рассмотрим работу устройства, ис- пользуя для пояснения фиг.26. В исходном состоянии регистры 3 и 4 обнулены регистре 1 хранится без знака n-разрядное значение первого сомножителя. Коммутатор 5 настроен на пере- дачу информации с входа 18 множителя устройства (отсутствует сигнал Y17).

В каждом из п первых тактов работы устройства (первый этап) иа его вход 18 множителя поступает по одно- му разряду второй сомножитель и осуществляются те же операции, что и в основном режиме умножения двух сомножителей, т.е. производится вычисление

произведения двух первых сомножителей и запись его старших п разрядов в виде двухразрядного кода в регистры б и 7. Однако в наличии от основного режима, в n-м такте подается сигнал Y12, под действием которого устанавливаются в нулевое состояние регистры 3 и k и записывается очередной (третий) сомножитель в регистр 1.

На втором этапе работы устройства выполняются (т-2) подобных циклов.

Перед началом каждого из (т-2) циклов регистры 3 и 4 обнулены, в регистре 1 хранится без знака значение очередного сомножителя, в регистрах б и 7 хранится в двухрядном коде значение п старших разрядов произведения предыдущего цикла, триггер запоминания переноса сумматора 8 обнулен.

Далее в каждом из (т-2) циклоа в устройстве параллельно реализуются две функции: вычисление по одному разряду в каждом такте старших п разрядов произведения предыдущего цикла с помощью одноразрядного сумматора 8 из информации, хранимой в регистрах б и 7, и вычисление нового произведения с помощью блоков 2, используя в качестве множимого значение очередного сомножителя, хранимого в регистре t, а в качестве множителя - старшие п разрядов произведения пре-, дыдущего цикла, поступающие с выхода 30 элемента 9 задержки через коммутатор 5 настроенный сигналом Y17) на входы множителя блоков 2„ Таким образом, начиная с второго такта каждого из (т-2) циклов., в блоках 2 производятся операции, аналогичные первым п тактам работы устройства, причем на входы множителя блоков 2 поступает по одному разряду, начиная с младших значение произведения предыдущего цикла, вычисляемое одноразрядным сумматором 8 из информации, хранимой в регистрах б и 7 (в первом такте каждого из (т-2) циклов младший разряд этого произведения записывается в элемент 9 задержки), а на входы множимого блоков 2 поступает значение очередного сомножителя с выходов 24 регистра 1 множимого.

В (п+1)м такте каждого из (т-2) циклрв значение старших п разрядов получившегося нового произведения в двухрядном коде записываемся с выходов 25 и 26 блоков 2 в регистры 7

и 6 соответственно, а также производится (кроме (п+1)-го такта последнего (т-2)-го цикла) обнуление регистров 3 и 4 и загрузка значения очередного сомножителя в регистр 1. В (п+1)-м такте (т-2)-го цикла производится запись старших п разрядов произведения п А- в двухрядном коде

i«r J

с выходов 25 и 26 блоков 2 в регистры 7 и 6, а также в соответствующие регистры 3 и 4. На третьем этапе выполняются еще п тактов, в течение которых из устройства осуществляется вывод старших п разрядов результата с контролем, подобно последним тактам в основном режиме умножения двух сомножителейо

Вывод 2-п разрядного значения произведения А осуществляется в

J

устройстве следующим образом: младшие п разрядов выводятся через первый информационный выход 21 устройства по одному разряду в каждом такте (т-2)-го цикла, начиная с второго, такта, а старшие п разрядов - либо через первый 21, либо через второй информационные выходы устройства по одному разряду в каждом из п последних тактов работы устройства (на третьем этапе работы устройства). При этом одновременно с выводом п старших разрядов результата можно осуществлять контроль работоспособности узлов и блоков устройства путем сравнения в узле 10 значений каждого из п старших разрядов результата, формируемых параллельно одно разрядным сумматорам 8 и блоками 2 независимо друг от друга. Выдача сигнала ошибки на выход 23 контроля устройства разрешается подачей управляющего сигнала Y16. Вход 20 коррекции устройства может и в этом режиме работы быть использован для округления результата и введения необходимой коррекции по знакам при умножении чисел в дополнительном

коде.

Формула изобретения

Устройство для умножения по авт.

св. № 888109,о тличающееся

0

0

тем, что, с целью повышения достоверности результата вычислений устройства, в него введены два регистра промежуточного результата, коммутатор, одноразрядный сумматор, элемент задержки, узел сравнения и элемент И, причем выход младшего разряда каждого из п блоков вычисления разрядных значений произведения группы, кроме первого, соединен с соответствующим разрядом информационного входа первого регистра промежуточного результата, выход старшего разряда - с

,. соответствующим разрядом информационного входа второго регистра промежуточного результата, информационные выходы первого и второго регистров промежуточного результата соединены соответственно с входами первого и второго операндов одноразрядного сумматора, выход результата которого соединен с информационным входом элемента задержки, выход которого сое5 динен с первыми информационными входами узла сравнения и коммутатора, выход узла сравнения соединен с первым входом элемента И, выход которого является выходом контроля устройства, выход первого буферного регистра второй группы соединен с вторым информационным входом узла сравнения, второй информационный вход коммутатора подключен к входу множителя устройства, управляющий вход коммутатора подключен к входу задания режима работы устройства,выход коммутатора соединен с вторыми входами блоков вычисления разрядных значений произведения

группы, выход элемента задержки является соответственно вторым информационным выходом устройства, установочные входы и входы записи первого и втбро- го регистров промежуточного результата подключены соответственно к второму

0

5

5

0

установочному входу и второму входу записи устройства, установочный вход и вход записи счетчика - соответственно к второму установочному входу и второму входу записи устройства, второй вход элемента И - к входу стро. бирования,устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1988 |

|

SU1569824A1 |

Изобретение относится к вычислительной технике, может быть использовано при разработке быстродействующих устройств умножения чисел, удобных для изготовления в составе больших интегральных схем, и является усовершенствованием устройства по а.с. У 888109. Цель изобретения - повышение достоверности результата вычислений устройства. Цель достигается с помощью регистров 6,7 промежуточного результата, сумматора 8, элемента 9 задержки, узла 10 сравнения, элемента И 11 и коммутатора 5. С их помощью контролируется работа умножителя, включающего в себя регистр 1 множимого, п блоков 2 вычисления разрядных значений произведения и групп буферных регистров 3,4„ 2 ил.

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1988-12-06—Подача