Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке арифметических устройств ЭВМ. Целью изобретения является повышение быстродействия устройства.. Устройство содержит регистры 1, 2 множимого и множителя, блок 5 вычисления разрядных значений произведения, буферный регистр 3, регистр 4 частичного произведения и коммутатор 6. 3 ил., 1 табл.

О

сл

00

Ј

VJ

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЭВМ.

Целью изобретения является повышение быстродействия устройства.

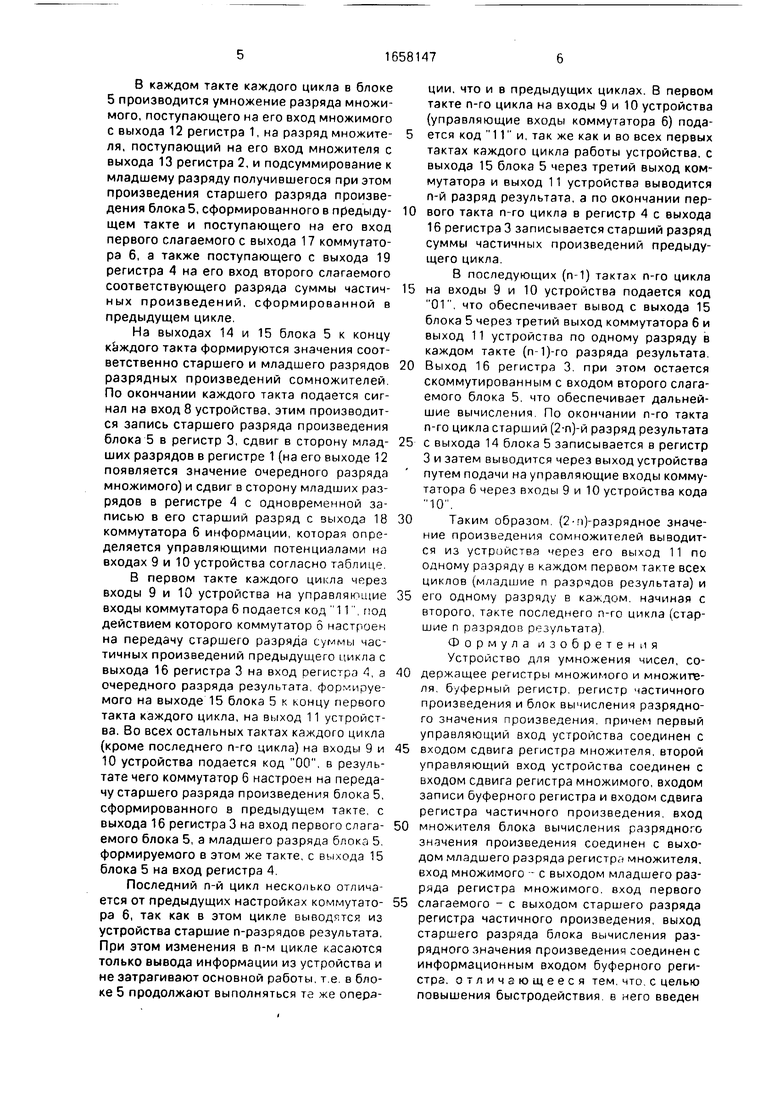

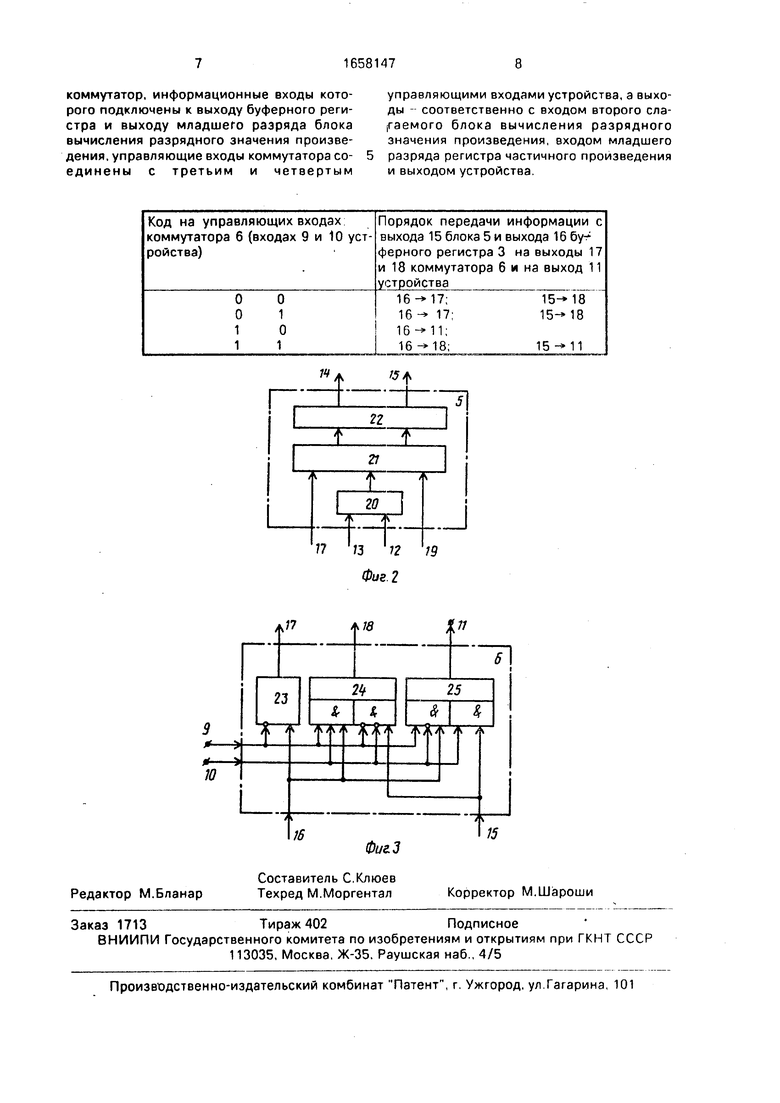

На фиг. 1 представлена структурная схема устройства для умножения чисел; на фиг. 2 - структурная схема блока вычисления разрядного значения произведения; на фиг. 3 - функциональная схема коммутатора.

Устройство для умножения чисел (фиг. 1) содержит регистр 1 множимого, регистр 2 множителя, буферный регистр 3, регистр 4 частичного произведения, блок 5 вычисления разрядного значения произведения, коммутатор 6, управляющие входы 7-10, выход 11. Вход множимого блока 5 вычисления разрядного значения произведения соединен с выходом 12 младшего разряда регистра 1, вход множителя - с выходом 13 младшего разряда регистра 2, выход 14 старшего разряда блока 5 соединен с информационным входом регистра 3, выход 15 младшего разряда блока 5 и выход 16 регистра 3 соединены с информационными входами коммутатора 6, первый 17 и второй 18 выходы которого соединены соответственно с входом второго слагаемого блока бис входом младшего разряда регистра 4, а третий выход коммутатора 5 подключен к выходу 11 устройства, выход 19 старшего разряда регистра 4 соединен с входом первого слагаемого блока 5, первый управляющий вход 7 соединен с входом сдвига регистра 2, второй управляющий вход 8 устройства соединен с входом разрешения записи регистра 3 и входами сдвига регистров 1 и 4, а третий 9 и четвертый 10 управляющие входы - с первым и вторым управляющими входами коммутатора 6 соответственно.

Регистр 1 множимого предназначен для хранения значения n-разрядного множимого. Он представляет собой сдвиговый регистр с кольцевым переносом разрядностью п. Регистр 2 множителя предназначен для хранения n-разрядного множителя и представляет собой сдвиговый регистр разрядностью п.

Буферный регистр 3 предназначен для хранения значения старшего разряда произведения, формируемого на выходе 14 блока 5.

Регистр 4 предназначен для хранения разрядов суммы частичных произведений, используемых как промежуточная информация при работе устройства. Он представляет собой сдвиговый регистр разрядностью (п-1).

Блок 5 предназначен для вычисления значения разрядного произведения сомножителей с учетом поступающих на его входы первого и второго слагаемых. Этот блок комбинационного типа и может быть реализован любыми известными способами, обеспечивающими выполнение функции:

B+C+D, где А, В, С, D - одноразрядные числа.

0Блок 5 (фиг. 2) содержит узел 20 умножения, узел 21 суммирования и сумматор 22, На выходе узла 20 умножения формируется произведение сомножителей в многоряд5 ном (в частном случае - в двухрядном) коде, узел 21 суммирования преобразует многорядный код в код, удобный для обработки параллельным сумматором 21 с входным переносом, на выходах которого формируются

0 в однорядном коде старший и младший разряды разрядного произведения сомножите- лей. Например, при использовании операндов, представленных в двоично-кодированной шестнадцатиричной системе

5 счисления, узел 20 формирует четырехрядный код произведения сомножителей, узел 21 в два этапа преобразует шестирядный код в код, который с помощью двухвходово- го сумматора 22 с входным переносом пре0 образуется в однорядный результат.

Коммутатор 6 осуществляет передачу старшего и младшего разрядов произведений, формируемых блоком 5, на вход второго слагаемого блока 5, вход младшего

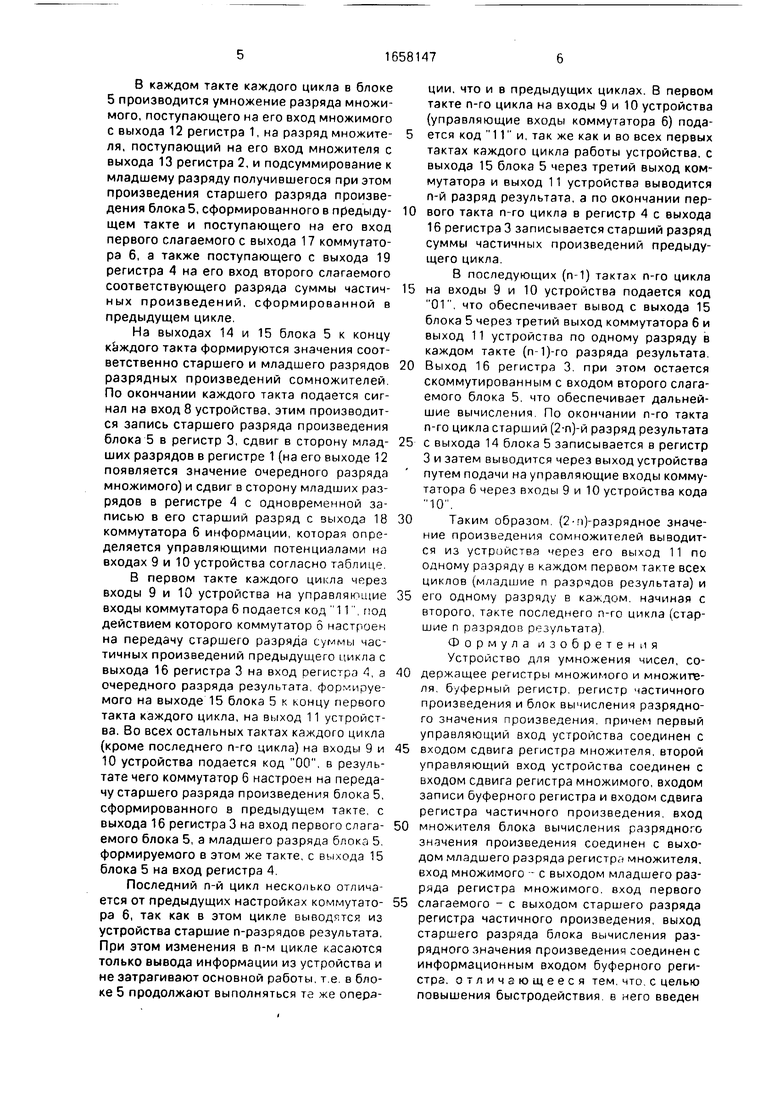

5 разряда регистра 4 и на выход 11 устройства в соответствии с сигналами на управляющих входах, определяемых алгоритмом функционирования устройства. В таблице поясняется функционирование коммутато0 ра.6.

В таблице запись вида означает, что информация с выхода 16 регистра 3 передается на выход 17 коммутатора 6. Коммутатор 6 содержит элементы И 23,

5 И-ИЛИ 24 и И-ИЛИ 25 с соответствующими связями (фиг. 3).

Устройство работает следующим образом.

В исходном состоянии регистры 3 и 4

0 обнулены, в регистрах 1 и 2 хранятся без знака n-разрядные значения соответственно множимого и множителя.

Умножение в устройстве выполняется за п циклов, каждый из которых реализуется за п

5 тактов, т.е. конечный результат формируется за п2 тактов. В течение одного цикла в устройстве формируется частичное произведение множимого на один разряд множителя, а также осуществляется подсуммирование этого частичного произведения к ранее накопленной сумме частичных произведений.

В каждом такте каждого цикла в блоке 5 производится умножение разряда множимого, поступающего на его вход множимого с выхода 12 регистра 1, на разряд множителя, поступающий на его вход множителя с выхода 13 регистра 2, и подсуммирование к младшему разряду получившегося при этом произведения старшего разряда произведения блока 5, сформированного в предыдущем такте и поступающего на его вход первого слагаемого с выхода 17 коммутатора 6, а также поступающего с выхода 19 регистра 4 на его вход второго слагаемого соответствующего разряда суммы частичных произведений, сформированной в предыдущем цикле.

На выходах 14 и 15 блока 5 к концу каждого такта формируются значения соответственно старшего и младшего разрядов разрядных произведений сомножителей По окончании каждого такта подается сигнал на вход 8 устройства, этим производится запись старшего разряда произведения блока 5 в регистр 3, сдвиг в сторону младших разрядов в регистре 1 (на его выходе 12 появляется значение очередного разряда множимого) и сдвиг в сторону младших разрядов в регистре 4 с одновременной записью в его старший разряд с выхода 18 коммутатора 6 информации, которая определяется управляющими потенциалами на входах 9 и 10 устройства согласно таблице

В первом такте каждого цикла через входы 9 и 10 устройства на управляющие входы коммутатора 6 подается код 11 под действием которого коммутатор 6 настроен на передачу старшего разряда суммы частичных произведений предыдущего цикла с выхода 16 регистра 3 на вход регистра 4, а очередного разряда результата формируемого на выходе 15 блока 5 к концу первого такта каждого цикла, на выход 11 устройства. Во всех остальных тактах каждого цикла (кроме последнего n-го цикла) на входы 9 и 10 устройства подается код 00, в результате чего коммутатор 6 настроен на передачу старшего разряда произведения блока 5, сформированного в предыдущем такте с выхода 16 регистра 3 на вход первого слагаемого блока 5, а младшего разряда блока 5 формируемого в этом же такте, с выхода 15 блока 5 на вход регистра 4

Последний n-й цикл несколько отличается от предыдущих настройках коммутатора 6, так как в этом цикле выводятся из устройства старшие n-разрядов результата. При этом изменения в n-м цикле касаются только вывода информации из устройства и не затрагивают основной работы, т е в блоке 5 продолжают выполняться те же операции, что и в предыдущих циклах. В первом такте n-го цикла на входы 9 и 10 устройства (управляющие входы коммутатора 6) пода- ется код 11 и, так же как и во всех первых тактах каждого цикла работы устройства, с выхода 15 блока 5 через третий выход коммутатора и выход 11 устройства выводится n-й разряд результата, а по окончании пер0 вого такта n-го цикла в регистр 4 с выхода 16 регистра 3 записывается старший разряд суммы частичных произведений предыдущего цикла

В последующих (п-1) тактах n-го цикла

5 на входы 9 и 10 устройства подается код 01, что обеспечивает вывод с выхода 15 блока 5 через третий выход коммутатора 6 и выход 11 устройства по одному разряду в каждом такте (п-1)-го разряда результата

0 Выход 16 регистра 3 при этом остается скоммутированным с входом второго слагаемого блока 5 что обеспечивает дальнейшие вычисления По окончании n-го такта n-го цикла старший (2-п)-й разряд результата

5 с выхода 14 блока 5 записывается в регистр 3 и затем выводится через выход устройства путем подачи на управляющие входы коммутатора 6 через входы 9 и 10 устройства кода 10

0Таким образом (2-п)-разрядное значение произведения сомножителей выводится из устройства через его выход 11 по одному разряду в каждом первом такте всех циклов (младшие п разрядов результата) и

5 его одному разряду в каждом начиная с второго, такте последнего n-го цикла (старшие п разрядов результата)

Формула изобретения Устройство для умножения чисел, со0 держащее регистры множимого и множителя буферный регистр регистр частичного произведения и блок вычисления разрядного значения произведения причем первый управляющий вход устройства соединен с

5 входом сдвига регистра множителя, второй управляющий вход устройства соединен с входом сдвига регистра множимого, входом записи буферного регистра и входом сдвига регистра частичного произведения вход

0 множителя блока вычисления разрядного значения произведения соединен с выходом младшего разряда регистре 1 множителя, вход множимого - с выходом младшего разряда регистра множимого вход первого

5 слагаемого - с выходом старшего разряда регистра частичного произведения, выход старшего разряда блока вычисления разрядного значения произведения соединен с информационным входом буферного регистра, отличающееся тем что с целью повышения быстродействия е него введен

коммутатор, информационные входы которого подключены к выходу буферного регистра и выходу младшего разряда блока вычисления разрядного значения произведения, управляющие входы коммутатора соединены с третьим и четвертым

Ю

управляющими входами устройства, а выходы -- соответственно с входом второго сла- Гаемого блока вычисления разрядного значения произведения, входом младшего разряда регистра частичного произведения и выходом устройства.

ФигЗ

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1988-12-21—Подача