«1

Изобретение относится к автоматике и зычкслительной технике и может быть использовано для бесконтактного измерения параметров движения объектов относительно поверхностей со слу- чайным распределением яркостей.

Цель изобретения - повышение точности устройства .

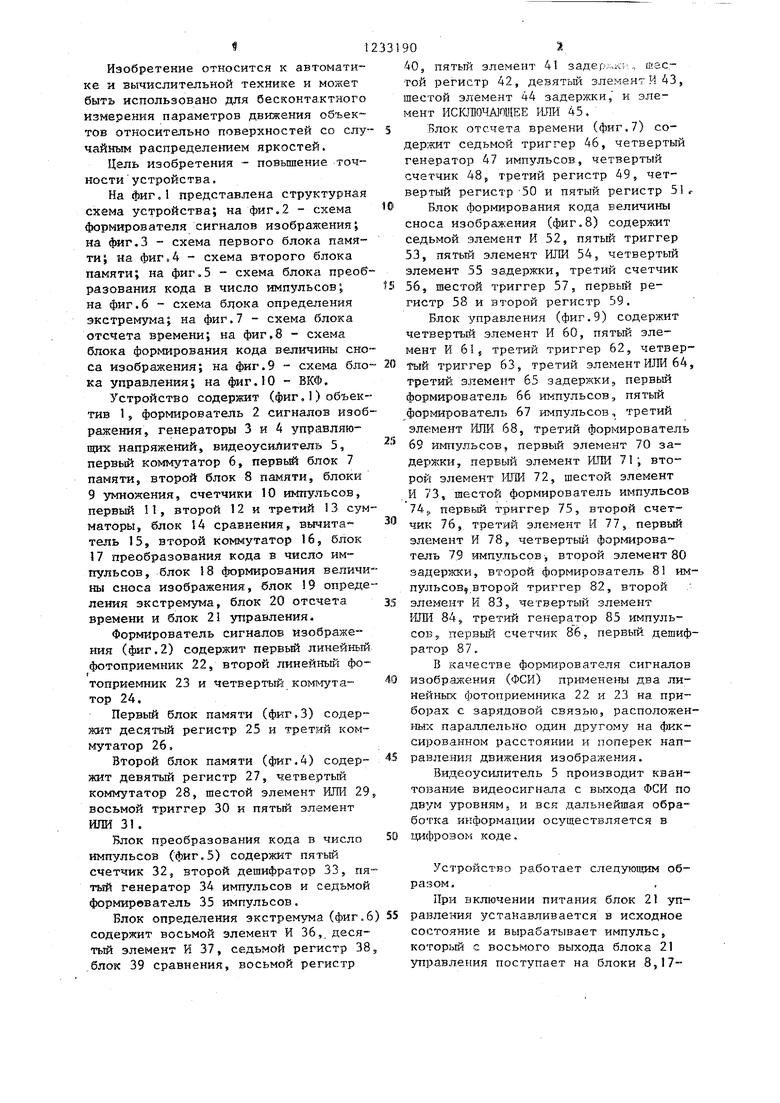

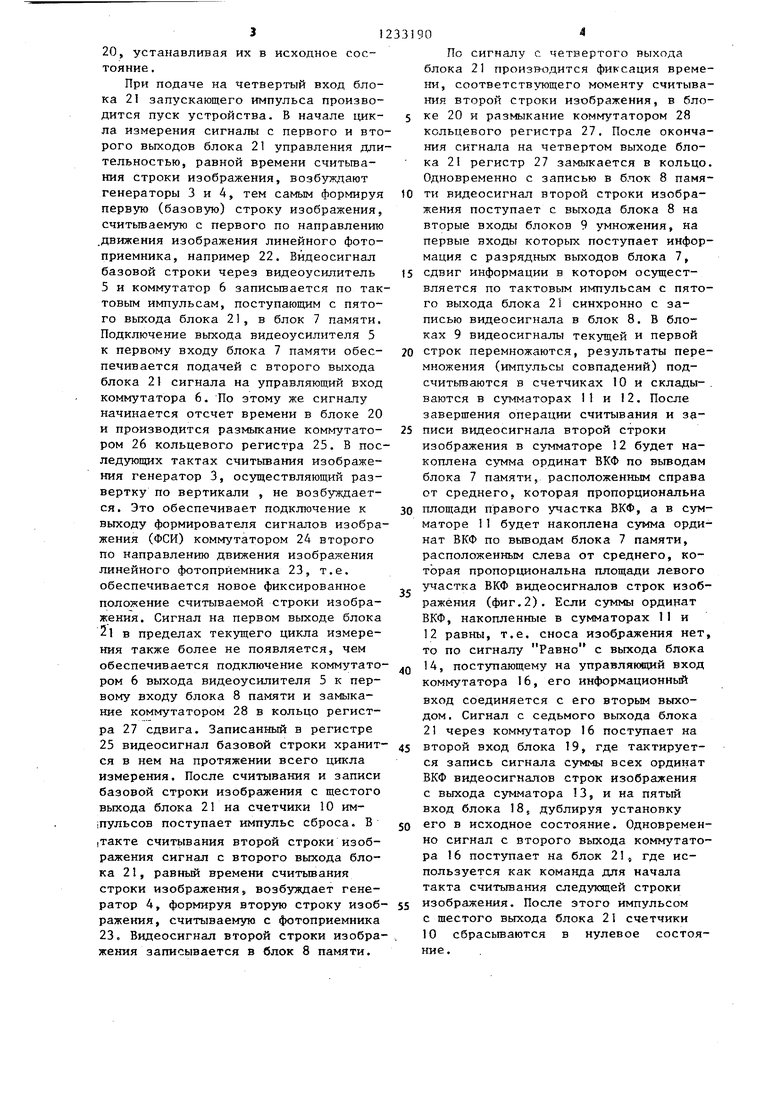

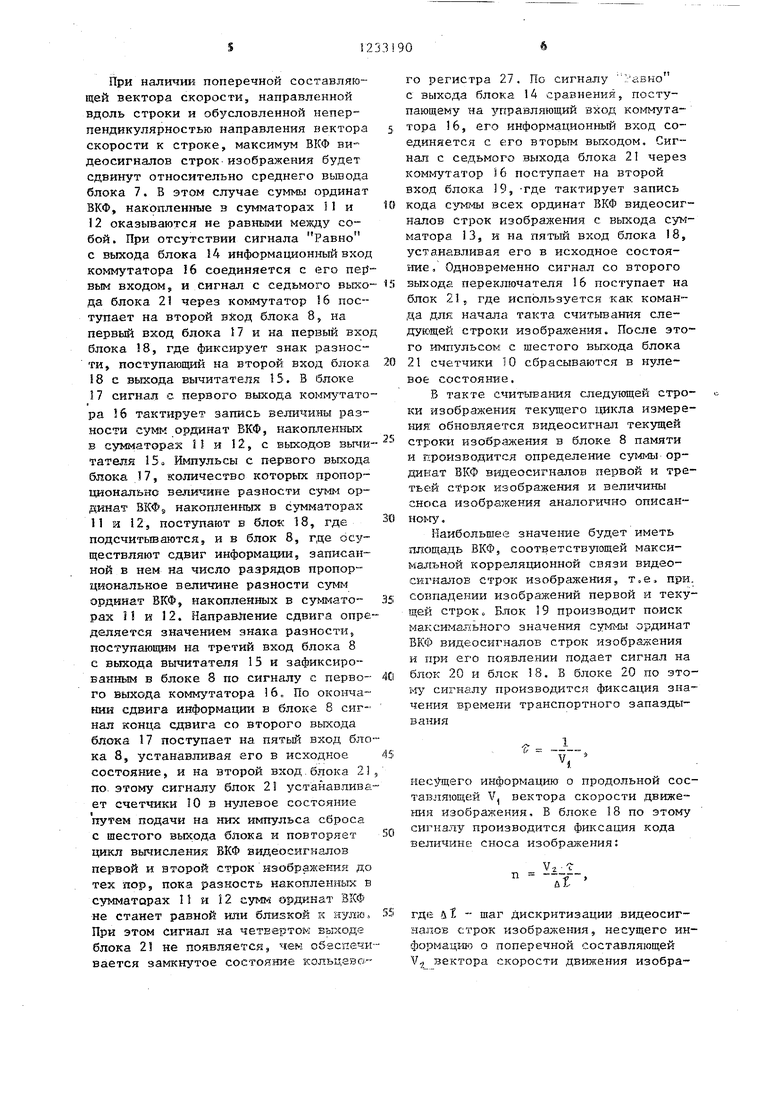

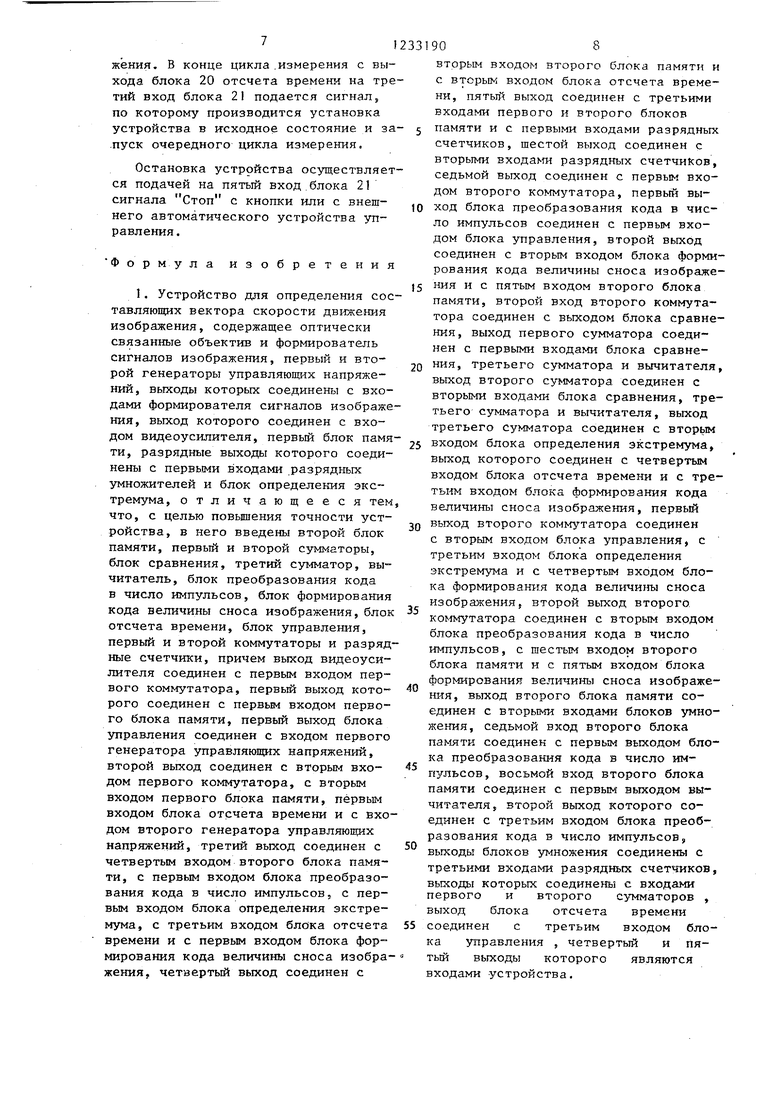

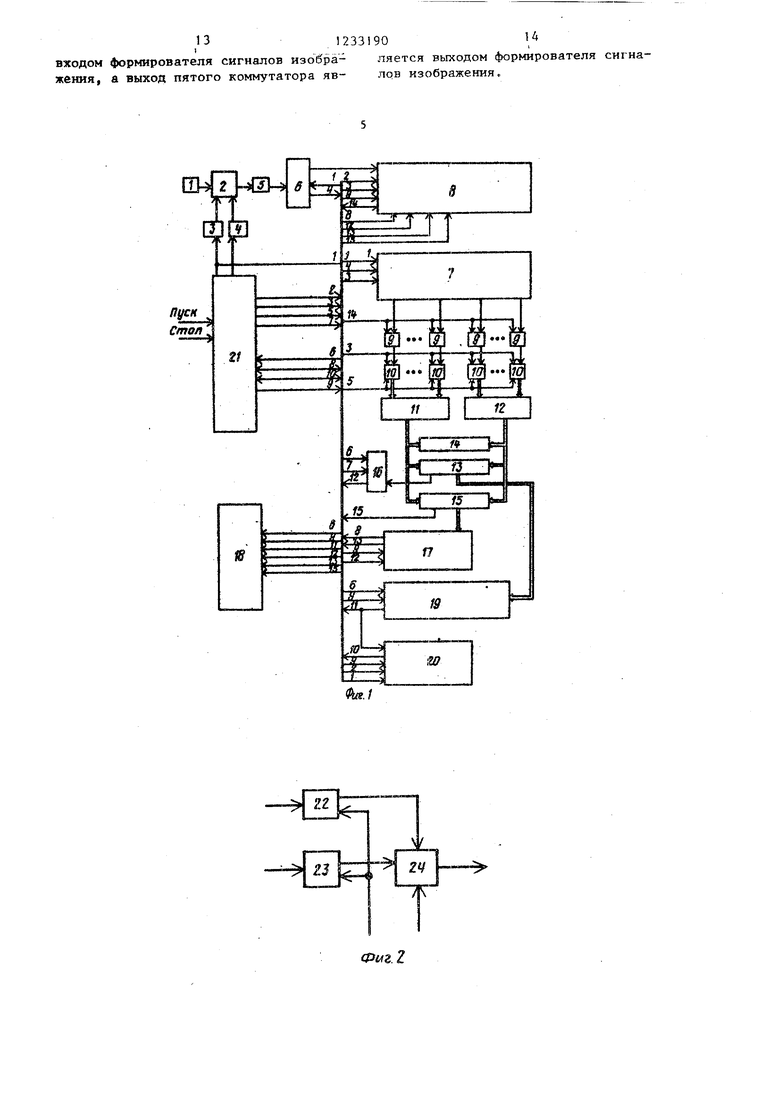

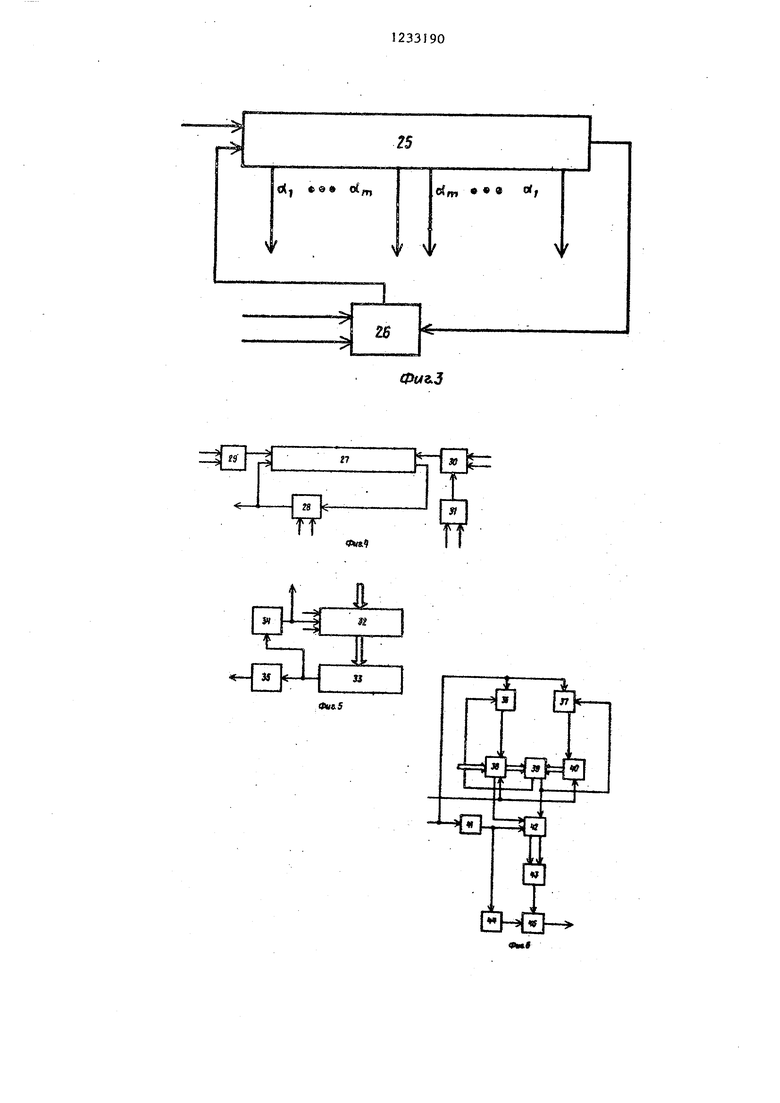

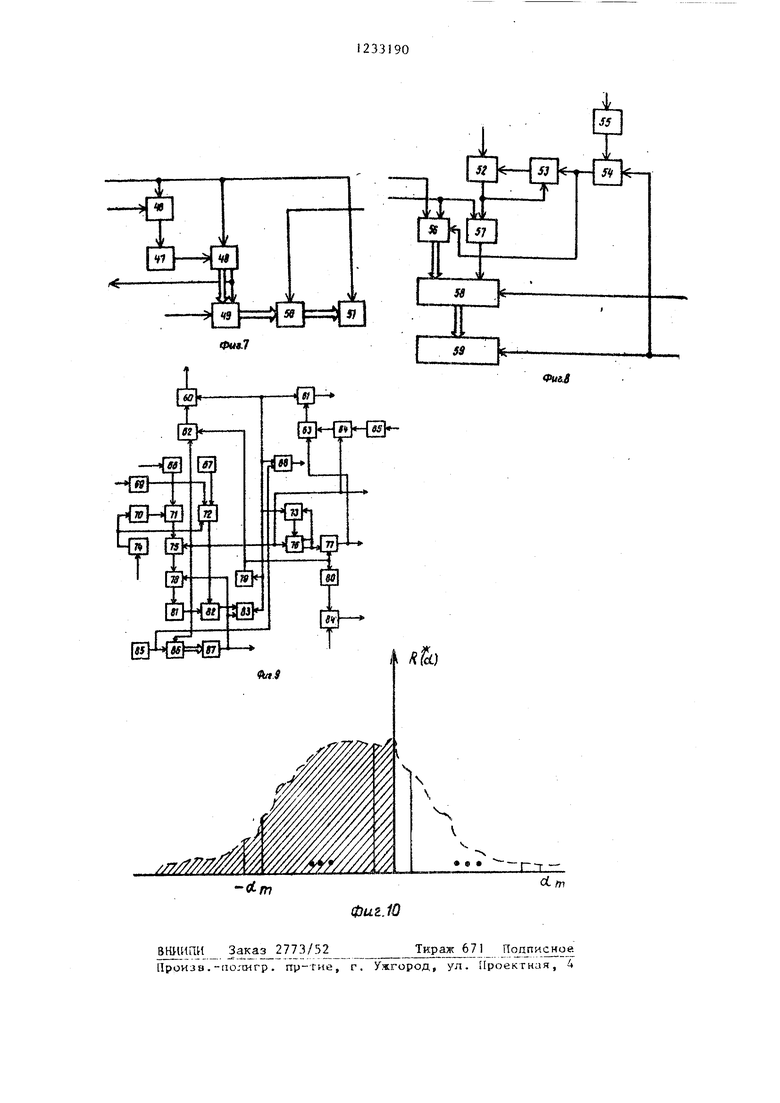

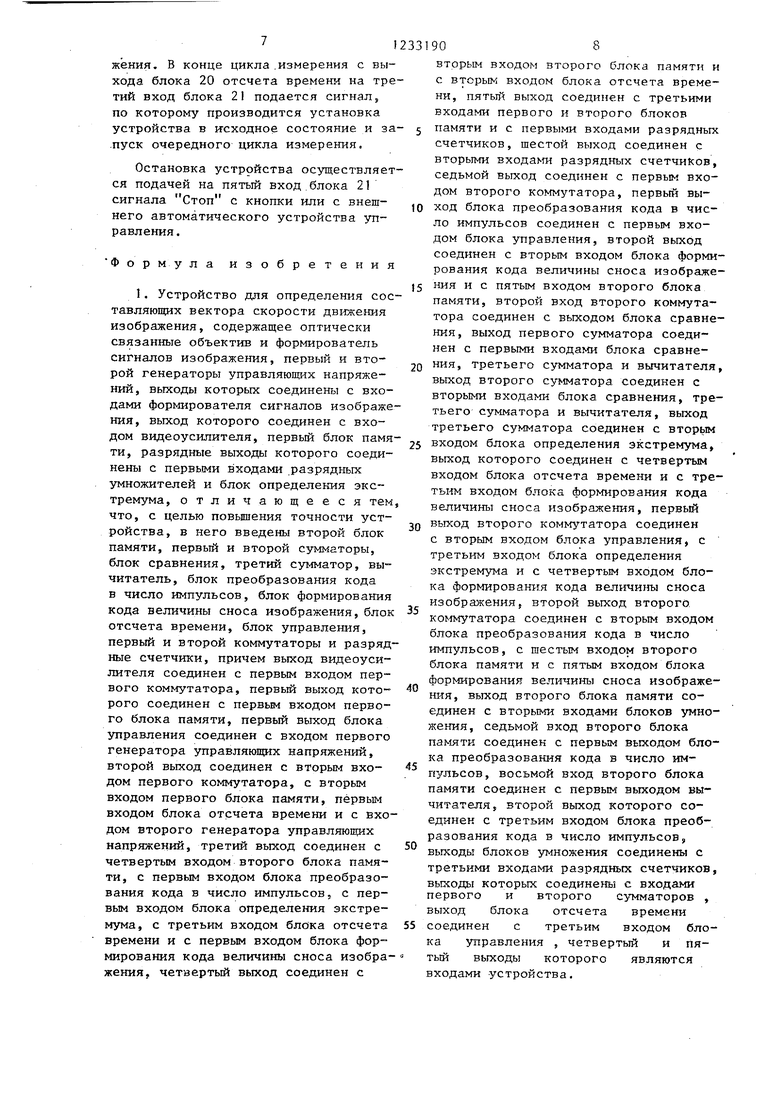

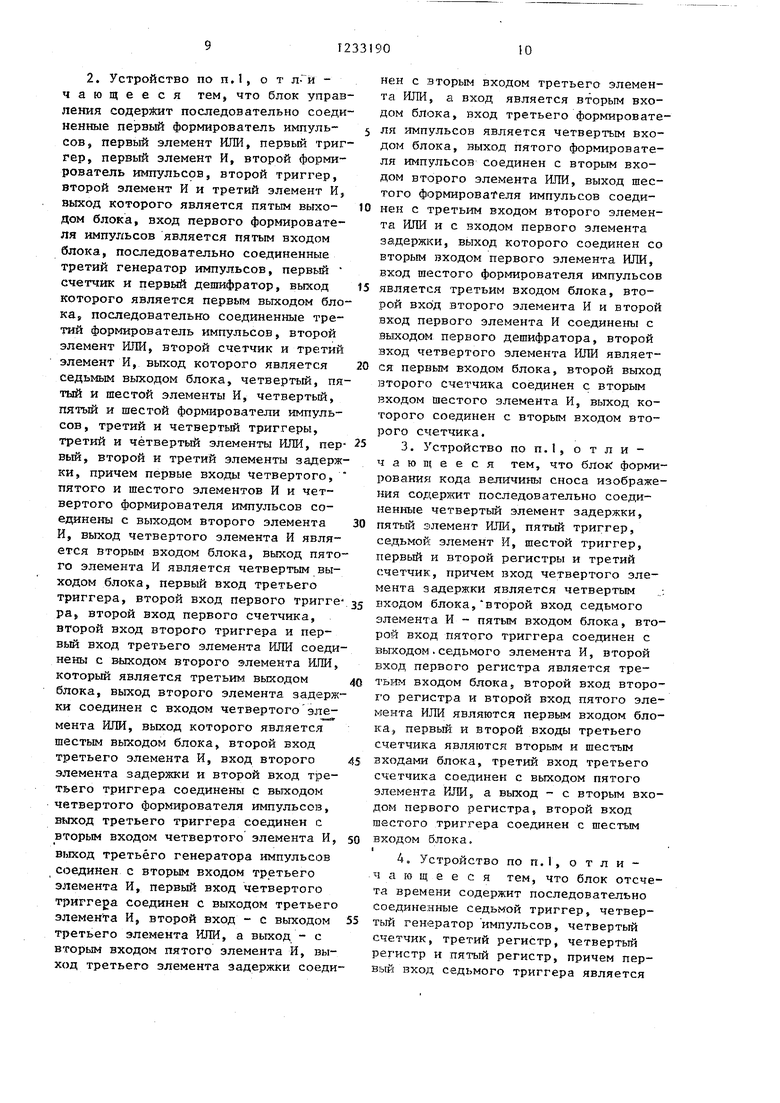

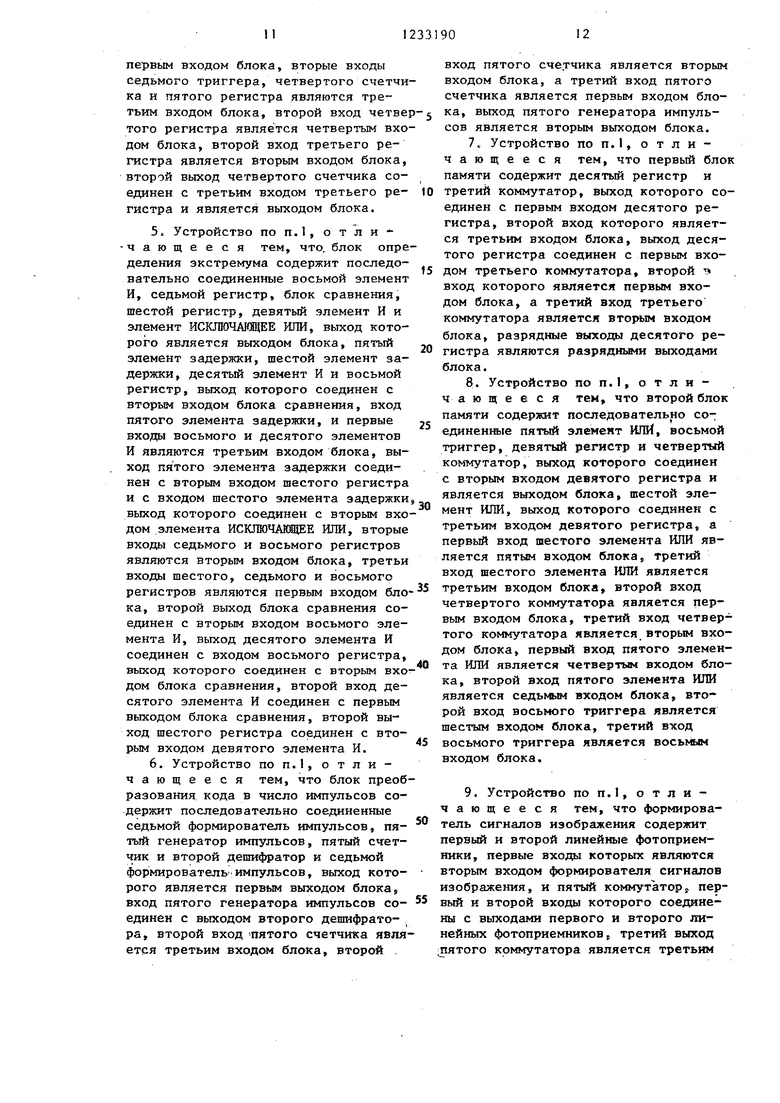

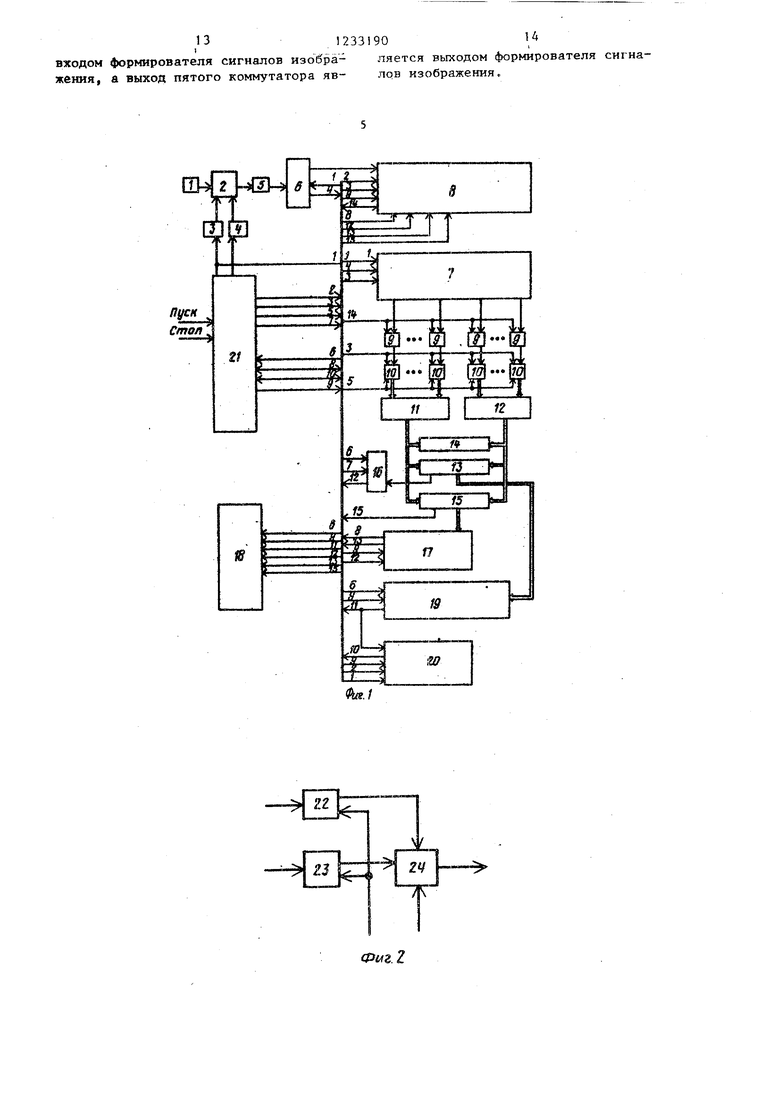

На фиг.1 представлена структурная схема устройства; на фиг.2 - схема формирователя сигналов изображения , на фиг.З - схема первого блока памяти; на фиг.4 - схема второго блока памяти; на фиг«5 - схема блока преобразования кода в число импульсов; на фиг.6 схема блока определения экстремума; на фиг.7 - схема блока отсчета времени; на фиг.8 - схема блока формирования кода величины сноса изображения; на фиг.9 - схема бло ка управления; на фиг.10 - ВКФ.

Устройство содержит (фиг, 1) объектив 15 формирователь 2 сигналов изображения, генераторы 3 и 4 управляющих напряжений, видеоусилитель 5, первый коммутатор 6, первый блок 7 памяти, второй блок 8 памяти, блоки 9 умножения, счетчики 10 импульсов, первый 11, второй 12 и третий 13 сумматоры, блок 54 сравнения, вьгчита- тель 15, второй коммутатор 16, блок 7 преобразования кода в число импульсов, блок 18 формирования величины сноса изображения, блок 19 определения экстремума, блок 20 отсчета времени и блок 21 управления.

Формирователь сигналов изображения (фиг.2) содержит первый лииейный фотоприемник 22, второй линейный фотоприемник 23 и четвертый коммута- тор 24,

Первый блок памяти (фиг.З) содержит десятый регистр 25 и третий коммутатор 26,

Второй блок памяти (фиг.4) содер- жит девятый регистр 27, четвертый коммутатор 28, шестой элемент ИЛИ 29, восьмой триггер 30 и пятый элемент ШШ 31 .

Блок преобразования кода в число импульсов (фиг.З) содержит пятый счетчик 32J второй дешифратор 33, пятый генератор 34 импульсов и седьмой формиреватель 35 импульсов.

Блок определения экстремума (фиг.б содержит восьмой элемент И 36, десятый элемент И 37, седьмой регистр 38, блок 39 сравнения, восьмой регистр

:90X

40, пятый элемент 41 задерка-а ,, шестой регистр 42, девятый элемент И 43, шестой элемент 44 задержки, и элемент ИСЮЖ1ЧА Щ1 ЕЕ ИЛИ 45.

Блок отсчета времени (фиг.7) со- дер;|кит седьмой триггер 46, четвертый генератор 47 импульсов, четвертый счетчик 48, третий регистр 49, четвертый регистр 50 и пятый регистр 51 «

Блок формирования кода величины сноса изображения (фиг.8) содержит седьмой элемент И 52, пятый триггер 53, пятьш элемент ИЛИ 54, четвертый элемент 55 задержки, третий счетчик 56, шестой триггер 57, первый регистр 58 и второй регистр 59.

Блок управления (фиг.9) содержит четвертый элемент И 60, пятый элемент И 61, третий триггер 62, четвертый триггер 63, третий элемент ИЛИ 64, третий элемент 65 задержки, первый формирователь 66 импульсов, пятый формирователь 67 импульсов, третий ИЛИ 68, третий формирователь 69 импульсов, первый элемент 70 задержки, первый элемент ШШ 71; второй элемент ШШ 72, шестой элемент И 73, шестой формирователь импульсов 74,, первый триггер 75, второй счетчик 76, третий элемент И 77, первый элемент И 78, четвертый формирователь 79 импульсов-, второй элемент 80 задержки, второй формирователь 81 импульсов, второй триггер 82, второй элемент И 83, четвертый элемент ИЛИ 84, третий генератор 85 импуль- СО13,, первый счетчик 86, первый дешифратор 87,

В качестве формирователя сигналов изобр,ажения (ФСИ) при1-1екень два линейных фотоприемника 22 и 23 на приборах с зарядовой связью, расположен- ны: параллельно один другому на фиксированном расстоянии и поперек направления движения изображения.

Видеоусилитель 5 производит квантование видеосигнала с выхода ФСИ по двум уровням, и вся дальнейшая обработка информации осуществляется в цифровом коде.

Устройство работает следующим образом.

При включении питания блок 21 уп- раш1е5-шя устанавливается в исходное состояние и вырабатывает импульс, который с восьмого выхода блока 21 управления поступает на блоки 8,173I

20, устанавливая их в исходное состояние,

При подаче на четвертый вход блока 21 запускающего импульса производится пуск устройства. В начале цик- ла измерения сигналы с первого и второго выходов блока 21 управления длительностью, равной времени считьгоа- ния строки изображения, возбуждают генераторы 3 и 4, тем самым формируя первую (базовую) строку изображения, считьгоаемую с первого по направлению .движения изображения линейного фотоприемника, например 22. Видеосигнал базовой строки через видеоусилитель 5 и коммутатор 6 записьшается по тактовым импульсам, поступающим с пятого выхода блока 21, в блок 7 памяти. Подключение выхода видеоусилителя 5 к первому входу блока 7 памяти обес- печивается подачей с второго выхода блока 21 сигнала на управляющий вход коммутатора 6. По этому же сигналу начинается отсчет времени в блоке 20 и производится размыкание коммутато- ром 26 кольцевого регистра 25. В последующих тактах считьтания изображения генератор 3, осуществляющий развертку по вертикали , не возбуждается. Это обеспечивает подключение к выходу формирователя сигналов изображения (ФСИ) коммутатором 24 второго по направлению движения изображения линейного фотопрйемника 23, т.е. обеспечивается новое фиксированное положение считываемой строки изображения. Сигнал на первом выходе блока 2l в пределах текущего цикла измерения также более не появляется, чем обеспечивается подключение коммутато ром 6 выхода видеоусилителя 5 к первому входу блока 8 памяти и замыкание коммутатором 28 в кольцо регистра 27 сдвига. Записанный в регистре 25 видеосигнал базовой строки хранит- ся в нем на протяжении всего цикла измерения. После считывания и записи базовой строки изображения с щестого выхода блока 21 на счетчики 10 им- 1пульсов поступает импульс сброса. В ,такте считывания второй строки изображения сигнал с второго выхода блока 21, равный времени считьшания строки изображения, возбуждает генератор 4, формируя вторую строку изоб- ражения, считываемую с фотоприемника 23. Видеосигнал второй строки изобра- жения записывается в блок 8 памяти.

5 0 5 0 5 о 5 Q

5

90

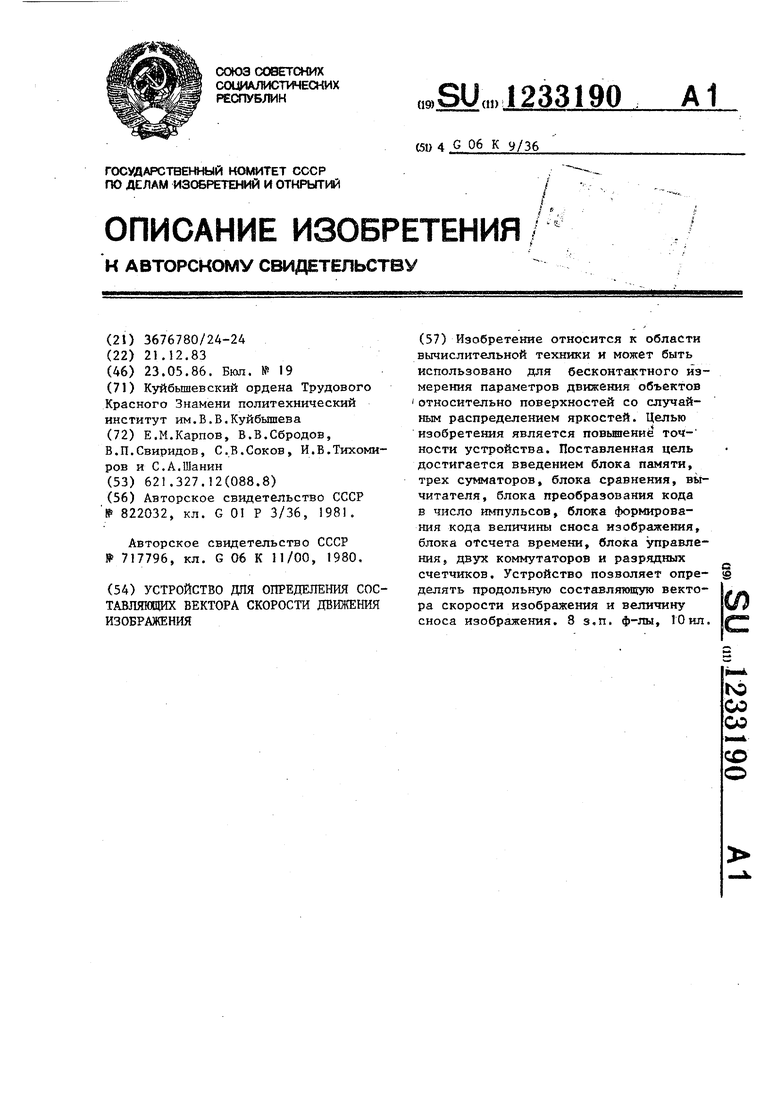

По сигналу с четвертого выхода блока 21 произн-одится фиксация времени, соответствующего моменту считывания второй строки изображения, в блоке 20 и размыкание коммутатором 28 кольцевого регистра 27. После окончания сигнала на четвертом выходе блока 21 регистр 27 замыкается в кольцо. Одновременно с записью в блок 8 памяти видеосигнал второй строки изображения поступает с выхода блока 8 на вторые входы блоков 9 умножения, на первые входы которых поступает информация с разрядных выходов блока 7, сдвиг информации в котором осуществляется по тактовым импульсам с пятого выхода блока 2 i синхронно с записью видеосигнала в блок 8. В блоках 9 видеосигналы текущей и первой строк перемножаются, результаты перемножения (импульсы совпадений) под- считьшаются в счетчиках 10 и склады- . ваются в сумматорах П и 12. После завершения операции считывания и записи видеосигнала второй строки изображения в сумматоре 12 будет накоплена сумма ординат ВКФ по вьгеодам блока 7 памяти, расположенным справа от среднего, которая пропорциональна площади правого участка ВКФ, а в сумматоре 11 будет накоплена сумма ординат ВКФ по вьшодам блока 7 памяти, расположенным слева от среднего, которая пропорциональна площади левого участка ВКФ видеосигналов строк изображения (фиг.2). Если суммы ординат ВКФ, накопленные в сумматорах 11 и 12 равны, т.е. сноса изображения нет, то по сигналу Равно с выхода блока 14, поступающему на управляющий вход коммутатора 16, его информационный

вход соединяется с его вторым выходом , Сигнал с седьмого выхода блока 2 через коммутатор 16 поступает на второй вход блока 19, где тактируется запись сигнала суммы всех ординат ВКФ видеосигналов строк изображения с выхода сумматора 13, и на пятый вход блока 18, дублируя установку его в исходное состояние. Одновременно сигнал с второго выхода коммутатора 16 поступает на блок 21, где используется как команда для начала такта считывания следующей строки изображения. После этого импульсом с шестого выхода блока 21 счетчики 10 сбрасьшаются в нулевое состояние.

При наличии поперечной составляющей вектора скорости, направленной вдоль строки и обусловленной неперпендикулярностью направления вектора скорости к строке, максимум ВКФ видеосигналов строк-изображения будет сдвинут относительно среднего вьшода блока 7. В этом случае суммы ординат ВКФ, накопленные в сумматорах Пи 12 оказываются не равными между собой . При отсутствии сигнала Равно с выхода блока 14 информационный вход коммутатора 16 соединяется с его первым входомS и Сигнал с седьмого выхо- да блока 21 через коммутатор 16 поступает на второй вход блока 8, на первый вход блока 17 и на первый вход блока 8, где фиксирует знак разности, поступающий на второй вход блока }8 с выхода вычитателк 15. В блоке 17 сигнал с первого выхода коммутатора 16 тактирует запись величины разности сумм ординат ВКФ, накоп-пенных в еумматораэг It и 12, с выходов вьгчи- тателя 15 Импульсы с первого выхода блока 17, количество которых пропорционально величине разности с-умм ординат ВКФ5 накопленных в сумматорах 11 и 12, поступают в блок 18, где подсчитьшаются, и в блок 8, где осуществляют сдвиг информации, записанной в нем на число разрядов пропорциональное величине разности сумм ординат ВКФ, накоплейШ)1Х в сумкато- pax П и 12. Направление сдвига определяется значением знака разности, поступающим на третий вход блока 8 с выхода вычитателя 15 и зафиксированным в блоке 8 по сигналу с перво- го выхода коммутатора 6„ По окончании сдвига информации в блоке 8 сигнал конца сдвига со второго выхода блока 17 поступает на пятьй вход блока 8, устанавливая его в исходное состояние, и на второй вход.блока 21 по. этому сигналу блок 21 устанавливает счетчики 10 в нулевое состояние путем подачи на них импульса сброса с шестого выхода блока и повторяет цикл вычисления ВКФ видеосигналов первой и второй строк изображения до тех пор 5 пока разность накопленных s сумматорах П и 12 сумм ординат ВКФ не станет равной или близкой к нулгс, При этом сигнал на четЕе|зток вьзходе блока 2 не появляется, чем обесшгчи- вается замкнутое состоя яме кольцевого регистра 27. По сигнат1у :: авно с выхода блока 14 сравнения, поступающему на управляющий вход ко1-{мута- тора 16, его информационный вход соединяется с его вторым выходом. Сигнал с седьмого выхода блока 21 через коммутатор 16 поступает на второй вход блока 19, -где тактирует запись кода cyMiMbi всех ординат ВКФ видеосигналов строк изображения с выхода сумматора 13, и на пятьш вход блока 18, устанавливая его в исходное состояние/ Одновременно сигнал со второго выхода переключателя 16 поступает на блок 215 где используется как команда для начала такта считывания следующей строки изображения. После этого импульсом с шестого выхода блока 21 счетчики 10 сбрасываются в нулевое состояние.

В такте считьгеания следующей строки изображения тек тцего одкла измерения: обновляется видеосигнал текущей строки изображения в блоке 8 памяти и производится определение суммы ординат ВКФ видеосигналов первой и третьей строк изображения и величины сноса изображения аналогично описан- .

Наибольшее значение будет иметь площа; ь ВКФ, соответствующей макси- корреляционной связи видеосигналов строк изображения, т,е, при. еокпадении изображений первой и текущей строк. Блок 19 производит поиск максимального значения суммы ординат ВКФ видеосигналов строк изображения и при его появлении подает сигнал на блок 20 и блок 18. В блоке 20 по это- try сигналу производится фиксация значения времени транспортного запаздывания

несущего информацию о продольной сос- та1зляющей V, вектора скорости движения изображения. В блоке 18 по этому сигналу производится фиксация кода величине сноса изображения:

П --а

где йХ шаг Дискритизации видеосигналов строк изображения, несущего ин- формацш-э о поперечной составляющей ,д вектора скорости движения изобра7

жения. В конце цикла .измерения с выхода блока 20 отсчета времени на третий вход блока 21 подается сигналj по которому производится установка устройства в исходное состояние и за- .пуск очередного цикла измерения.

Остановка устройства осуществляется подачей на пятый вход блока 21 сигнала Стоп с кнопки или с внешнего автоматического устройства управления.

Фор м у ла изобретения

1. Устройство для определения составляющих вектора скорости движения изображения, содержащее оптически связанные объектив и формирователь сигналов изображения, первый и второй генераторы управляющих напряжений, выходы которых соединены с входами формирователя сигналов изображения, выход которого соединен с входом видеоусилителя, первый блок памяти, разрядные выходы которого соединены с первыми входами разрядных умножителей и блок определения экстремума, отличающееся тем что, с целью повышения точности устройства, в него введены второй блок памяти, первый и второй сумматоры, блок сравнения, третий сумматор, вы- чйтатель, блок преобразования кода в число импульсов, блок формирования кода величины сноса изображения, блок отсчета времени, блок управления, первый и второй коммутаторы и разрядные счетчики, причем выход видеоусилителя соединен с первым входом первого коммутатора, первый выход которого соединен с первым входом первого блока памяти, первый выход блока управления соединен с входом первого генератора управляющих напряжений, второй выход соединен с вторым входом первого коммутатора, с вторым входом первого блока памяти, первым входом блока отсчета времени и с входом второго генератора управляющих напряокений, третий выход соединен с четвертым входом второго блока памяти, с первым входом блока преобразования кода в число импульсов, с первым входом блока определения экстремума, с третьим входом блока отсчета времени и с первым входом блока формирования кода величины сноса изобра- жения, четвертый выход соединен с

- 5

15

20

25

30

35

, 55

4Q

45

50

908

вторым входом второго блока памяти и с вторьм входом блока отсчета времени, пятьш выход соединен с третьими входами первого и второго б.поков памяти и с первыми входами разрядных счетчиков, шестой выход соединен с вторыми входами разрядных счетчиков, седьмой выход соединен с первым входом второго коммутатора, первый выход блока преобразования кода в число импульсов соединен с первым входом блока управления, второй выход соединен с вторым входом блока формирования кода величины сноса изображения и с пятым входом второго блока памяти, второй вход второго коммутатора соединен с выходом блока сравнения, выход первого сумматора соединен с первыми входами блока сравнения, третьего сумматора и вычитателя, выход второго сумматора соединен с вторыми входами блока сравнения, третьего сумматора и вычитателя, выход третьего сумматора соединен с вторЬ1М входом блока определения экстремума, выход которого соединен с четвертым входом блока отсчета времени и с третьим входом блока формирования кода величины сноса изображения, первый выход второго коммутатора соединен с вторым входом блока управления, с треты-iM входом блока определения экстремума и с четвертым входом блока формирование кода величины сноса изображения, второй выход второго коммутатора соединен с вторым входом блока преобразования кода в число импульсов, с шестым входом второго блока памяти и с пятым входом блока формирования величины сноса изображения, выход второго блока памяти соединен с вторыми входами блоков умножения, седьмой вход второго блока памяти соединен с первым выходом блока преобразования кода в число импульсов, восьмой вход второго блока памяти соединен с первым выходом вычитателя, второй выход которого соединен с третьим входом блока преобразования кода в число импульсов, выходы блоков умножения соединены с третьими входами разрядных счетчиков, выходь которых соединены с входами первого и второго сумматоров , выход блока отсчета времени соединен с третьим входом блока управления , четвертый и Пятый выходы которого являются входами устройства.

2. Устройство по п.1, о т л-и - чающееся тем, что блок управления содерйсит последовательно соединенные первый формирователь импульсов, первый элемент ИЛИ, первый триггер, первый элемент И, второй формирователь импульсов, второй триггер, второй элемент И и третий элемент И, выход которого является пятым выходом блока, вход первого формирователя импульсов является пятым входом блока, последовательно соединенные третий генератор импульсов, первый счетчик и первый дешифратор, выход которого является первым выходом блока, последовательно соединенные третий формирователь импульсов, второй элемент ИЛИ, второй счетчик и третий элемент И, выход которого является седьмым выходом блока, четвертый, пятый и шестой элементы И, четвертый, пятый и шестой формирователи импульсов, третий и четвертьй триггеры, третий и четвертый элементы ИЛИ, первый, второй и третий элементы задержки, причем первые входы четвертого, пятого и шестого элементов И и четвертого формирователя импульсов соединены с выходом второго элемента И, выход четвертого элемента И является вторым входом блока, выход пятого элемента И является четвертым выходом блока, первый вход третьего триггера, второй вход первого тригге ра, второй вход первого счетчика, второй вход второго триггера и первый вход третьего элемента ИЛИ соединены с выходом второго элемента И,Г1И, который является третьим выходом блока, выход второго элемента задержки соединен с входом четвертого элемента ШШ, выход которого является шестым выходом блока, второй вход третьего элемента И, вход второго элемента задержки и второй вход третьего триггера соединены с выходом четвертого формирователя импульсов, выход третьего триггера соединен с вторым входом четвертого элемента И, вг51ход третьего генератора импульсов соединен с вторым входом тр етьего элемента И, первый вход четвертого триггера соединен с выходом третьего элемента И, второй вход - с выходом третьего элемента ИЛИ, а выход - с вторым входом пятого элемента И, выход третьего элемента задержки соединен с вторым входом третьего элемента ИЛИ, а вход является вторым входом блока, вход третьего формировате- 5 ля импульсов является четвертым входом блока, выход пятого формирователя импульсов соединен с вторым входом второго элемента ИЛИ, выход шестого формирователя импульсов соеди0 нен с третьим входом второго элемента ШШ и с входом первого элемента задержки, выход которого соединен со вторым входом первого элемента ИЛИ, вход Ш(2стого формирователя импульсов

5 является третьим входом блока, второй вход второго элемента И и второй вход первого элемента И соединены с выходом первого дешифратора, второй вход четвертого элемента ИЛИ являет0 ся первым входом блока, второй выход )зторого счетчика соединен с вторым входом шестого элемента И, выход которого соединен с вторым входом второго счетчика.

5 3. З стройство по п. 1, о т л и - чающееся тем, что блокг формирования кода величины сноса изображе- 1ШЯ содержит последовательно соединенные четвертый элемент задержки,

0 пятьш элемент ИЛИ, пятый триггер, седьмой элемент И, шестой триггер, первый и второй регистры и третий счетчик, причем вход четвертого элемента задержки является четвертым

5 входом блока, второй вход седьмого элемента И - пятым входом блока, второй вход пятого триггера соединен с выходом.седьмого элемента И, второй вход первого регистра является тре0 тьим входом блока, второй вход второго регистра и второй вход пятого элемента ИЛИ являются первым входом блока, первый: и второй входы третьего счетчика являются вторым и шестым

5 входами блока, третий вход третьего счетчика соединен с выходом пятого элемента ИЛИ, а выход - с вторым входом первого регистра, второй вход шестого триггера соединен с шестым

0 входом блока,

4. Устройство по п.1, о т л и - чающееся тем, что блок отсчета времени содержит последовательно соединенные седьмой триггер, четвер- 5 Tbrfi генератор импульсов, четвертый счетчик, третий регистр, четвертьй регистр и пятый регистр, причем первый вход седьмого триггера является

первым входом блока, вторые входы седьмого триггера, четвертого счетчика и пятого регистра являются третьим входом блока, второй вход четве того регистра является четвертым входом блока, второй вход третьего регистра является вторым входом блока, второй выход четвертого счетчика соединен с третьим входом третьего ре- гистра и является выходом блока,

5.Устройство по п. 1, о т л и -чающееся тем, что. блок определения экстремума содержит последовательно соединенные восьмой элемент И, седьмой регистр, блок сравнения, шестой регистр, девятый элемент И и элемент ИСКЛЮЧАКЩЕЕ ИЛИ, выход которого является выходом блока, пятый элемент задержки, шестой элемент задержки, десятый элемент И и восьмой регистр, выход которого соединен с вторым входом блока сравнения, вход пятого элемента задержки, и первые входы восьмого и десятого элементов

И являются третьим входом блока, выход пятого элемента задержки соединен с вторым входом шестого регистра и с входом шестого элемента задержки выход которого соединен с вторым входом элемента ИСКЛЮЧАКЩЕЕ ИЛИ, вторые входы седьмого и восьмого регистров являются вторым входом блока, третьи входы шестого, седьмого и восьмого регистров являются первым входом бло ка, второй выход блока сравнения соединен с вторым входом восьмого элемента И, выход десятого элемента И соединен с входом восьмого регистра, выход которого соединен с вторым входом блока сравнения, второй вход десятого элемента И соединен с первым выходом блока сравнения, второй выход шестого регистра соединен с вторым входом девятого элемента И.

6.Устройство по п.1, о т л и - чающееся тем, что блок преобразования кода в число импульсов содержит последовательно соединенные седьмой формирователь импульсов, пя- тый генератор импульсов, пятый чик и второй дешифратор и седьмой формирователь импульсов, выход кото- рого является первым выходом блока, вход пятого генератора импульсов со- единен с выходом второго дешифратора, второй вход ПЯТОГО счетчика является третьим входом блока, второй

S

5 0

n 5

0

U

вход пятого счетчика является вторым входом блока, а третий вход пятого счетчика является первым входом блока, выход пятого генератора импульсов является вторьп выходом блока.

7.Устройство по П.1, отличающееся тем, что первый блок памяти содержит десятый регистр и третий коммутатор, выход которого соединен с первым входом десятого регистра, второй вход которого является третьим входом блока, выход десятого регистра соединен с первым входом третьего коммутатора, второй вход которого является первым входом блока, а третий вход третьего коммутатора является вторым входом блока, разрядные выходы десятого регистра являются разрядньв и выходами блока.

8.Устройство по п.1, о т л и - чающееся тем, что второй блок памяти содержит последовательно со- единенш 1е пятый элемент ИЛИ, восьмой триггер, девятьй регистр и четвертый коммутатор, выход которого соединен

с вторым входом девятого регистра и является выходом блока, шестой элемент ИЖ, выход которого соединен с третьим входом девятого регистра, а первый вход шестого элемента ИЛИ является пятым входом блока, третий вход шестого элемента ИЛИ является третьим входом блока, второй вход четвертого коммутатора является первым входом блока, третий вход четвертого коммутатора является вторым входом блока, первый вход пятого элемента ИЛИ является четвертым входом блока, второй вход пятого элемента ИЛИ является седькьм входом блока, второй вход восьмого триггера является шестым входом блока, третий вход восьмого триггера является восьмым входом блока.

9.Устройство по П.1, отличающееся тем, что формирователь сигналов изображения содержит первый и второй линейные фотоприем- ники, первые входы которых являются вторым входом формирователя сигналов изображения, и пятый коммутаторj первый и второй входы которого соединены с выходами первого и второго линейных фотоприемников третий выход пятого коммутатора является третьим

входом формирователя сигналов изобра- ляется выходом формирователя сигна- жения, а выход пятого коммутатора яв- лов изображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Устройство для обнаружения движущихся объектов | 1989 |

|

SU1817256A2 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для распознавания элементов треков | 1983 |

|

SU1161969A1 |

Изобретение относится к области вычислительной техники и может быть использовано для бесконтактного измерения параметров движения объектов относительно поверхностей со случайным распределением яркостей. Целью изобретения является повьшение точ- ности устройства. Поставленная цель достигается введением блока памяти, трех сумматоров, блока сравнения, BIJ- читателя, блока преобразования кода в число ш шульсов, блока формирования кода величины сноса изображения, блока отсчета времени, блока управления, двух коммутаторов и разрядных счетчиков. Устройство позволяет определять продольную составлянмцую вектора скорости изображения и величину сноса изображения. 8 з,п. ф-лы, 10ил. с S N3 СО со со о

Z3

IU l.lllKnm

щ

. 2

r

o(, ® Ы

IT

75

m

d, e rt.

f

f

zs

Фиъ.3

(Ani9

TT

4Ъ«5

//7

.

Ч

ч

-X «

рт

-ctm

ВЩШПИ Заказ 2773/52

Произа.-ао:шгр. пр--гне, г. Ужгород, ул. Проектная, 4

ct

m

фи&.Ю

Ткралс 671 Подписное

| Датчик скорости изображения | 1979 |

|

SU822032A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для считывания и определения параметров движения констрастного изображения | 1976 |

|

SU717796A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-12-21—Подача