Изобретение относится к технике телевидения и может использоваться для обнаружения движущихся малоразмерных объектов на фоне подвижных и их идентификации.

Целью изобретения является обеспечение возможности обнаружения и идентификации движущихся малоразмерных объектов на подвижном фоне с объектами.

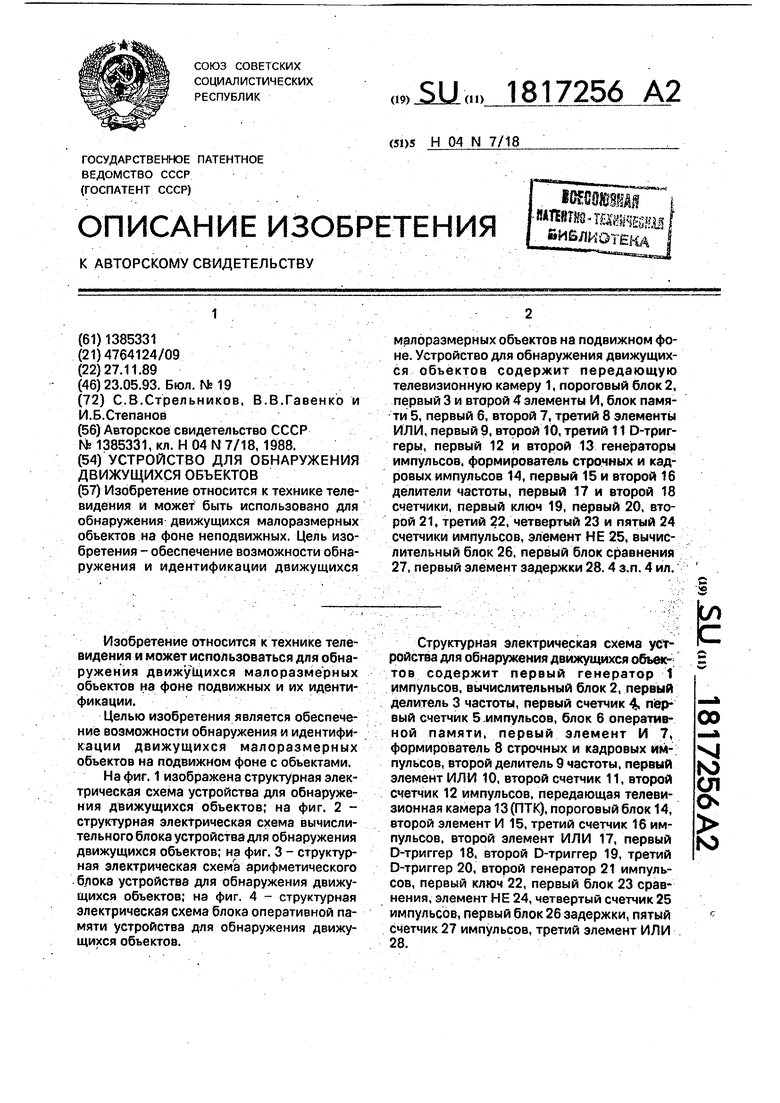

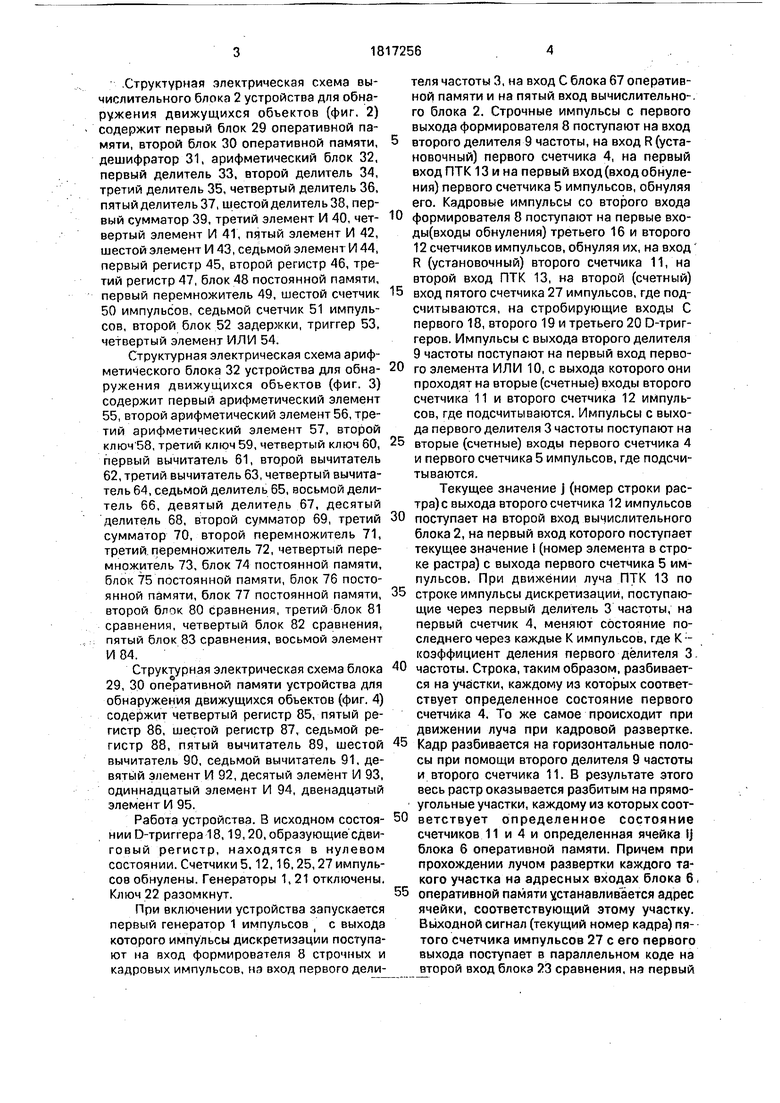

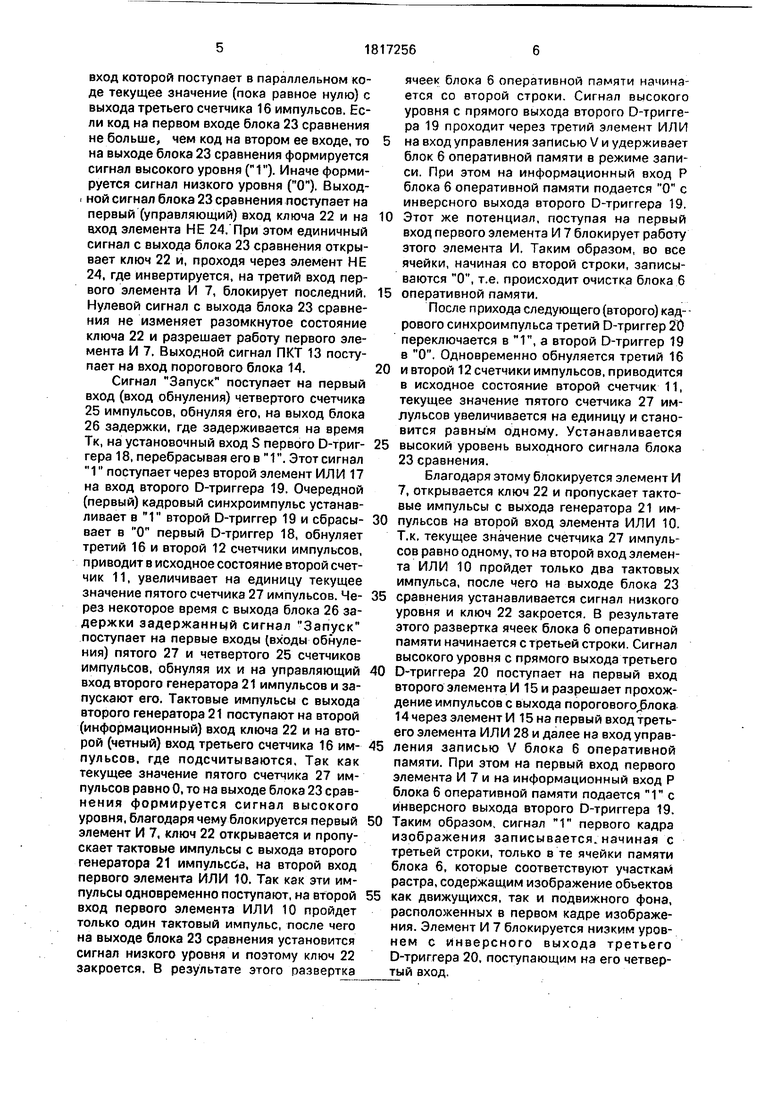

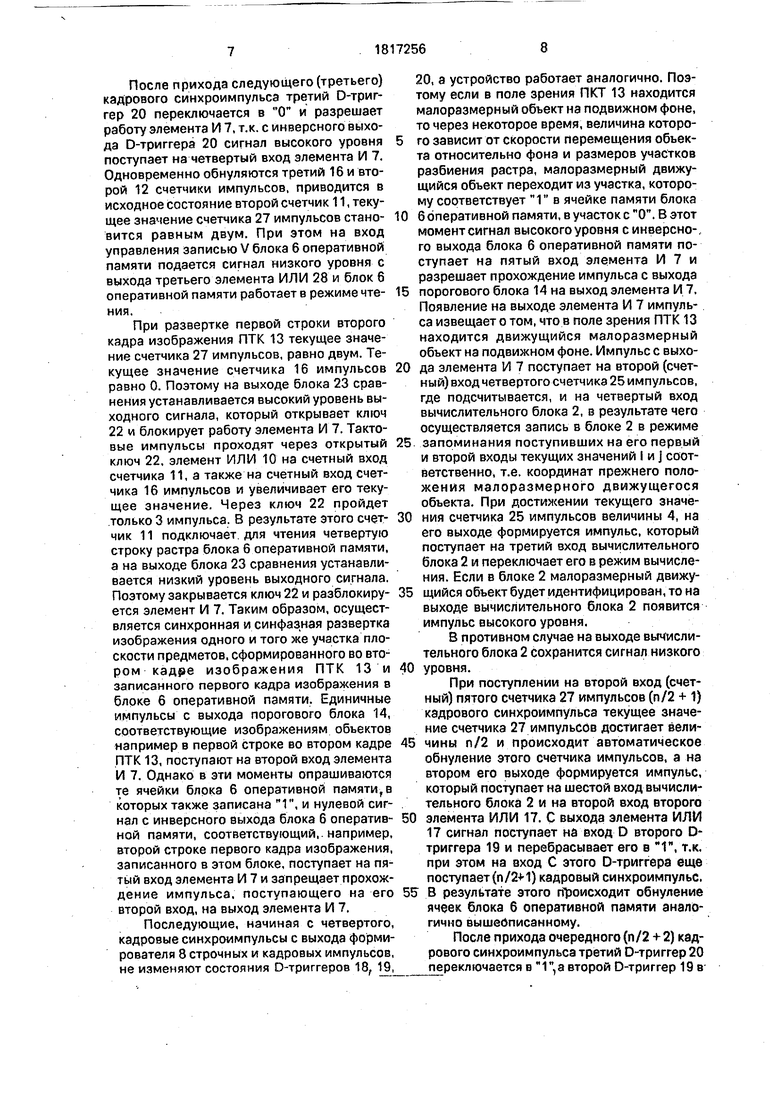

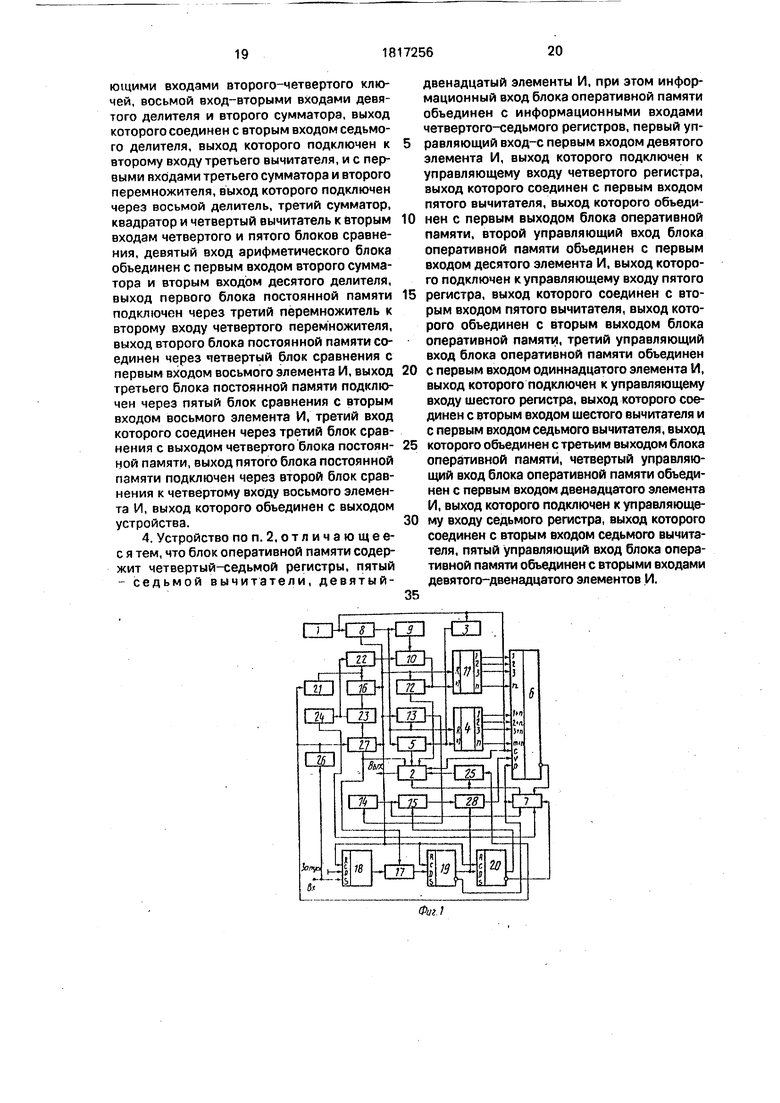

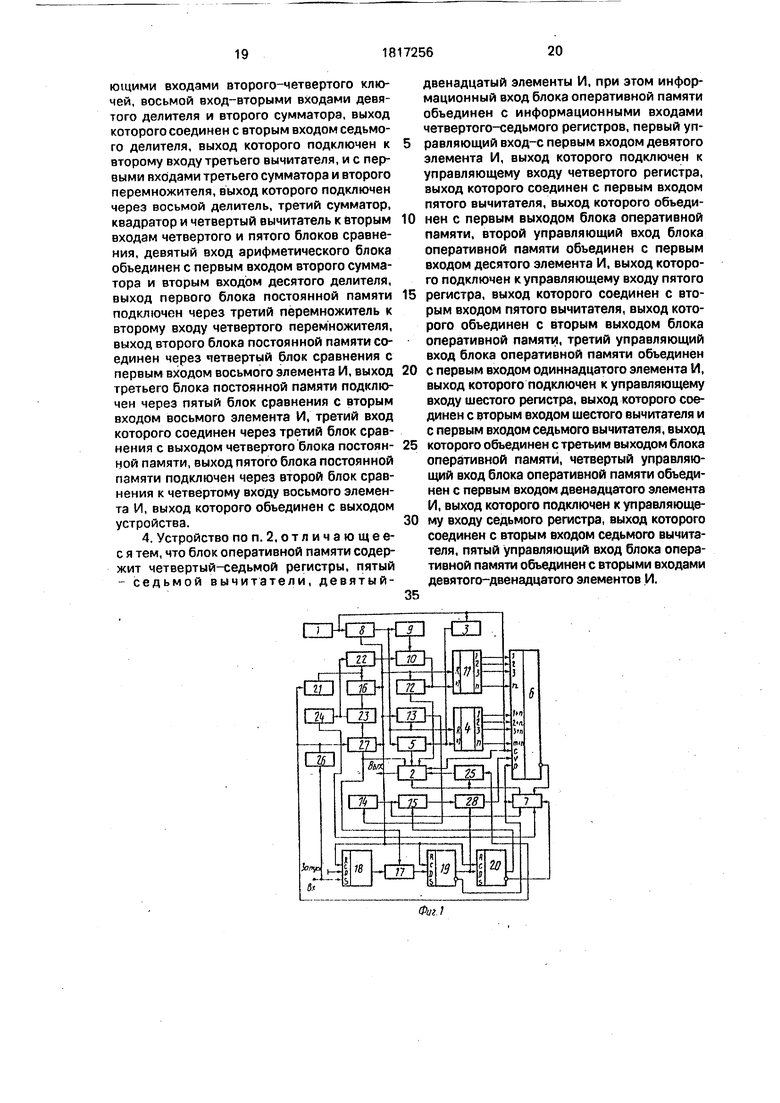

На фиг. 1 изображена структурная электрическая схема устройства для обнаружения движущихся объектов; на фиг. 2 - структурная электрическая схема вычислительного блока устройства для обнаружения движущихся объектов; на фиг. 3 - структурная электрическая схема арифметического блока устройства для обнаружения движущихся объектов; на фиг. 4 - структурная электрическая схема блока оперативной памяти устройства для обнаружения движущихся объектов.

Структурная электрическая схема устройства для обнаружения движущихся объек- тов содержит первый генератор 1 импульсов, вычислительный блок 2, первый делитель 3 частоты, первый счетчик 4. первый счетчик 5 импульсов, блок 6 оперативной памяти, первый элемент И 7, формирователь 8 строчных и кадровых импульсов, второй делитель 9 частоты, первый элемент ИЛИ 10, второй счетчик 11, второй счетчик 12 импульсов, передающая телевизионная камера 13(ПТК), пороговый блок 14, второй элемент И 15, третий счетчик 16 импульсов, второй элемент ИЛИ 17, первый D-триггер 18, второй D-триггер 19, третий D-триггер 20, второй генератор 21 импульсов, первый ключ 22, первый блок 23 сравнения, элемент НЕ 24, четвертый счетчик 25 импульсов, первый блок 26 задержки, пятый счетчик 27 импульсов, третий элемент ИЛИ 28.

у

Ё

00

ю ел сь

fe

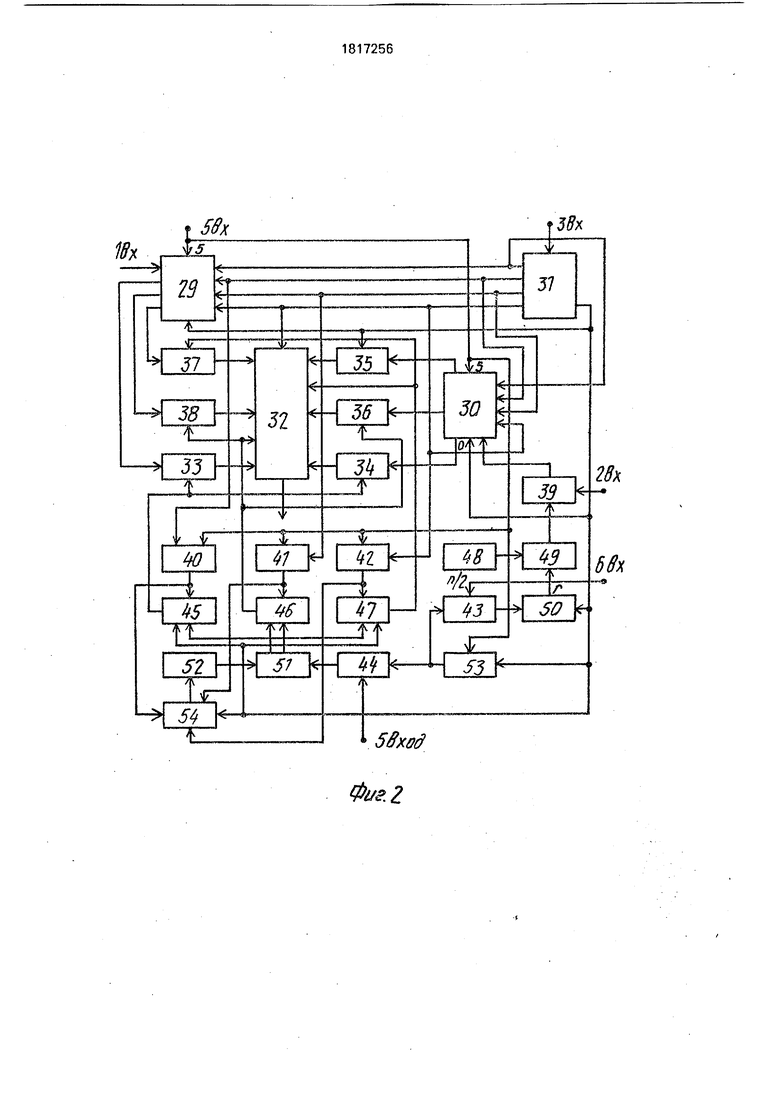

.Структурная электрическая схема вычислительного блока 2 устройства для обнаружения движущихся объектов (фиг, 2) содержит первый блок 29 оперативной памяти, второй блок 30 оперативной памяти, дешифратор 31, арифметический блок 32, первый делитель 33, второй делитель 34, третий делитель 35, четвертый делитель 36, пятый делитель 37, шестой делитель 38, первый сумматор 39, третий элемент И 40, четвертый элемент И 41, пятый элемент И 42, шестой элемент И 43, седьмой элемент И 44, первый регистр 45, второй регистр 46, третий регистр 47, блок 48 постоянной памяти, первый перемножитель 49, шестой счетчик 50 импульсов, седьмой счетчик 51 импульсов, второй блок 52 задержки, триггер 53, четвертый элемент ИЛИ 54.

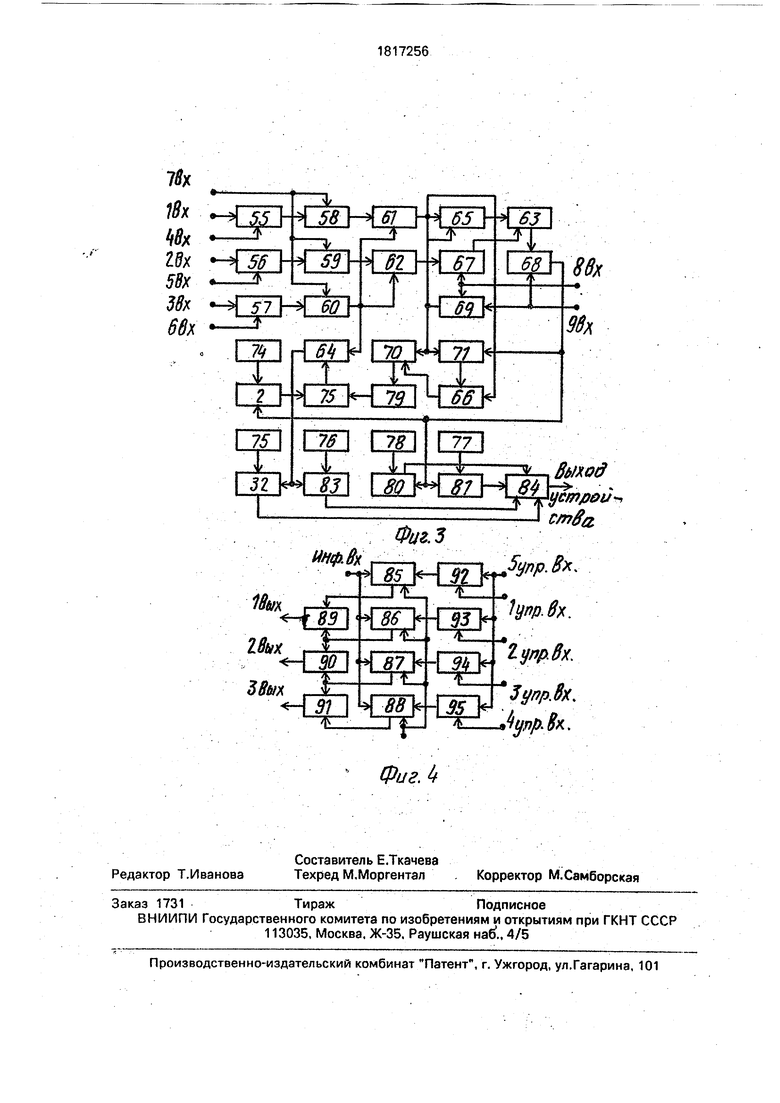

Структурная электрическая схема арифметического блока 32 устройства для обнаружения движущихся объектов (фиг. 3) содержит первый арифметический элемент 55, второй арифметический элемент 56, третий арифметический элемент 57, второй ключ 58, третий ключ 59, четвертый ключ 60, первый вычитатель 61, второй вычитатель 62, третий вычитатель 63, четвертый вычитатель 64, седьмой делитель 65, восьмой делитель 66, девятый делитель 67, десятый делитель 68, второй сумматор 69, третий сумматор 70, второй перемножитель 71, третий, перемножитель 72, четвертый перемножитель 73, блок 74 постоянной памяти, блок 75 постоянной памяти, блок 76 постоянной памяти, блок 77 постоянной памяти, второй блок 80 сравнения, третий блок 81 сравнения, четвертый блок 82 сравнения, пятый блок 83 сравнения, восьмой элемент И 84.

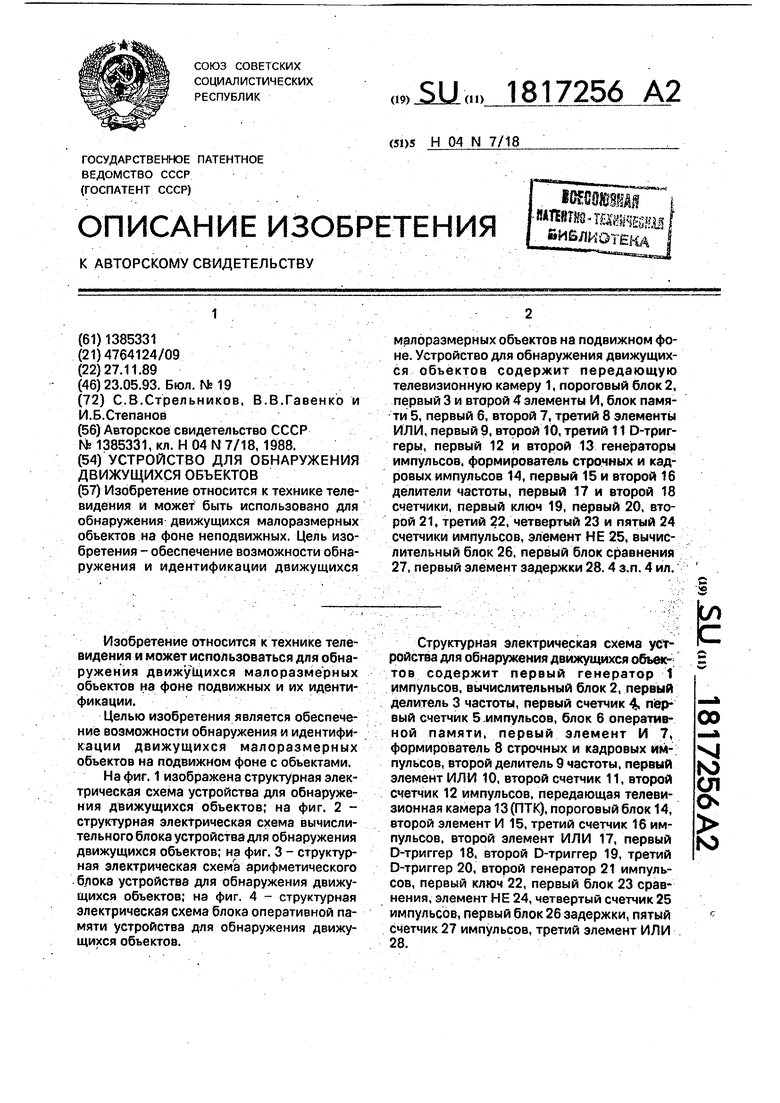

Структурная электрическая схема блока 29, 30 оперативной памяти устройства для обнаружения движущихся объектов (фиг. 4) содержит четвертый регистр 85, пятый регистр 86, шестой регистр 87, седьмой регистр 88, пятый вычитатель 89, шестой вычитатель 90, седьмой вычитатель 91, девятый элемент И 92, десятый элемент И 93, одиннадцатый элемент И 94, двенадцатый элемент И 95.

Работа устройства. В исходном состоянии D-триггера 18, 19,20, образующие сдвиговый регистр, находятся в нулевом состоянии. Счетчики 5.12,16,25,27 импульсов обнулены. Генераторы 1,21 отключены. Ключ 22 разомкнут.

При включении устройства запускается первый генератор 1 импульсов ( с выхода которого импульсы дискретизации поступают на вход формирователя 8 строчных и кадровых импульсов, нэ вход первого делителя частоты 3, на вход С блока 67 оперативной памяти и на пятый вход вычислительно-, го блока 2. Строчные импульсы с первого выхода формирователя 8 поступают на вход

второго делителя 9 частоты, на вход R (установочный) первого счетчика 4, на первый вход ПТК 13 и на первый вход (вход обнуления) первого счетчика 5 импульсов, обнуляя его. Кадровые импульсы со второго входа

0 формирователя 8 поступают на первые вхо- ды(входы обнуления) третьего 16 и второго 12 счетчиков импульсов, обнуляя их, на вход R (установочный) второго счетчика 11, на второй вход ПТК 13, на второй (счетный)

5 вход пятого счетчика 27 импульсов, где подсчитываются, на стробирующие входы С первого 18, второго 19 и третьего 20 D-триг- геров. Импульсы с выхода второго делителя 9 частоты поступают на первый вход перво0 го элемента ИЛИ 10, с выхода которого они проходят на вторые (счетные) входы второго счетчика 11 и второго счетчика 12 импульсов, где подсчитываются. Импульсы с выхода первого делителя 3 частоты поступают на

5 вторые (счетные) входы первого счетчика 4 и первого счетчика 5 импульсов, где подсчитываются.

Текущее значение j (номер строки растра) с выхода второго счетчика 12 импульсов

0 поступает на второй вход вычислительного блока 2, на первый вход которого поступает текущее значение 1 (номер элемента в строке растра) с выхода первого счетчика 5 импульсов. При движении луча ПТК 13 по

5 строке импульсы дискретизаций, поступающие через первый делитель 3 частоты, на первый счетчик 4, меняют состояние последнего через каждые К импульсов, где К-- коэффициент деления первого делителя 3.

0 частоты. Строка, таким образом, разбивается на участки, каждому из которых соответствует определенное состояние первого счетчика 4, То же самое происходит при движении луча при кадровой развертке.

5 Кадр разбивается на горизонтальные полосы при помощи второго делителя 9 частоты и второго счетчика 11. В результате этого весь растр оказывается разбитым на прямоугольные участки, каждому из которых соот0 ветствует определенное состояние счетчиков 11 и 4 и определенная ячейка tj блока 6 оперативной памяти. Причем при прохождении лучом развертки каждого такого участка на адресных входах блока 6,

5 оперативной памяти устанавливается адрес ячейки, соответствующий этому участку. Выходной сигнал (текущий номер кадра) пятого счетчика импульсов 27 с его первого выхода поступает в параллельном коде на второй вход блока 23 сравнения, на первый

вход которой поступает в параллельном коде текущее значение (пока равное нулю) с выхода третьего счетчика 16 импульсов. Если код на первом входе блока 23 сравнения не больше, чем код на втором ее входе, то на выходе блока 23 сравнения формируется сигнал высокого уровня (1). Иначе формируется сигнал низкого уровня (О). Выход- . ной сигнал блока 23 сравнения поступает на первый (управляющий) вход ключа 22 и на Bjcofl элемента НЕ 24. При этом единичный сигнал с выхода блока 23 сравнения открывает ключ 22 и, проходя через элемент НЕ 24, где инвертируется, на третий вход первого элемента И 7, блокирует последний. Нулевой сигнал с выхода блока 23 сравнения не изменяет разомкнутое состояние ключа 22 и разрешает работу первого элемента И 7. Выходной сигнал ПКТ 13 поступает на вход порогового блока 14.

Сигнал Запуск поступает на первый вход (вход обнуления) четвертого счетчика

25 импульсов, обнуляя его, на выход блока

26 задержки, где задерживается на время Тк, на установочный вход S первого D-триг- гера 18, перебрасывая его в 1. Этот сигнал 1 поступает через второй элемент ИЛИ 17 на вход второго D-триггера 19. Очередной (первый) кадровый синхроимпульс устанавливает в 1 второй D-триггер 19 и сбрасывает в О первый D-триггер 18, обнуляет третий 16 и второй 12 счетчики импульсов, приводит в исходное состояние второй счетчик 11, увеличивает на единицу текущее значение пятого счетчика 27 импульсов. Через некоторое время с выхода блока 26 задержки задержанный сигнал Запуск поступает на первые входы (входы обнуления) пятого 27 и четвертого 25 счетчиков импульсов, обнуляя их и на управляющий вход второго генератора 21 импульсов и запускают его. Тактовые импульсы с выхода второго генератора 21 поступают на второй (информационный) вход ключа 22 и на второй (четный) вход третьего счетчика 16 импульсов, где подсчитываются. Так как текущее значение пятого счетчика 27 импульсов равно 0, то на выходе блока 23 сравнения формируется сигнал высокого уровня, благодаря чему блокируется первый элемент И 7, ключ 22 открывается и пропускает тактовые импульсы с выхода второго генератора 21 импульсов, на второй вход первого элемента ИЛИ 10. Так как эти импульсы одновременно поступают, на второй вход первого элемента ИЛИ 10 пройдет только один тактовый импульс, после чего на выходе блока 23 сравнения установится сигнал низкого уровня и поэтому ключ 22 закроется, В результате этого развертка

ячеек блока 6 оперативной памяти начинается со второй строки. Сигнал высокого уровня с прямого выхода второго D-триггера 19 проходит через третий элемент ИЛИ 5 на вход управления записью V и удерживает блок 6 оперативной памяти в режиме записи. При этом на информационный вход Р блока 6 оперативной памяти подается О с инверсного выхода второго D-триггера 19.

10 Этот же потенциал, поступая на первый вход первого элемента И 7 блокирует работу этого элемента И, Таким образом, во все ячейки, начиная со второй строки, записываются О, т.е. происходит очистка блока 6

5 оперативной памяти.

После прихода следующего (второго) кад- - рового синхроимпульса третий D-триггер 20 переключается в 1, а второй D-триггер 19 в О. Одновременно обнуляется третий 16

0 и второй 12 счетчики импульсов, приводится в исходное состояние второй счетчик 11, текущее значение пятого счетчика 27 им- лульсов увеличивается на единицу и становится равным одному. Устанавливается

5 высокий уровень выходного сигнала блока 23 сравнения.

Благодаря этому блокируется элемент И 7, открывается ключ 22 и пропускает тактовые импульсы с выхода генератора 21 им0 пульсов на второй вход элемента ИЛИ 10. Т.к. текущее значение счетчика 27 импульсов равно одному, то на второй вход элемента ИЛИ 10 пройдет только два тактовых импульса, после чего на выходе блока 23

5 сравнения устанавливается сигнал низкого уровня и ключ 22 закроется. В результате этого развертка ячеек блока 6 оперативной памяти начинается с третьей строки. Сигнал высокого уровня с прямого выхода третьего

0 D-триггера 20 поступает на первый вход второго элемента И 15 и разрешает прохождение импульсов с выхода порогового;блока 14 через элемент И 15 на первый вход третьего элемента ИЛИ 28 и далее на вход управ5 ления записью V блока 6 оперативной памяти. При этом на первый вход первого элемента И 7 и на информационный вход Р блока 6 оперативной памяти подается 1 с инверсного выхода второго D-триггера 19.

0 Таким образом, сигнал Г первого кадра изображения записывается, начиная с третьей строки, только в те ячейки памяти блока 6, которые соответствуют участкам растра, содержащим изображение объектов

5 как движущихся, так и подвижного фона, расположенных в первом кадре изображения. Элемент И 7 блокируется низким уровнем с инверсного выхода третьего D-триггера 20, поступающим на его четвертый вход.

После прихода следующего (третьего) кадрового синхроимпульса третий D-триг- гер 20 переключается в О и разрешает работу элемента И 7, т.к. с инверсного выхода D-триггера 20 сигнал высокого уровня поступает на четвертый вход элемента И 7. Одновременно обнуляются третий 16 и второй 12 счетчики импульсов, приводится в исходное состояние второй счетчик 11, текущее значение счетчика 27 импульсов становится равным двум. При этом на вход управления записью V блока 6 оперативной памяти подается сигнал низкого уровня с выхода третьего элемента ИЛИ 28 и блок 6 оперативной памяти работает в режиме чтения.

При развертке первой строки второго кадра изображения ЛТК 13 текущее значение счетчика 27 импульсов, равно двум. Текущее значение счетчика 16 импульсов равно 0. Поэтому на выходе блока 23 сравнения устанавливается высокий уровень выходного сигнала, который открывает ключ 22 и блокирует работу элемента И 7. Тактовые импульсы проходят через открытый ключ 22, элемент ИЛИ 10 на счетный вход счетчика 11, а также на счетный вход счетчика 16 импульсов и увеличивает его текущее значение. Через ключ 22 пройдет только 3 импульса. В результате этого счетчик 11 подключает, для чтения четвертую строку растра блока 6 оперативной памяти, а на выходе блока 23 сравнения устанавливается низкий уровень выходного сигнала. Поэтому закрывается ключ 22 и разблокируется элемент И 7. Таким образом, осуществляется синхронная и синфазная развертка изображения одного и того же участка плоскости предметов, сформированного во втором кадре изображения ПТК 13 и записанного первого кадра изображения в блоке 6 оперативной памяти. Единичные импульсы с выхода порогового блока 14, соответствующие изображениям объектов например в первой строке во втором кадре ПТК 13, поступают на второй вход элемента И 7. Однако в эти моменты опрашиваются те ячейки блока 6 оперативной памяти,в которых также записана 1, и нулевой сигнал с инверсного выхода блока 6 оперативной памяти, соответствующий,, например, второй строке первого кадра изображения, записанного в этом блоке, поступает на пятый вход элемента И 7 и запрещает прохождение импульса, поступающего на его второй вход, на выход элемента И 7.

Последующие, начиная с четвертого, кадровые синхроимпульсы с выхода формирователя 8 строчных и кадровых импульсов, не изменяют состояния D-триггеров 18, 1J),

20, а устройство работает аналогично. Поэтому если в поле зрения ПКТ 13 находится малоразмерный объект на подвижном фоне, то через некоторое время, величина которого зависит от скорости перемещения объекта относительно фона и размеров участков разбиения растра, малоразмерный движущийся объект переходит из участка, которому соответствует 1 в ячейке памяти блока

0 6 оперативной памяти, в участок с О. В этот момент сигнал высокого уровня с инверсно-, го выхода блока 6 оперативной памяти поступает на пятый вход элемента И 7 и разрешает прохождение импульса с выхода

5 порогового блока 14 на выход элемента И 7, Появление на выходе элемента И 7 импульса извещаете том, что в поле зрения ПТК 13 находится движущийся малоразмерный объект на подвижном фоне. Импульс с выхо0 да элемента И 7 поступает на второй (счетный) вход четвертого счетчика 25 импульсов, где подсчитывается, и на четвертый вход вычислительного блока 2, в результате чего осуществляется запись в блоке 2 в режиме

5. запоминания поступивших на его первый и второй входы текущих значений I и j соответственно, т.е. координат прежнего положения малоразмерного движущегося объекта. При достижении текущего значе0 ния счетчика 25 импульсов величины 4, на его выходе формируется импульс, который поступает на третий вход вычислительного блока 2 и переключает его в режим вычисления. Если в блоке 2 малоразмерный движу5 щийся объект будет идентифицирован, то на выходе вычислительного блока 2 появится импульс высокого уровня.

В противном случае на выходе вычислительного блока 2 сохранится сигнал низкого

0 уровня.

При поступлении на второй вход (счетный) пятого счетчика 27 импульсов (п/2 + 1) кадрового синхроимпульса текущее значение счетчика 27 импульсов достигает вели5 чины п/2 и происходит автоматическое обнуление этого счетчика импульсов, а на втором его выходе формируется импульс, который поступает на шестой вход вычислительного блока 2 и на второй вход второго

0 элемента ИЛИ 17. С выхода элемента ИЛИ 17 сигнал поступает на вход D второго D- триггера 19 и перебрасывает его в 1, т.к. при этом на вход С этого D-триггера еще поступает () кадровый синхроимпульс.

5 В результате этого происходит обнуление ячеек блока 6 оперативной памяти аналогично вышеописанному.

После прихода очередного (п/2 + 2) кадрового синхроимпульса третий D-триггер 20 переключается в Г,а второй D-триггер 19 в

0й. Благодаря этому осуществляется запись очередного (п/2 + 1) кадра изображения в ячейки блока 6 оперативной памяти аналогично вышеописанному.

При поступлении следующего (п/2 + 3) кадрового синхроимпульса третий D-триг- гер 20 переключается в О и разрешает работу элемента И 7. В результате этого осуществляется сравнение одноименных участков (п/2 + 2) кадра изображения, фор- мйруемого в ПТК 13, записанного в ячейках блока 6 оперативной памяти (п/2 + 1) кадра изображения. В дальнейшем устройство работает аналогино.

Работа вычислительного блока 2. В ис- ходном состоянии в блоке 48 постоянной памяти записано значение п/2, счетчики 30, 31 импульсов, обнулены.

При включении устройства на первый вход и далее на информационный вход бло- ка 29 оперативной памяти поступает текущее значение I. На второй вход и далее на второй вход сумматора 39 поступает текущее значение j. На третий вход и далее на вход дешифратора 31 поступает текущее значение счетчика 25 импульсов. На четвертый вход и далее на управляющие входы блоков 29, 30 оперативной памяти, на первые входы элементов И 40,41,42 и триггера 53 поступают импульсы с выхода элемента И 7. На пятый вход и далее на первый вход элемента И 44 поступают тактовые импульсы с выхода генератора 1 импульсов. На шестой вход и далее на первый вход элемента И 43 поступают импульсы с выхода счет- чика 27 импульсов.

При поступлении на третий вход вычислительного блока 2 на нулевом выходе дешифратора 31 устанавливается сигнал высокого уровня, который поступает на входы обнуления регистров 45, 46, 47 обнуляя их, блоков 29, 30, оперативной памяти, обнуляя их, счетчика 50 импульсов, обнуляя его, второй вход триггера 53, перебрасывая его в О , и на первый вход элемен- та ИЛИ 54, с выхода которого проходит через блок 52 задержки, задерживаясь на время тз, на вход обнуления счетчика 51 импульсов и обнуляет его. Сигнал низкого уровня с выхода триггера 53 поступает на вторые входы элементов И 43,44 и закрывает их. Следовательно происходит подготовка к работе вычислительного блока 2.

При появлении в поле зрения ПТК 13 малоразмерного движущегося объекта на выходе элемент И 7 формируется первый импульс, который через четвертый вход вычислительного блока 2 поступает на первые входы элементов И 40, 41,42 и триггера 53, перебрасывая его в на пятые управляющие входы блоков 29,30 оперативной памяти, обеспечивая запись в них соответственно текущих значений h,j , характеризующих положение обнаруженного объекта в поле зрения ПТК 13. Сигнал высокого уровня с выхода триггера 53 поступает на вторые входы элементов И 43,44,58 и открывает их. При этом на третий вход вычислительного блока 2 поступает код 001, благодаря чему на первом выходе дешифратора 31 устанавливается сигнал высокого уровня, который поступает на первые управляющие входы блоков 29,30 оперативной памяти, благодаря чему запись значений h,ji осуществляется в первые ячейки памяти этих блоков. Тактовые импульсы с пятого входа блока 2 проходят через открытый элемент И 44 на счетный вход счетчика 51 импульсов, где подсчитываются. С выхода счетчика 51 импульсов его текущее значение А поступает одновременно на информационные входы регистров 45. 46, 47. Импульсы с шестого входа блока 2 проходят через открытый элемент И 57 на счетный вход счетчика 50 импульсов, где подсчитываются. С выхода счетчика 50 импульсов его текущее значение г поступает на первый вход перемножителя 49, на второй вход которого с выхода блока 48 постоянной памяти постоянно поступает значение п/2. Полученное произведение гп/2 с выхода перемножителя 49 поступает на первый вход сумматора 36, где складывается с поступающим на второй вход сумматора 39 текущим значением J. Полученная сумма j j + rn/2 с выхода сумматора 39 поступает на информационный вход блока 30 оперативной памяти. Очередные импульсы, поступающие на первый вход триггера 53, не изменяют его состояния.

Второй импульс, поступающий на четвертый вход блока 2, проходит на первые входы элементов И 40, 41,42 и триггера 53, на пятые управляющие входы блоков 29, 30 оперативной памяти, обеспечивая запись в них соответственно текущих значений i2,j 2. При этом на третий вход блока 2 поступает код 010, благодаря чему на втором выходе дешифратора 31 устанавливается сигнал высокого уровня, который поступает на вторые управляющие входы блоков 29, 30 оперативной памяти, благодаря чему запись значений i2,j 2 осуществляется во вторые ячейки памяти этих блоков, и на второй вход элемента И 40, открывая его. Поэтому второй импульс с четвертого входа блока 2 пройдет через открытый элемент И 40 на третий вход элемента ИЛИ 54 и на управляющий вход (вход записи) регистра 45, в результате чего произойдет запись текущего

значения Alia счетчика импульсов 51 в регистр 47. С выхода элемента ИЛИ 54 второй импульс пройдет через блок 52 задержки, где задержится на время гз, на вход обнуления счетчика импульсов 51 и обнуляет его. Следовательно, значение Ali2 пропорционально интервалу времени между поступлением на четвертый вход первого и второго импульсов. Значение ДНа с выхода регистра 45 поступает на вторые входы делителей 33 и 34, С первого выхода блока 29 оперативной памяти на первый вход делителя 33 поступает значение . Полученное частное (t2-H)/A 112 с выхода делителя 33 поступает на третий вход арифметического блока 32. С первого выхода блока 30 оперативной памяти на первый вход делителя 34 поступает значение }Vj i. Полученное частное G 2-j t)/Ali2C выхода делителя 34 поступает на шестой вход арифметического блока 32. Третий импульс, поступающий на четвертый вход блока 2, проходит на первые входы элементов И 40,41,42 и триггера 53, на пятые управляющие входы блоков 29,30 оперативной памяти, обеспечивая запись в них соответственно текущих значений 1з,Гз- При этом на третий вход блока 2 поступает код 011, благодаря чему на третьем выходе дешифратора 31 устанавливается сигнал высого уровня, который поступает на третьи управляющие входы блоков 29,30 оперативной памяти, благодаря чему запись значений ЬЛ з осуществляется в третьи ячейки памяти этих блоков, и на второй вход элемента И 41, открывая его. Поэтому третий импульс с четвертого входа блока 2 пройдет через открытый элемент И 41 на четвертый вход элемента ИЛИ 54 и на управляющий вход (вход записи) регистра 46, в результате чего произойдет запись текущего значения AI23 счетчика 51 импульсов в регистр 46. С выхода элемента ИЛИ 54 третий.импульс пройдет через блок 52 задержки, где задержится на время гз, на вход обнуления счетчика 51 импульсов и обнулит его, Следовательно, значение Aha пропорционально интервалу время между поступлением на четвертый вход блока 2 второго и третьего импульсов. Значение AI23C выхода регистра 46 поступает на вторые входы делителей 36,38 и на восьмой вход арифметического блока 32. Со второго выхода блока 29 оперативной памяти на первый вход делителя 38 поступает значение Ы2 Получен- ное (1з-12)/Д123 с выхода делителя 38 поступает на второй вход арифметического блока 32. Со второго выхода блока 30 оперативной памяти на первый вход делителя 36 поступает значение js -jz. Полученное

частное )/Д 23 с выхода делителя 36 поступает на пятый вход арифметического блока 32,.

Четвертый импульс, поступающий на

четвертый вход блока 2, проходит на первые входы элементов И 40, 41, 42 и триггера 53, на пятые управляющие входы блоков 29, 30 оперативной памяти, обеспечивая запись в них соответственно текущих значений М и

j4

При этом на третий вход блока 2 поступает код 100, благодаря чему на четвертом выходе дешифратора 31 устанавливается сигнал высокого уровня, который поступает

на четвертые управляющие входы блоков 29,30 оперативной памяти, благодаря чему запись значений U и № осуществляется в четвертые ячейки памяти этих блоков, на второй вход элемента И 42 и, открывая его,

на седьмой вход арифметического блока 32. Поэтому четвертый импульс с четвертого блока 2 пройдет через открытый элемент И 42 на второй вход элемента ИЛИ 54 и на управляющий вход (вход записи) регистра

47, в результате чего произойдет запись текущего значения ДЫ счетчика 51 импульсов в регистр 47. С выхода элемента ИЛИ 54 четвертый импульс пройдет через блок 52 задержки, где задержится на время тз, на

вход обнуления счетчика 51 импульсов и обнулит его. Следовательно значение АЫ пропорционально интервалу времени между поступлением на четвертый вход бл. 2 третьего и четвертого импульсов. Значение

А1з4 с выхода регистра 47 поступает на вторые входы делителей 35, 37 и на девятый вход арифметического блока 32. С третьего выхода блока 29 оперативной памяти на первый вход делителя 37 поступает значение . Полученное частное (14-1з)7Д1з4 с выхода делителя 37 поступает на первый вход арифметического блока 32, на выходе которого формируется сигнал низкого или высокого уровня.

Очередной импульс, поступающий на четвертый вход блока 2, проходит на первые входы элементов И 40,41,42 и триггера 53, на пятые управляющие входы блоков 29,30, не изменяя их состояния. При этом на третий вход блока 2 поступает код 000, благодаря чему на нулевом выходе дешифратора 31 устанавливается сигнал высокого уровня и происходит подготовка к работе вычислительного блока 2. В дальнейшем.вычислительный блок 2 работает аналогично. Работа арифметического блока 32. В исходном состоянии в блоке 74 посто- янной памяти записано значение 0,25; в блоке 75 постоянной памяти записано значение V0 max. В блоке 76 постоянной памяти записано значение V0 min, в блоке 78 постоянной памяти записано значение атах. в блоке 77 постоянной памяти записано значение amin. При включении устройства на первый вход блока 32 и далее на первый вход арифметического элемента 55 поступает значение Via. На четвертый вход блока 32 и далее на второй вход арифметического элемента 55 поступает значение Vja. Полученное значение Va с выхода арифметического элемента 55 поступает на информационный вход ключа 58. На второй вход блока 32, далее на первый вход арифметического элемента 56 поступает значение Vi2. На пятый вход блока 32 и далее на второй вход арифметического элемента 56 поступает значение У|2. Полученное значение /2 - Vy& + v c выхода арифметиче- ского элемента 56 поступает на информационный вход ключа 59. На третий вход блока 52 и далее на первый вход арифметического элемента 57 поступает значение Vii. На шестой вход блока 32 и далее на второй вход арифметического элемента 57 поступает значение У. Полученное значение Vi - V vfr -Ь vft с выхода арифметического элемента 57 поступает на информационный вход ключа 60. На восьмой вход блока 2 и далее на вторые входы делителей 56 и сумматора 69 поступает значение А)23- На девятый вход блока 32 и далее на первый вход сумматора 69 и на второй вход делителя 68 поступает значение Л Ы. На седьмой вход блока 32 и далее на управляющие входы ключей 58, 59, 60 поступает импульс, который открывает указанные ключи. Значение /з с выхода ключа 58 поступает на первый вход вычитателя 61. Значение Mz с выхода ключа 59 поступает на первый вход вычитателя 62. Значение Vr с выхода ключа 60 поступает на вторые входы вычитателей 61, 62, 64. Полученная разность Vi-V/зс выхода вычитателя 61 поступает на первые входы делителей 65, 66. Полученная сумма Ates + А Ы с выхода сумматора 69 поступает на второй вход делителя 65 и на первые входы сумматора 70 и перемножителя 71. Полученное частное (Vi- Vs)/ (Ai23 + АЫ) с выхода делителя 65 поступает на второй вход вычитателя 63, выходнойсигнал которого

Vi -V3 ,. Vi + Vz (А|2з + ДЫ +™&lir- постУпает на первый вход делителя 68. Полученное значение а с выхода делителя 68 поступает на вторые входы перемножителей 71,72 и блоков 80, 81 сравнения. Полученное произведение ( Д123 + А Ы) с выхода перемножителя

71 поступает на второй вход делителя 66, с выхода которого полученное частное (Vi- /з) + А 1з4)а поступает на второй вход сумматора 70. Полученная сумма с выхода 5 сумматора 70 поступает через квадратор 79 на первый вход перемножителя 73. С выхода блока 74 постоянной памяти значение 0,25 поступает на первый вход перемножителя 72, с выхода которого полученное про0 изведение 0,25 поступает на второй вход перемножителя 73. Полученное произведение с выхода перемножителя 73 поступает на первый вход вычитателя 64, с выхода которого полученное значение поступает на

5 вторые входы блоков 82, 83, сравнения. С выхода блока 75 постоянной памяти значение V0 max поступает на первый вход блока 82 сравнения, на выходе которого формируется сигнал высокого уровня, поступающий

0 на первый вход элемента И 84, только в том случае, если выполняется неравенство V0 V0 max. С выхода блока 76 постоянной памяти значение V0 mm поступает на первый вход блока 83 сравнения, на выходе которо5 го формируется сигнал высокого уровня, поступающий на второй вход элемента И 84, только s том случае, если выполняется неравенство V0 Ve пш. С выхеда блока 78 постоянной памяти значение атах поступает

0 на первый вход блоке 80 сравнения, на выходе которого формируется сигнал высокого уровня, поступающий на четвертый вход элемента И 34, только в том случае, если выполняется неравенство а атах. С выхода

5 блока 77 постоянной пемятм значение amin поступает на первый вход блока 81 сравнения, на выходе которого формируется сигнал высокого уровня, поступающий на третий вход элемента И 84, только в том

0 случае, если выполняется неравенство а amin. Если на все входы элемента И 84 одновременно поступят сигналы высокого уровня, то на выхода элемента И 84 сформируется сигнал высокого уровня, свидетель5 ствующий об идентификации объекта, и он поступит на выход устройства для обнаружения движущихся объектов. В противном случае на выходе устройства будет сохраняться сигнал низкого уровня. В дэльней0 шем арифметический блок 32 работает аналогично,

Работа блоков 29,30 оперативной памяти. На информационный вход блока 29,30 и далее на информационные входы регистров

5 85,86,87,88 поступает входной сигнал (значение i или J). На вход обнуления блока 29 (30) и далее на входы обнуления регистров 85, 86, 87, 88 поступает импульс обнуления и обнуляет указанные регистры. На первый управляющий вход блока 29 (30) и далее на

первый вход элемента И 92 поступает первый управляющий импульс и открывает его. На второй управляющий вход блока 29 (30) и далее на первый вход элемента И 93 поступает второй управляющий импульс и открывает его. На третий управляющий вход блока 29 (30) и далее на первый вход элемента И 94 поступает третий управляющий импульс и открывает его. На четвертый управляющий вход блока 29 (30) и далее на первый вход элемента И 95 поступает четвертый управляющий импульс и открывает его. На пятый управляющий вход блока 29 (30) поступает управляющий импульс и далее проходит на вторые входы элементов И 92, 93, 94, 95. Этот импульс проходит через один из открытых элементов И 92,93,94,95 на управляющий вход (вход записи) соответствующего одного из регистров 85, 86, 87, 88, в который и записывается входной сигнал с информационного входа. Выходной сигнал регистра 85 поступает на первый вход (вход вычитаемого) вычитателя 89. Выходной сигнал регистра 86 поступает на второй вход (вход уменьшаемого) вычитателя 89 и на первый вход (вход вычитаемого) вычитателя 90,

Полученная разность с выхода вычитателя 90 поступает на второй выход блока 29 (30). Выходной сигнал регистра 88 поступает на второй вход вычитателя 91, с выхода которого полученная разность поступает на третий выход блока 29 (30). В дальнейшем блоки оперативной памяти работают аналогично.

Таким образом, в предложенном устройстве после подачи сигнала Запуск при наличии движущегося малоразмерного объекта в полезрения ПТК13 на выходе элемента И 7 формируются выходные сигналы, свидетельствующие об обнаружении указанного объекта. Если параметры движения малоразмерного объекта соответствуют заданным в вычислительном блоке 2, то на выходе вычислительного блока 2 формируется выходной сигнал, свидетельствующий об идентификации малоразмерного движущегося, объекта. Следовательно, достигается поставленная цель изобретения.

Использование устройства позволит обнаруживать подижные малоразмерные объекты, имеющие скорость движения, отличную от скорости перемещения окружающего фона, и идентифицировать их при заданных параметрах движения. При этом устройство работоспособно, если скорость движения малоразмерного объекта находится в диапазоне значений 2V «S VA nV/2.

Формула изобретения 1. Устройство для обнаружения движущихся объектов по авт. св. № 138533 отличающееся тем, что, с целью обеспечения

возможности обнаружения и идентификации движущихся малоразмерных объектов на подвижном фоне, введены первый и второй элементы ИЛИ, второй генератор импульсов, ключ, пять счетчиков импульсов, элемент НЕ,

0 вычислительный блок, блок сравнения и блок задержки, причем первый выход формирователя строчных и кадровых импульсов соединен с входом обнуления первого счетчика импульсов, счетный вход которого подклю5 чен к выходу первого делителя частоты, второй выход формирователя строчных и кадровых импульсов соединен с входом обнуления третьего счетчика импульсов, выход которого подключен через блок

0 сравнения к управляющему входу ключа и входу элемента НЕ, выход которого подключен к третьему входу первого элемента И, и со счетным входом пятого счетчика импуль- сов, первый вход которого подключен к вто5 рому входу блока сравнения, выход второго делителя частоты соединен через первый элемент ИЛИ, второй вход которого подключен к выходу ключа, со счетными входами второго счетчика и второго счетчика

0 импульсов, выход которого подключен к второму входу вычислительного блока, первый вход которого соединен с выходом первого счетчика импульсов, установочный вход D- триггера объединен с входом блока задерж5 ки, выход которого подключен к входу обнуления пятого счетчика импульсов, второй выход которого соединен с шестым входом вычислительного блока и вторым входом второго элемента ИЛИ, который

0 включен между выходом первого ключа и входом третьего счетчика импульса, второй генератор импульсов, выход которого соединен с информационным входом первого ключа и со счетным входом третьего счетчи5 ка импул ьсов, и к входу обнуления четвертого счетчика импульсов, выход которого1 соединен с третьим входом вычислительного блока, выход которого объединен с выхо дом устройства, выход первого элемента И

0 подключен к четвертому входу вычислительного блока, пятый вход которого соединен в выходом первого генератора импульсов, и и счетному входу четвертого счетчика импульсов.

5 2. Устройство по я. 1,отличающее с я тем, что вычислительный блок содержит первый и второй блоки оперативной памяти, дешифратор, арифметический блок, шесть делителей, сумматор, третйй-седьмой эл&- менты И, три регистра, перемножитель, шестой и седьмой счетчики импульсов, второй блок задержки, триггер, четвертый элемент ИЛИ, первый блок постоянной памяти, при этом первый вход вычислительного блока объединен с информационным входом первого блока оперативной памяти, первый выход которого подключен через первый делитель к третьему входу арифметического блока, выход которого объединен с выходом устройства, второй вход вычислительного блока объединен с вторым входом первого сумматора, выход которого соединен с информационным входом второго блока оперативной памяти, первый выход которого подключен через второй делитель к шестому входу арифметического блока, четвертый вход которого соединен через третий делитель с третьим выходом второго блока оперативной памяти, второй выход которого подключен через четвертый делитель к пятому входу арифметического блока, первый вход которого соединен через пятый делитель с третьим выходом первого блока оперативной памяти, второй выход которого подключен через шестой делитель к второму входу арифметического блока, седьмой вход которого соединен с четвертым выходом дешифратора, нулевой выход которого подключен к первому входу четвертого элемента ИЛИ, к второму входу триггера и входам обнуления первого-третьего регистров, первого и второго блоков оперативной памяти и шестого счетчика импульсов, третий вход вычислительного блока объединен с входом дешифратора, первый-четвертый выходы которого соединены соответственно с управляющими первыми-четвертыми входами первого и второго блоков оперативной памяти, второй выход дешифратора подключен к второму входу третьего элемента И, выход которого соединен с управляющим входом первого регистра, выход которого подключен к вторым входам первого и второго делителей, и с третьим, входом четвертого элемента ИЛИ, выход которого подключен через второй блок задержки к входу обнуления седьмого счетчика импульсов, выход которого соединен с информационными входами первого-третьего регистров, третий выход дешифратора подключен к второму входу четвертого элемента И, выход которого соединен с управляющим входом второго регистра, выход которого подключен к вторым входам шестого и четвертого делителей и к восьмому входу арифметического блока, и с четвертым входом четвертого элемента ИЛИ, четвертый выход дешифратора подключен к второму входу пятого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ и с управляющим входом третьего регистра, выход которого подключен к вторым входам пятого и третьего делителей и к девятому входу арифметиче- 5 ского блока, четвертый вход вычислительного блока объединен с пятым управляющими входами первого и второго блоков оперативной памяти и с первыми входами треть- ero-пятого элементов И и триггера, выход

0 которого подключен к вторым входам шестого и седьмого элементов И, пятый вход вычислительного блока объединен с первым входом седьмого элемента И, выход которого подключен к счетному входу седьмого

5 счетчика импульсов, шестой вход вычислительного блока объединен с первым входом шестого элемента И, выход которого подключен к счетному входу шестого счетчика импульсов, выход которого соединен через

0 первый перемножитель, к второму входу которого подключен выход первого блока постоянной памяти,с первым входом первого сумматора.

3. Устройство по п. 2, о т л и ч а ю щ е е5 с я тем, что арифметический блок содержит три арифметических элемента, второй-чет- вертый ключи, четыре вычитателя, седьмой- десятый делители, второй и третий сумматоры, второй-четвертый перемножи0 телк, второй-шестой блоки постоянной памяти, регистр, квадратор, второй-пятый блоки сравнения и восьмой элемент И, причем первый вход арифметического блока объединен с первым входом первого ариф5 метического элемента, выход которого соединен с информационным входом второго ключа, выход которого подключен через первый вычитатель к первым входам седьмого и восьмого делителей, второй вход

0 арифметического блока объединен с первым входом второго арифметического элемента, выход которого соединен с информационным входом третьего ключа, выход которого подключен через второй вы5 читатель, девятый делитель, третий вычитатель и десятый делитель к вторым входам второго и третьего перемножителей, второго и третьего блоков сравнения, третий вход арифметического блока объединен с пер0 вым входом третьего арифметического элемента, выход которого соединен с информационным входом четвертого ключа, выход которого подключен к вторым входам первого, второго и четвертого вычитателей,

5 четвертый вход арифметического блока объединен с вторым входом первого арифметического элемента, пятый вход-с вторым входом арифметического элемента, шестой вход-с вторым входом третьего арифмети- ческого элемента, седьмой вход-с управляющими входами второго-четвертого ключей, восьмой вход-вторыми входами девятого делителя и второго сумматора, выход которого соединен с вторым входом седьмого делителя, выход которого подключен к второму входу третьего вычитателя, и с первыми входами третьего сумматора и второго перемножителя, выход которого подключен через восьмой делитель, третий сумматор, квадратор и четвертый вычитатель к вторым входам четвертого и пятого блоков сравнения, девятый вход арифметического блока объединен с первым входом второго сумматора и вторым входом десятого делителя, выход первого блока постоянной памяти подключен через третий перемножитель к второму входу четвертого перемножителя, выход второго блока постоянной памяти соединен через четвертый блок сравнения с первым входом восьмого элемента И, выход третьего блока постоянной памяти подключен через пятый блок сравнения с вторым входом восьмого элемента И, третий вход которого соединен через третий блок сравнения с выходом четвертого блока постоянной памяти, выход пятого блока постоянной памяти подключен через второй блок сравнения к четвертому входу восьмого элемента И, выход которого объединен с выходом устройства.

4. Устройство поп.2,отличающее- с я тем, что блок оперативной памяти содержит четвертый-седьмой регистры, пятый - седьмой вычитатели, девятыйдвенадцатый элементы И, при этом информационный вход блока оперативной памяти объединен с информационными входами четвертого-седьмого регистров, первый управляющий вход-с первым входом девятого элемента И, выход которого подключен к управляющему входу четвертого регистра, выход которого соединен с первым входом пятого вычитателя, выход которого объединен с первым выходом блока оперативной памяти, второй управляющий вход блока оперативной памяти объединен с первым входом десятого элемента И, выход которого подключен к управляющему входу пятого

регистра, выход которого соединен с вторым входом пятого вычитателя, выход которого объединен с вторым выходом блока оперативной памяти, третий управляющий вход блока оперативной памяти объединен

с первым входом одиннадцатого элемента И, выход которого подключен к управляющему входу шестого регистра, выход которого соединен с вторым входом шестого вычитателя и с первым входом седьмого вычитателя, выход

которого объединен с третьим выходом блока оперативной памяти, четвертый управляющий вход блока оперативной памяти объединен с первым входом двенадцатого элемента И, выход которого подключен к управляющему входу седьмого регистра, выход которого соединен с вторым входом седьмого вычитателя, пятый управляющий вход блока оперативной памяти объединен с вторыми входами девятого-двенадцатого элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство для обнаружения движущихся объектов | 1989 |

|

SU1734234A2 |

| Устройство для мажоритарного декодирования в целом | 1984 |

|

SU1243101A1 |

| Система оптимизации управления непосредственно и косвенно управляемыми объектами | 1982 |

|

SU1080117A1 |

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для обнаружения движущихся объектов | 1989 |

|

SU1697275A2 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

Изобретение относится к технике телевидения и может быть использовано для обнаружения: движущихся малоразмерных объектов на фоне неподвижных. Цель изобретения - обеспечение возможности обнаружения и идентификации движущихся малоразмерных объектов на подвижном фоне. Устройство для обнаружения движущихся объектов содержит передающую телевизионную камеру 1, пороговый блок 2, первый 3 и второй 4 элементы И, блок памяти 5, первый 6, второй 7, третий 8 элементы ИЛИ, первый 9, второй 10, третий 11 D-триг- геры, первый 12 и второй 13 генераторы импульсов, формирователь строчных и кадровых импульсов 14, первый 15 и второй 16 делители частоты, первый 17 и второй 18 счетчики, первый ключ 19, первый 20, второй 21, третий 22, четвертый 23 и пятый 24 счетчики импульсов, элемент НЕ 25, вычислительный блок 26, первый блок сравнения 27, первый элемент задержки 28.4 з.п. 4 ил.

0#е.2

- 5Ј

iym/дол

| Телевизионное устройство для обнаружения движущихся объектов | 1986 |

|

SU1385331A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-23—Публикация

1989-11-27—Подача