НИИ изображений, вычислителя 2 и коммутатора 9, что обеспечивает увеличение времени записи информации от внешнего источника в блок памяти

1

Изобретение относится к вычислительной технике и предназначено для отображения символьной и графической информации на телевизионных цветных экранах.

Цель изобретения - повышение быст- родействия устройства.

На фиг.1 приведена блок-схема устройства; на фиг.2 - блок-схема блока регенерации изображения; на фиг.З - блок-схема вычислителя; на фиг.4 - блок-схема коммутатора.

Устройство для формирования изображения на экране телевизионного приемника содержит блок 1 приема данных вычислитель 2, первую 3, вторую 4 и третью 5. группы инверторов, первьй 6, второй 7 и третий 8 сумматоры, коммутатор 9, первый 10, второй 11 и третий 12 блоки памяти, первьй 13, второй 14 и третий 15 преобразователи кодов, блок 16 регенерации изображения, формирователь 17 видеосигнала, первую 18, вторую 19 и третью 20 группы элементов И, первый 21, второй 22, третий 23, четвертьй 24, пятый 25 и шестой 26 регистры, первый 27, второй 28 и третий 29 элементы ИЛИ.

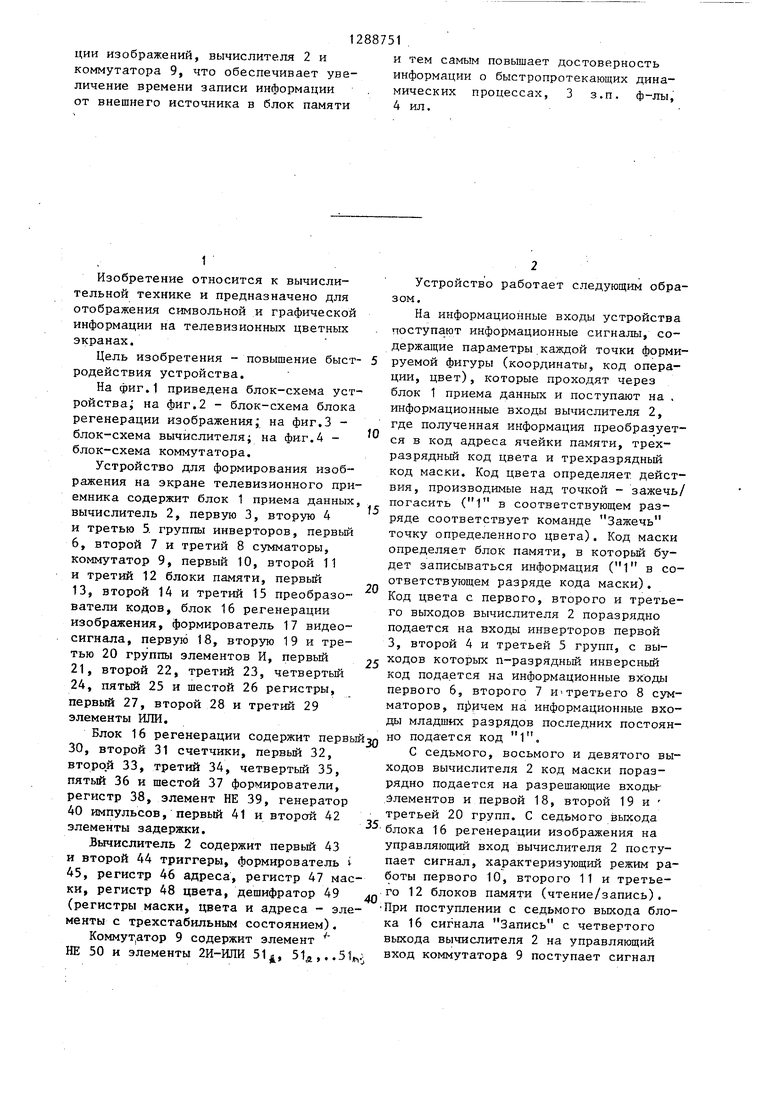

Блок 16 регенерации содержит первь 30, второй 31 счетчики, первьй 32, второй 33, третий 34, четвертьй 35, пятый 36 и шестой 37 формирователи, регистр 38, элемент НЕ 39, генератор 40 импульсов, первый 41 и второй 42 элементы задержки.

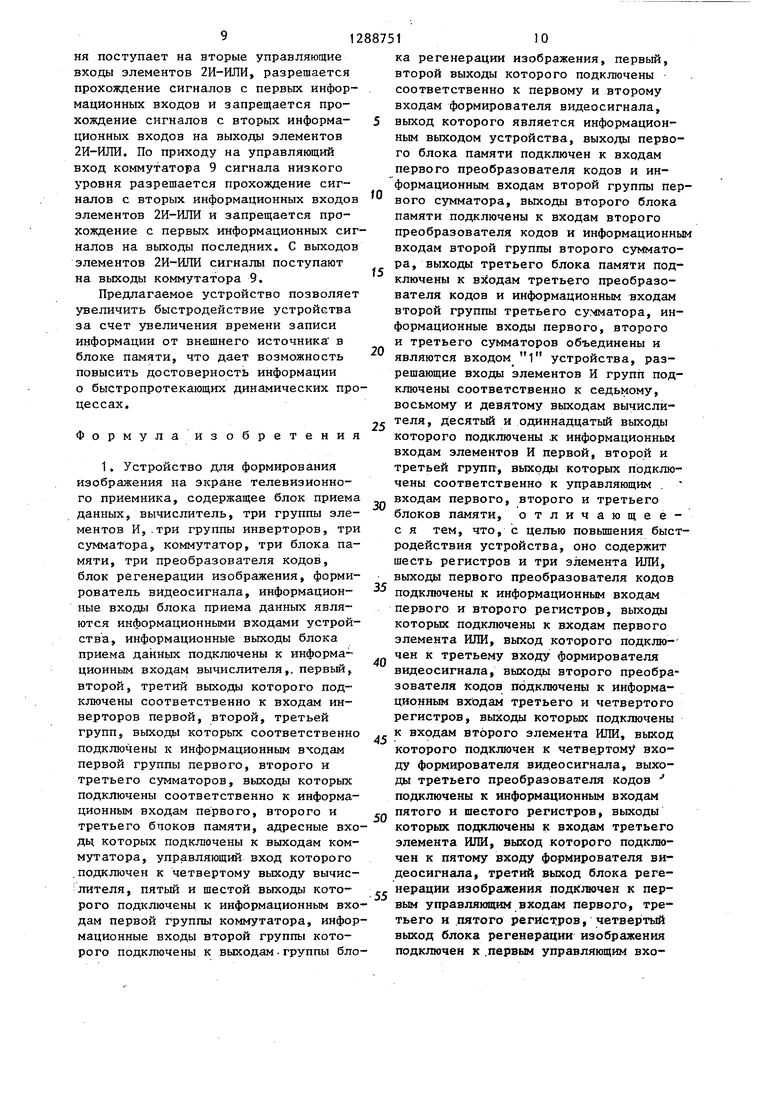

Вычислитель 2 содержит первьй 43 и второй 44 триггеры, формирователь i 45, регистр 46 адреса, регистр 47 маски, регистр 48 цвета, дешифратор 49 (регистры маски, цвета и адреса - элементы с трехстабильным состоянием).

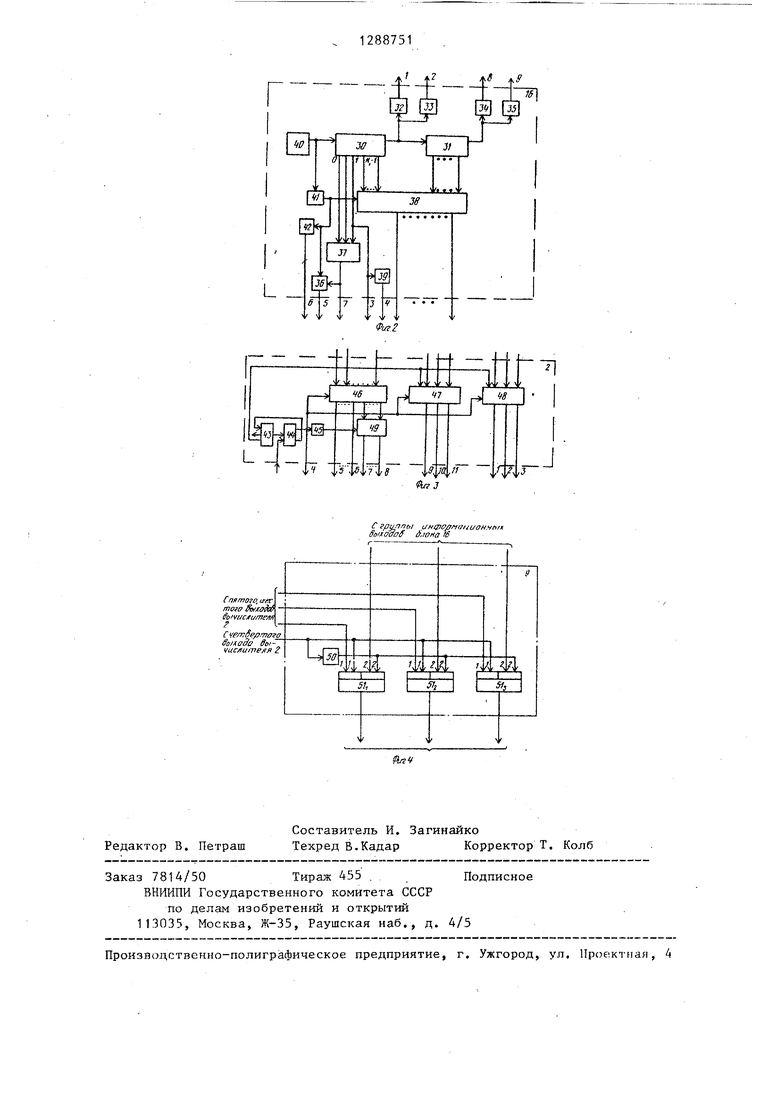

Коммут,атор 9 содержит элемент НЕ 50 и элементы 2И-ИЛИ 51, 51д,..51

и тем самым повьшает достоверность информации о быстропротекающих динамических процессах, 3 з.п. ф-лы, 4 ил.

f5

0

5

,,

Устройство работает следующим образом.

На информационные входы устройства поступают информационные сигналы, содержащие параметры каждой точки формируемой фигуры (координаты, код операции, цвет), которые проходят через блок 1 приема данных и поступают на , информационные входы вычислителя 2, где полученная информация преобразуется в код адреса ячейки памяти, трех- разрядньй код цвета и трехразрядньй код маски. Код цвета определяет действия, производимые над точкой - зажечь/ погасить (1 в соответствующем разряде соответствует команде Зажечь точку определенного цвета). Код маски определяет блок памяти, в которьй будет записываться информация (1 в соответствующем разряде кода маски). Код цвета с первого, второго и третьего выходов вычислителя 2 поразрядно подается на входы инверторов первой 3, второй 4 и третьей 5 групп, с выходов которых п-разрядный инверсньй код подается на информационные входы первого 6, второго 7 и-третьего 8 сумматоров, причем на информационные входы младших разрядов последних постоянно подается код 1,

С седьмого, восьмого и девятого выходов вычислителя 2 код маски поразрядно подается на разрешающие входы- Элементов и первой 18, второй 19 и третьей 20 групп. С седьмого выхода блока 16 регенерации изображения на управляющий вход вычислителя 2 поступает сигнал, характеризующий режим работы первого 10, второго 11 и третьего 12 блоков памяти (чтение/запись), При поступлении с седьмого выхода блока 16 сигнала Запись с четвертого выхода вычислителя 2 на управляющий вход коммутатора 9 поступает сигнал

высокого уровня, разрешающго прохождение через последний сигналов, определяющих код адреса m ячеек памяти первого 10, второго 11 и третьего 12

блоков памяти, поступающих с пятого и шестого выходов вычислителя 2 на информационные входы первой группы коммутатора 9, с выходов которого код адреса подается на адресные входы первого 10, второго 11 и третьего 12 блоков памяти, при этом на выходах каждого блока памяти устанавливаются п-разрядные коды, находящиеся в га заданных ячейках памяти.

С выходов первого блока 10 памяти сигналы поступают на информационные входы второй группы первого сумматора 6 и на входы первого преобразователя 13 кодов, с выходов которого преобразованный п-разрядный код подается на информационные входы первого 21 и второго 22 регистров, В первом сумматоре 6 коды с информационных входов обеих групп суммируются, и с

его выходов m суммарных п-разрядных кодов подается на информационные входы первого блока 10 памяти (если в первом- разряде кода цвета установлен (СОД Зажечь точку, то на выходах сумматора происходит наращивание кодов, содержащихся в m заданных ячейках памяти, на единицу, если в первом разряде кода, цвета установлен код Погасить точку, то на выходах сумматора происходит уменьшение кодов, содержащихся в га заданных ячейках памяти, на единицу).

С информационных выходов второго блока 11 памяти сигналы поступают на информационные входы второго сумматора 7 и на входы второго преобразователя 14 кодов, с выходов которого пре- образованньй п-разрядный код подается на информационные входы третьего 23 и четвертого 24 регистров. Во втором сумматоре 7 коды с информационных входов обеих групп суммируются и с его выходов m суммарных п-разрядных кодов подается на информационные входы второго блока 11 памяти.

С информационных выходов третьего блока 12 памяти сигналы поступают на информационные входы третьего сумматора 8 и на входы третьего преобразователя 15 кодов, с выходов которого преобразованный п-разрядный код по- дается на информационные входы пятого 25 и щестого 26 регистров. В третьем

fO

х

а 25

15

30

35

,Q 2887514

сумматоре 8 коды с информационных входов обеих групп суммируются.и с его выходов m суммарных п-разрядных кодов подается на информационные входы третьего блока 12 памяти.

По сигналу Запись с одиннадцатого и десятого выходов вычислителя 2 на информационные входы элементов И первой 18, второй 19 и третьей 20 групп поступают управляющие сигналы, и, если на их разрешающих входах имеются сигналы разрешения (соответствующие разряды кода маски равны 1), то уп)авляющие сигналы проходят через них и поступают соответственно на управляющие входы первого 10, второго 11 и третьего 12 блоков памяти, тем самым записывая в последние коды с ин- формационньк входов в одну из m ячеек памяти, адреса которых установлены на адресных входах первого 10, второго 11 и третьего 12 блоков памяти.

По окончании режима Запись с седьмого выхода блока 16 регенерации изображения на управляющий вход вычислителя поступает сигнал Чтение. По принятию этого сигнала с четвертого выхода вычислителя 2 на управляющий вход коммутатора 9 поступает сигнал низкого уровня, разрешающий прохождение через последний сигналов, определяющих код адреса m ячеек памяти первого 10, второго 11 и третьего 12 бло- ков памяти, поступающих с выходов.блока 16 на информационные входы второй группы коммутатора 9, с выходов которого код адреса подается на адресные входы первого 10, второго 11 и третьего 12 блоков памяти.

20

,Q 5

0

5

и десятый выходы вычислителя 2 блокируются, и на выходах элементов И первой 18, второй 19 и третьей 20 групп устанавливаются сигналы, соответст- вующие режиму Чтение, которые поступают на управляющие входы первого 10, второго 11 и третьего 12 блоков памяти, при этом одновременно из m ячеек памяти, адреса которых установлены на адресных входах всех трех блоков памяти, считываются имеющиеся там коды. С третьего и четвертого выходов блока 16 на первые управляющие входы первого 21, второго 22, третьего 23, пятого 25, второго 22, четвертого 24 и шастого 26 регистров поступают соответственно сигналы управления, определяющие режим работы этих регистров51288751

сдвиг/загрузка, причем если первый 21, третий 23 и пятый 25 регистры работают в режиме Сдвиг, то второй 22, четвертый 24 и шестой 26 регистры - в режиме Загрузка, и наоборот. 5

В случае, когда на первые управляющие входы первого 21, третьего 23 и пятого 25 регистров с третьего выхода блока 16 поступает сигнал управления Сдвиг, а на первые управляющие входы второго 22, четвертого 24 и шестого 26 регистров с четвертого выхода блока 16 - сигнал Загрузка, то при поступлении с пятого выхода

товые импульсы поступают на вход первого элемента 41 задержки и счетный вход первого счетчика 30, количество разрядов последнего связано с количеством точек в строке следующей зависимостью:г

,

где k, - количество разрядов первого счетчика 30. С информационных выходов первого счетчика 30 сигналы младших разрядов поступают на группу входов шестого формирователя 37, причем количество i X разрядов определяется

- I,- .. разрядностью первого 21, второго 22,

блока 16 на вторые управляющие входы л, Ас

третьего 23, четвертого /4, пятого /5

и шестого 26 регистров устройства (фиг,1) и равно

m 2 грузка коды с информационных входов

первого 21, второго 22, третьего 23,

четвертого 24, пятого 25 и шестого 26

регистров записываются во второй 22,

четвертьм 24 и шестой 26 регистры.

При поступлении с шестого выхода бло- 25 счетчика 30 также поступает прямо и

ка 16 на третьи управляющие входы пер- через злемент НЕ 39 -на третий и четпервого 21, второго 22, третьего 23, четвертого 24, пятого 25 и шестого 26 регистров стробирующих сигналов За20

где m - количество точек в строке;

i - количество младших разрядов первого счетчика 30, причем сигнал с i-ro разряда первого

вого 21, второго 22, третьего 23, четвертого 24, пятого 25 и шестого 26 регистров стробирующих сигналов Сдвиг информация, имеющаяся в первом 21, третьем 23 и пятом 25 регистрах, по- битно сдвигается и с их выходов сигналы поступают соответственно на входы первого 27, второго 28 и третьего 29 элементов ИЛИ, с выходов которых сигналы поступают соответственно на третий, четвертый и пятый входы формирователя 17 видеосигнала, на первый и второй входы которого с первого и второго выходов блока 16 регенерации изображения поступают управляющие сигналы - строчный гасящий .и кадровьй гасящий соответственно. На выходе формирователя 17 видеосигнала появляется видеосигнал, который поступает на информационный выход устройства.

С восьмого и девятого выходов блока 16 на первый и второй управляющие выходы устройства поступают соответственно сигналы строчной и кадровой синхронизации.

Блок 16 регенерации работает следующим образом.

Генератор 40 импульсов вырабатывает тактовые импульсы частотой

f

51,2 МКС

где г - количество точек в строке. С выхода генератора 40 импульсов тактовые импульсы поступают на вход первого элемента 41 задержки и счетный вход первого счетчика 30, количество разрядов последнего связано с количеством точек в строке следующей зависимостью:г

,

m 2

где m - количество точек в строке;

i - количество младших разрядов первого счетчика 30, причем сигнал с i-ro разряда первого

0

5

0

вертый выходы блока 16 соответственно.

Сигналы k -i разрядов с информационных выходов первого счетчика 30 поступают на одни информационные входы регистра 38, на другую группу информационных входов которого поступают сигналы с группы информационных выходов второго счетчика 31, разрядность которого определяется следующей зависимостью: Z 2

где Z - количество строк на экране; k - количество разрядов второго счетчика 30.

Задержанный на время Т тактовый импульс с выхода первого элемента 41 задержки поступает на входы второго

элемента 42 задержки, пятого формирователя 36 и на управляющий вход регистра 38, тем самым записывая последний код с его информационных входов. С выходов регистра 38 сигналы поступают на информационные выходы блока 16. С выхода второго элемента 42 задержки тактовый импульс поступает на шестой выход блока 16, На выходе шестого формирователя

37 формируется сигнал, определяющий соотношение длительности операций чтение/запись, который поступает на другой вход пятого формирователя 36 и на седьмой выход блока 16. Дли0

тельность операции Чтение. можно уменьшать до

t t, -t, t,,

где t, - минимальное время срабатывания блоков памяти устройства;

t, - минимальное время срабатывания преобразователей кода;

tj - минимальное время надежной записи информации в регистры (фиг.1)

При поступлении на вход пятого формирователя 36 тактового импульса с выхода первого элемента 41 задержки и сигнала Чтение с выхода шестого формирователя 37 на выходе формирователя 36 формируется сигнал, поступающий на пятый выход блока 16, При переполнении первого счетчика 30 на его выходе Переполнение появсчетный вход второго счетчика 31 и на входы первого 32 и второго 33 формирователей, на выходах которых формируются управляющие сигналы, соответственно поступающие на первый и второй выходы блока 16. При переполнении второго счетчика 31 на его выходе Переполнение появляется сигнал, которьш поступает на входы третьего 34 и четвертого 35 формирователей, на выходах которьрс формируются сигналы, соответственно поступающие на восьмой и девятый выходы блока.

Вычислитель 2 работает следующим образом.

По информационным входам вычислителя 2 на информационные входы регистра 46 адреса, регистра 47 маски и регистра 48 цвета поразрядно подается

1-разрядный код. Одновременно на син

хровход первого триггера 43 входы регистра 46 адреса, регистра 47 маски и регистра 48 цвета по первому информационному входу поступает синхросигнал, тем самым записьгоая в регистр 46 адреса, регистра 47 маски и регистра 48 цвета имеющиеся на их информационных входах коды и устанавливая первый триггер 43 в единичное состояние (на информационный вход первого триггера 43 постоянно подается сигнал высокого уровня).

Выход первого триггера 43 подключен к информационному входу второго триггера 44. При поступлении по управляющему входу вычислителя 2 сигнала Запись на синхровход второго триггера 44 последний устанавливается в единичное состояние, и с его выхода

W

15

0

25

30

35

0

0

5

сигнал высокого уровня поступает на четвертый выход вычислителя 2, на вход формирователя 45 и управляющие входы регистра 46 адреса, регистра 47 маски и регистра 48 цвета, тем самым разрешая Бьщачу на информационные выходы последних хранящихся там кодов.

С выхода регистра 48 цвета код цвета поразрядно подается на первый, второй и третий выходы вычислителя 2. С группы информащюнньпс выходов регистра 47 маски код маски поразрядно подается на девятый, восьмой и седьмой выходы вычислителя 2.

С информационных выходов одной группы регистра 46 адреса код адреса подается на пятый и шестой выходы вычислителя 2, с информационных выходов другой группы регистра 46 адреса - на входы дешифратора 49. С выхода формирователя 45 на управляющий вход дешифратора 49 поступает сигнал управления, разрешающий работу последнего, при этом на выходах дешифратора 49 появляется код, который подается на одиннадцатый и десятый выходы вычислителя 2. С инверсного выхода второго триггера 44 сигнал низкого уровня поступает на вход Сброс первого триггера 43, устанавливая тем самым последний в нулевое состояние.

При поступлении по управляющему входу вычислителя 2 сигнала Чтение на синхровход второго триггера 44, последний устанавливается в нулевое состояние, так как на его информа- ционньш вход с выхода первого триггера 43 поступает сигнал низкого уровня. С выхода второго триггера 44 сигнал низкого уровня проходит через формирователь 45 и поступает на управляюп1ий вход дешифратора 49, запрещая тем самым его работу.

Коммутатор 9 работает следующим образом.

По информационньм входам первой группы коммутатора 9 информационные сигналы поступают на первые информационные входы элементов 2И-ИЛИ 51,./, 51 ,...,51, по информационным входам второй группы коммутатора 9 - на вторые информационные входы элементов 2И-ИЛИ. По приходу на управляющий вход коммутатора 9 сигнала высокого уровня, который поступает на первые управляющие входы элементов 2И-Ш1И и на вход элемента НЕ 50, с выхода которого сигнал низкого уровня поступает на вторые управляющие входа элементов 2И-ЙЛИ, разрешается прохождение сигналов с первых информационных входов и запрещается прохождение сигналов с вторых информационных входов на выходы элементов 2И-ИЛИ. По приходу на управляющий вход коммутатора 9 сигнала низкого уровня разрешается прохождение сигналов с вторых информационных входов элементов 2И-ИЛИ и запрещается прохождение с первых информационных сигналов на выходы последних. С выходов элементов 2И-ИЛИ сигналы поступают на выходы коммутатора 9.

Предлагаемое устройство позволяет увеличить быстродействие устройства за счет увеличения времени записи информации от внешнего источника в блоке памяти, что дает возможность повысить достоверность информации о быстропротекающих динамических процессах.

Формулаизобретения

1. Устройство для формирования изображения на экране телевизионного приемника, содержащее блок приема данных, вычислитель, три группы элементов И,.три группы инверторов, три сумматора, коммутатор, три блока памяти, три преобразователя кодов, блок регенерации изображения, формирователь видеосигнала, информационные входы блока приема данных являются информационными входами устройства, информационные выходы блока приема данных подключены к информационным входам вычислителя,, первьй, второй, третий выходы которого подключены соответственно к входам инверторов первой, второй, третьей

fO

15

20

ка регенерации изображения, первый, второй выходы которого подключены соответственно к первому и второму входам формирователя видеосигнала, выход которого является информационным выходом устройства, выходы перво го блока памяти подключен к входам первого преобразователя кодов и информационным входам второй группы пе вого сумматора, выходы второго блока памяти подключены к входам второго преобразователя кодов и информационн входам второй группы второго суммато ра, выходы третьего блока памяти под ключены к входам третьего преобразователя кодов и информационным входам второй группы третьего сумматора, ин формационные входы первого, второго и третьего сумматоров объединены и являются входом 1 устройства, раз30

решающие входы элементов И групп под ключены соответственно к седьмому, восьмому и девятому выходам вычисли- -е теля, десятый и одиннадцатьй выходы которого подключены к информационным входам элементов И первой, второй и третьей групп, выхода которых подключены соответственно к управляющим . входам первого, второго и третьего блоков памяти, отличающее- с я тем, что, с целью повьшения быс родействия устройства, оно содержит шесть регистров и три элемента ИЛИ, выхода первого преобразователя кодов подключены к информационным входам первого и второго регистров, выходы которых подключены к входам первого элемента ИЛИ, выход которого подключен к третьему входу формирователя видеосигнала, выходы второго преобразователя кодов подключены к информационным входам третьего и четвертого регистров, выходы которых подключены

35

40

групп, выхода которых соответственно ., к входам второго элемента ИЛИ, выход

подключены к информационным входам первой группы первого, второго и третьего сумматоров, выходы которых: подключены соответственно к информационным входам первого, второго и третьего б тюков памяти, адресные вхо- дц которых подключены к выходам коммутатора, управляющий вход которого .подключен к четвертому выходу вычис- лителя, и шестой выхода которого подключены к информационным входам первой группь коммутатора, информационные входы второй группы которого подключены к выходам - группы бло50

55

которого подключен к четвертому входу формирователя видеосигнала, выхода третьего преобразователя кодов подключены к информационным входам пятого и шестого регистров, выходы которых подключены к входам третьего элемента ИЛИ, выход которого подключен к пятому входу формирователя видеосигнала, третий выход блока регенерации изображения подКгаочен к первым управляющим входам первого, третьего и пятого регистров, четвертый выход блока регенерации изображения подключен к .первым управляющим вхо

ка регенерации изображения, первый, второй выходы которого подключены соответственно к первому и второму входам формирователя видеосигнала, выход которого является информационным выходом устройства, выходы первого блока памяти подключен к входам первого преобразователя кодов и информационным входам второй группы первого сумматора, выходы второго блока памяти подключены к входам второго преобразователя кодов и информационным входам второй группы второго сумматора, выходы третьего блока памяти подключены к входам третьего преобразователя кодов и информационным входам второй группы третьего сумматора, информационные входы первого, второго и третьего сумматоров объединены и являются входом 1 устройства, раз0

решающие входы элементов И групп подключены соответственно к седьмому, восьмому и девятому выходам вычисли- е теля, десятый и одиннадцатьй выходы которого подключены к информационным входам элементов И первой, второй и третьей групп, выхода которых подключены соответственно к управляющим . входам первого, второго и третьего блоков памяти, отличающее- с я тем, что, с целью повьшения быстродействия устройства, оно содержит шесть регистров и три элемента ИЛИ, выхода первого преобразователя кодов подключены к информационным входам первого и второго регистров, выходы которых подключены к входам первого элемента ИЛИ, выход которого подклю чен к третьему входу формирователя видеосигнала, выходы второго преобразователя кодов подключены к информационным входам третьего и четвертого регистров, выходы которых подключены

5

0

0

5

которого подключен к четвертому входу формирователя видеосигнала, выхода третьего преобразователя кодов подключены к информационным входам пятого и шестого регистров, выходы которых подключены к входам третьего элемента ИЛИ, выход которого подключен к пятому входу формирователя видеосигнала, третий выход блока регенерации изображения подКгаочен к первым управляющим входам первого, третьего и пятого регистров, четвертый выход блока регенерации изображения подключен к .первым управляющим вхоП1288751

дам второго, четвертого и шестого регистров, вторые и третьи управляющие входы всех регистров подключены соответственно к пятому и шестому выходам блока регенерации изображения, седьмой выход которого соединен с управляющим входом вычислителя, а восьмой и девятый выходы являются управляющими выходами устройства.

2, Устройство по П.1, отличающееся тем, что блок регенерации изображения содержит генератор импульсов, первый и второй счетчики, первый, второй, третий, четвертьй, пятьй и шестой формирователи, первый и второй элементы задержки, регистр и элемент НЕ, выход генератора импульсов подключен к счетному входу первого.счетчика и входу первого элемента задержки, выход которого подключен к входу второго элемента задержки, первому входу пятого формирователя и синхровходу регистра,, информационные входы которого подключены к выходам второго счетчика, к одним из выходов первого счетчика, другие выходы которого подключены к входам шестого формирователя, причем один из выходов других выходов первого счетчика является третьим выходом блока и подключен к входу элемента НЕ, выход которого является четвертым выходом блока, выходами группы которого являются выходы регистра, счетный вход второго счетчика подключен к выходу Переполнение первого счетчика, соединенному с входами первого и второго формирователей, выходы которых являются соответственно первым-и вторым выходами блока, восьмым и девятым выходами которого являются соответственно выходы третьего и четвертого формирователей, входы которых подключены

10

}5

20

25

30

40

тель содержит регистр адресу, регистр маски, регистр цвета, первый и второй триггеры, формирователь, дешифратор, информационные входы регистров адреса маски и цвета являются информационными входами вычислителя, а синхровходы их подключены к синхровходу первого триггера, выход которого подключен к информационному входу второго триггера, .синхровход которого является управляющим входом вычислителя, четвертым выходом которого является прямой выход второго триггера, подключен ный к входу формирователя и управляющим входам регистров адреса, маски и цвета, выходы регистра цвета являются первым, вторым и третьим выходами вычислителя, девятым, восьмым и седьмым выходами которого являются соответствующие выходы регистра маски, вы ходы одной из групп регистра адреса являются пятым и шестым выходами вычислителя, одиннадцатым и десятым выходами которого являются выходы дешифратора, входы которого подключены к выходам другой группы регистра адре са, выход формирователя подключен к управляющему входу дешифратора, инверсный выход второго триггера ,под- 35 ключей к входу Сброс первого тригге ра.

4. Устройство по П.1, отлича ющееся тем, что коммутатор со- держит элемент НЕ и элементы 2И-ИЛИ, информационные входы первой и второй групп элементов 2И-ИЛИ являются соответственно информационными входами первой и второй групп коммутатора, уп равляющим входом которого являются

к выходу Переполнение второго счет- вход элемента НЕ и первые управляющие

чика, выход второго элемента задержки является шестьм выходом блока,, пятым выходом которого является выход пятого формирователя, еторой вход

1

12

которого подключен к вьпсоду шестого формирователя, которьй является седьмым выходом блока.

3, Устройство по П.1, отличающееся тем, что вычисли0

5

0

5

0

0

тель содержит регистр адресу, регистр маски, регистр цвета, первый и второй триггеры, формирователь, дешифратор, информационные входы регистров адреса, маски и цвета являются информационными входами вычислителя, а синхровходы их подключены к синхровходу первого триггера, выход которого подключен к информационному входу второго триггера, .синхровход которого является управляющим входом вычислителя, четвертым выходом которого является прямой выход второго триггера, подключенный к входу формирователя и управляющим входам регистров адреса, маски и цвета, выходы регистра цвета являются первым, вторым и третьим выходами , вычислителя, девятым, восьмым и седьмым выходами которого являются соответствующие выходы регистра маски, выходы одной из групп регистра адреса являются пятым и шестым выходами вычислителя, одиннадцатым и десятым выходами которого являются выходы дешифратора, входы которого подключены к выходам другой группы регистра адреса, выход формирователя подключен к управляющему входу дешифратора, инверсный выход второго триггера ,под- 5 ключей к входу Сброс первого триггера.

4. Устройство по П.1, отличающееся тем, что коммутатор со- держит элемент НЕ и элементы 2И-ИЛИ, информационные входы первой и второй групп элементов 2И-ИЛИ являются соответственно информационными входами первой и второй групп коммутатора, управляющим входом которого являются

входы элементов 2И-ИЛИ, вторые управляющие входы которых подключены к выходу элемента НЕ, выходы элементов 2И-ИЛИ являются выходами коммутатора.

h-

I I

JL

r

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для сопряжения процессораС уСТРОйСТВАМи ВВОдА-ВыВОдА | 1979 |

|

SU845155A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Редактор В. Петраш

Составитель И. Загинайко

Техред В.Кадар Корректор Т. Колб

Заказ 7814/50 Тираж 455 . . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Пронзнодственио-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

t nntti uн lJe7Jffм(. Soixaasf б.юха t6

С fpyrt Soi oaoi

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1010613A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования изображений на экране телевизионного приемника | 1982 |

|

SU1072092A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-02-07—Публикация

1985-09-03—Подача