шифратора, выходы с первого по чет- мяти таблиц, с управляющими входами вертый которого соединены соответ- первого второго коммутаторов и вто- ственно с вторым входом узла памяти рым входом разрешения приема рабочетаблицы третьего операнда блока па- го регистра,

1176326

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее блок памяти таблиц и два дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей за счет вьшолнения преобразования кода из позиционной системы счисления в систе- . му остаточных классов и обратно, оно содержит два коммутатора, два сумматора, схему сравнения с нулем, два блока элементов запрета, блок памяти таблицы результата, рабочий регистр, а блок памяти таблиц содержит узлы памяти таблиц отрицательного произведения, положительного произведения, третьего операнда, старших констант и младших констант, причем входы первого и второго операндов устройства соединены с соответствующими входами первого сумматора и схемы сравнения с нулем, выход первого сумматора соединен с вхо-. дами узлов памяти таблиц отрицательного произведения и положительного произведения блока памяти таблиц, вы/ И 4 Jш ход схемы сравнения с нулем соединен с управляющими входами первого и второго блоков элементов запрета, информационные входы которых соединены соответственно с выходами узлов памяти отрицательного и положительного произведений блока памяти таблиц, входы третьего операнда и общих данных устройства соединены соответственно с первым входом узла памяти таблицы третьего операнда и входом узла памяти таблицы младпих констант блока памяти таблиц, выходы которых соединены соответственно с первым и вторым информационными входами первого(Л коммутатора, третий информационный вход которого соединен с выходом рабочего регистра и входом обпщх данных устройства, вход общего адреса которого соединен с входом узла памяти таблицы старших констант блока памяти таблиц и входом первого дешифратора, выходы которых соединены д : соответственно с первым информаОд ционным входом второго коммутатора 00 и с первым входом разрешения приема рабочего регистра, второй информационный и информационный входы которых соединены с выходом первого блока элементов запрета, выхрд второго блока элементов запрета соединен с третьим информационным входом второго коммутатора, выходы первого и второго коммутаторов соединены с соответствующими входами второ- гр сумматора, выход которого соединен через блок памяти таблицы результата с выходом результата устройства, вход кода операции устрой -. ства соединен с входом второго де

I

Изобретение относится к вычислительной технике и предназначено для работы в вычислительных устройствах работающих в непозиционной системе счисления (остаточных классах), с использованием индексного и вычетного представления кодов операндов.

Целью изобретения является расширенное функциональных возможностей за счет вьшолнения преобразования кода из позиционной системы счисления в систему остаточных классов и обратно.

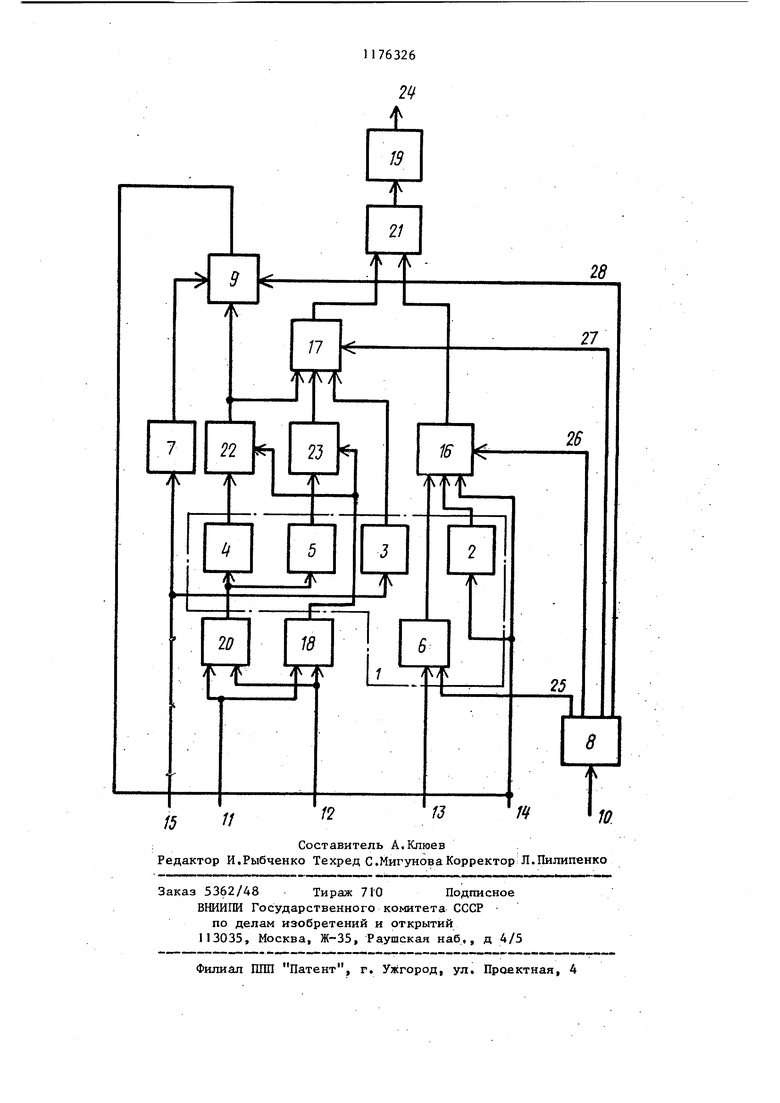

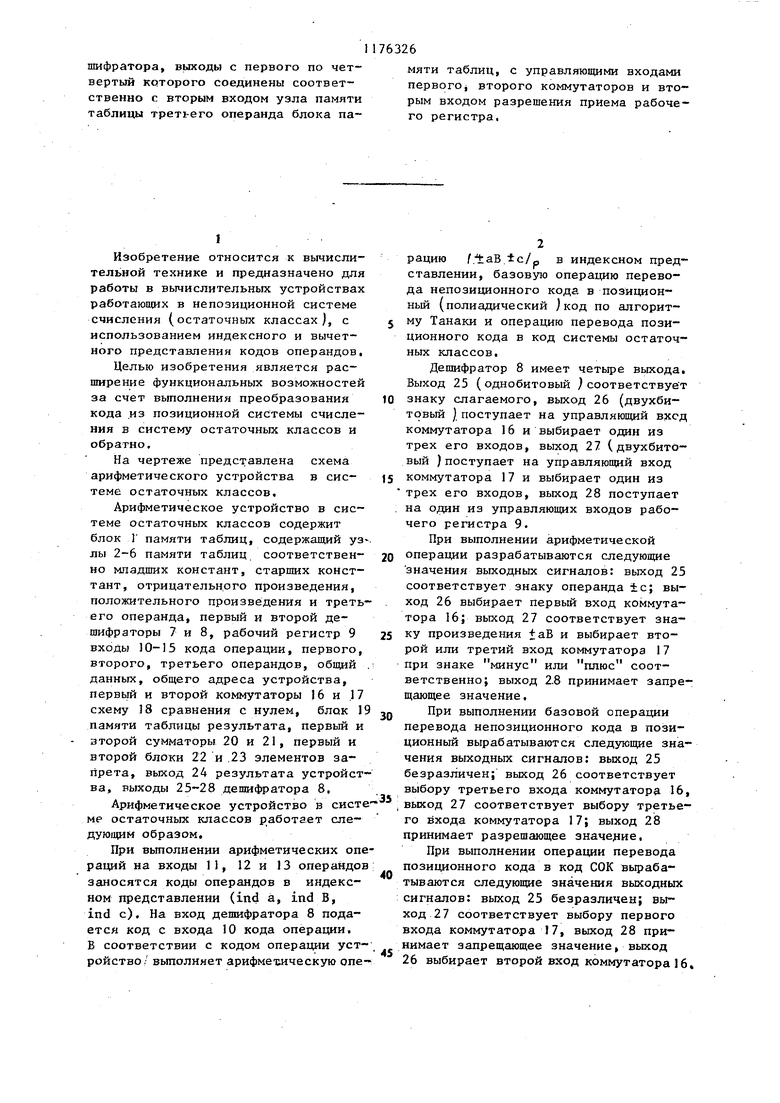

На чертеже представлена схема арифметического устройства в системе остаточных классов.

Арифметическое устройство в системе остаточных классов содержит блок 1 памяти таблиц, содержащий yз лы 2-6 памяти таблиц, соответственно младших констант, старших консттант, отрицательного произведения, положительного произведения и треть его операнда, первый и второй дешифраторы 7 и 8, рабочий регистр 9 входы 10-15 кода операции, первого, второго, третьего операндов, общий данных, общего адреса устройства, первь1й и второй коммутаторы 16 и .17 схему 18 сравнения с нулем, блок J9 памяти таблицы результата, первый и зторой сумматоры 20 и 21, первый и второй блоки 22 и .23 элементов запрета, выход 24 результата устройст ва, выходы 25-28 дешифратора 8,

Арифметическое устройство в сясте ме остаточных классов работает следующим образом.

При вьтолнении арифметических операций на входы 11, 12 и 13 операндов заносятся коды операндов в индексном представлении (ind а, ind В, ind с). На вход дешифратора 8 подается код с входа 10 кода операции. В соответствии с кодом операции устройство/ выполняет арифметическую операцию Г±аВ.с/р в индексном представлении, базовую операцию перевода непозиционного кода в позиционный (полиадический jкод по алгорит- 5 му Танаки и операцию перевода позиционного кода в код системы остаточных классов.

Дешифратор 8 имеет четыре выхода. Выход 25 (однобитовый )соответствует

0 знаку слагаемого, выход 26 (двухбитовый )поступает на управляющий вход коммутатора 16 и выбирает один из трех его входов, выход 27 (двухбитовый )поступает на управляющий вход

5 коммутатора 17 и выбирает один из трех его входов, выход 28 поступает : на один из управляющих входов рабочего регистра 9.

При выполнении арифметической

0 операции разрабатываются следующие значения выходных сигналов: выход 25 соответствует знаку операнда ±с; выход 26 выбирает первый вход коммутатора 16; выход 27 соответствует знаку произведения аВ и выбирает второй или третий вход коммутатора 17 при знаке минус или плюс соответственно; выход 2.8 принимает запрещающее значение,

„ При выполнении базовой операции перевода непозиционного кода в позиционный вырабатываются следующие значения выходных сигналов: выход 25 безразличен; выход 26 соответствует выбору третьего входа коммутатора 16, , выход 27 соответствует выбору третьего входа коммутатора 17; выход 28 принимает разрешающее значение.

При выполнении операции перевода позиционного кода в код СОК вырабатываются следующие значения выходных сигналов: выход 25 безразличен; выход 27 соответствует выбору первого входа коммутатора 17, выход 28 принимает запрещающее значение, выход

26 выбирает второй вход коммутатора 16. Известно, что операция умножения двух чисел по mod р, где р - простое число, изоморфна операции сложения индексов этих чисел по mod(pпоэтому произведение операндов а и В выполняется суммированием ind а ind В на сумматоре 20. Полученная сумма перекодируется с помощью узлов памяти таблиц положительного произведения 5 и отрицательного про изведения 4 в коды вычетов /+аВ/р и |-аВ|р соответственно. Таблицы реализуют преобразование tf(q(inda find В)где q:ind а + ind В- -(ind a+ind В).р, ; f :ind о - /о6/рПри чемИ|р (р /оС|р/. Таблица положительного произведения для имеет вид Входы О Выходы 1 Таблица отрицательного произведения для имеет вид Входы Выходы С входа 13 операнда с код поступает на вход узла 6 памяти таблицы операнда, которая реализует преобразование tf(ind с) в зависимости от значения сигнала с дешифратора 8. С выхода узла 6 па51яти таблицы операнда код tf(ind с) поступает на первый вход коммутатора 16. В случае арифметической операции управляющий сигнал с выхода дешифратора 8, подаваемый на управляющий вход коммутатора 16, выбирает пер вый вход, тогда вычет if(ind с) подается на вход сумматора 2J . Код . операнда с выхода узла 5 памяти таб лицы положительного произведения че .рез блок ,23 элементов запрета посту пает на третий вход коммутатора 17, Код операнда с выхода узла 4 памяти таблицы отрицательного произведения через блок 22 элементов запрета под ется на второй вход коммутатора 17 и в:ход рабочего регистра,9. Блоки 22 и 23 пропускают входной код для изменения или обнуляют его в зависи мости от сигнала на управляющем вхо де, который подается со схемы 18 сравнения с нулем. Схема 18 сравне ния с нулем вьщает сигнал, если хо тя бы один из операндов ind а или 264 ind В является символом, соответствующим нулю в вычетном представлении. С вьпсода коммутатора 17 в зависимости от сигнала с дешифратора 8 вычет +f(q(ind а + ind В) или -f (q(ind а + ind B)j подается на вход сумматора 21. Код результата суммирования подается на вход блока 19 памяти таблицы результата, который реализует преобразование I(m(x)). где X - код на входе блока 19 памяти таблицы результата; m:x-r(xL; Е if-x 1р- ind X. i Таблица результата для имеет С выхода блока 19 код индекса результата операции поступает на выход 24 устройства. Перевод непозиционного кода в позиционный по алгоритму Танаки выполняется реку1 рентно с помощью базовой операции перевода C«i}4o Cm} -H. . Начальным значением рекуррентной переменной cil является непоэиционный код, который необходимо преобразовать в позиционный ....:,Hp.J, где ftn)- - модулярные константы пре образования и; f I., |-(1рГ при Uv-ni при j«0 , |:pj определяется соотношеием , причем Р k-1 модули СОК; k -колиеЪтво модулей и число этапов реурсии, .Mj. {rj,-,-.r,}. -. ; ( 1; IP.-,IPjlPi - результат де у. fW/p. (р,-|р реобразования на j-м этапе рекурии; (; loi I р. - значение вычета по моулю р- рекуррентной переменной f е(1 а J-M этапе рекурсии. Результатом перевода является олиадический код у, А-г Для выполнения базово.й операции а один такт используется вход 14 бщих данных, объединяющий модулярые секции по модулям р-. При выполнении базовой операции еревода на входы 11 и 12 операндов подаются переменная и константа fгаj ;на вход 15 общего адреса подается адрес модулярной секции j, соответствующий номеру этапа рекурсии. Разрешающий сигнал с выхода дешифратора 8 подается на управляющий вход рабочего регистра 9, на другой управляющий вход которого по дается сигнал с выхода дешифратора 7, При наличие двух разрешающих сиг налов на управлякицих входах рабочего регистра 9 код отрицательного .пр изведения с выхода узла 4 памяти та лицы отрицательного произведения че рез регистр 9 передается на вход 14 общих данных.Одновременно Управляющий сигнал с выхода дешифратора 8 . выбирает третий вход коммутатора 16 и передает код с входа 14 общих дан ных на второй вход сумматора 2,:. Уп равляквций сигнал с выхода дешифратора 9 выбирает третий вход коммутатора 17, и код с выхода узла 5 памяти таблицы положительного произведения поступает на первый вход сумматора 21, Результат выполнения базовой операции на j-м рекурсии состоит из промежуточного значения рекуррентной переменной {о которое получается на выходе 24 результата, и j-й компоненты полиадического кода с отрицательным знаком на входе 14 общих данных. Для выполнения перевода непозиционного кода в позиционный по алгоритму Танаки в СОК с модулями Рр Р- . необходимо k предлагаемых устройств, объединенных входом общих данных и входом общего адреса. Алгоритм Танаки выполняется с помощью k-рекуррентных базовы операций. Перевод позиционного кода В в непозиционный код {Mj выполняется суммированием .модулярных констант, .соответствующих младшему байту и старшему байту позиционного кода. Если Вг и В„ - младший и старший байты позиционного кода соответственно, то соответствующие модулярные константы Мц.и М. по модулю р. определяются следующими соотношениями: J где ф В, - двухбайный позиционный код, у которого старший байт является нулевым, а младший равен B(j 0 - двухбайтный позиционный код, у которой старший байт равен В, а младший байт является нулевым. Тогда выполняется соответствие В В„ 95 +9SB «{М) , где Mj. iMHj. + . При выполнении операции перевода на вход 14 общих данных и вход 15 общего адреса подаются коды В i и Вд соответственно, .С входов 14 и 15 коды Вц и Вц поступают на входы узлов 2 и 3 памяти таблиц младших констант и старших констант. Управляющие сигналы с выхода дешифратора 8 выбирают соответствующие входы коммутато1за 16 и коммутатора 1,7, так что соответствующие модулярные константы Мц и MK; с выхода поступают на сумматор 2I, на котором выполняется операция перевода. Результат операции поступает на выход 24 результата устройства.

/7

ш

hi

2

2J

у г

ГТ

28

27

26

w

| Арифметическое устройство в системе остаточных классов | 1973 |

|

SU549805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ приготовления из сои корма для шелковичных червей | 1932 |

|

SU41989A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-30—Публикация

1984-03-27—Подача