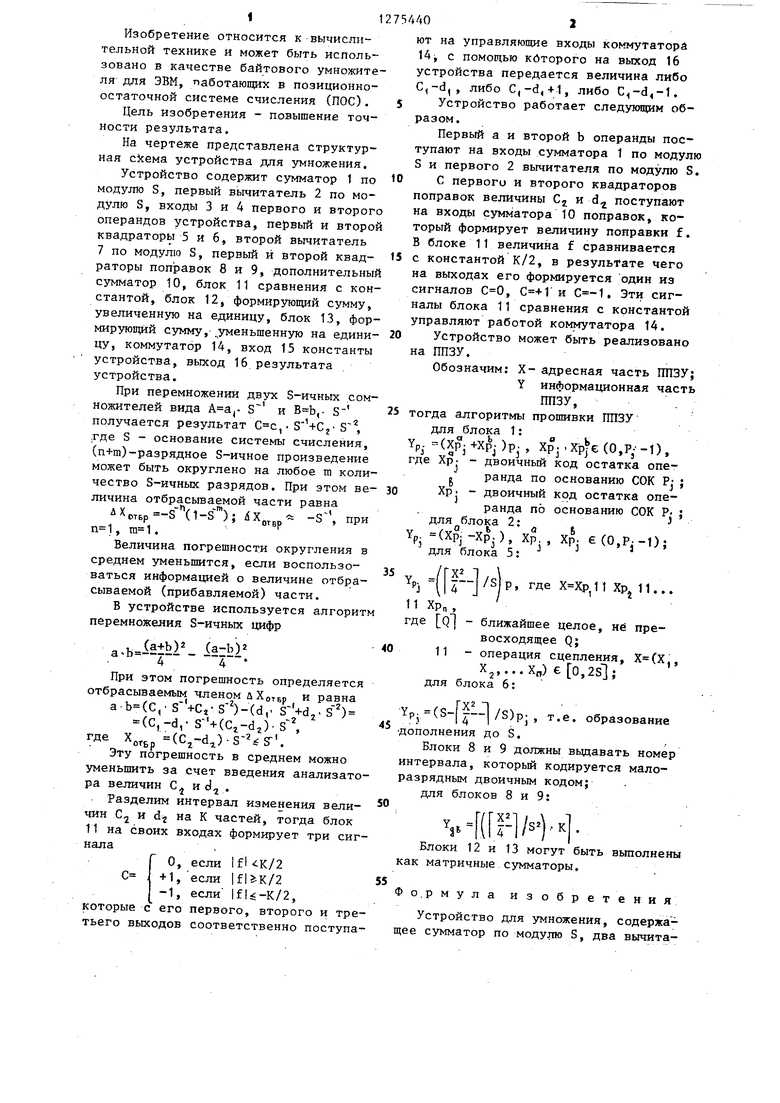

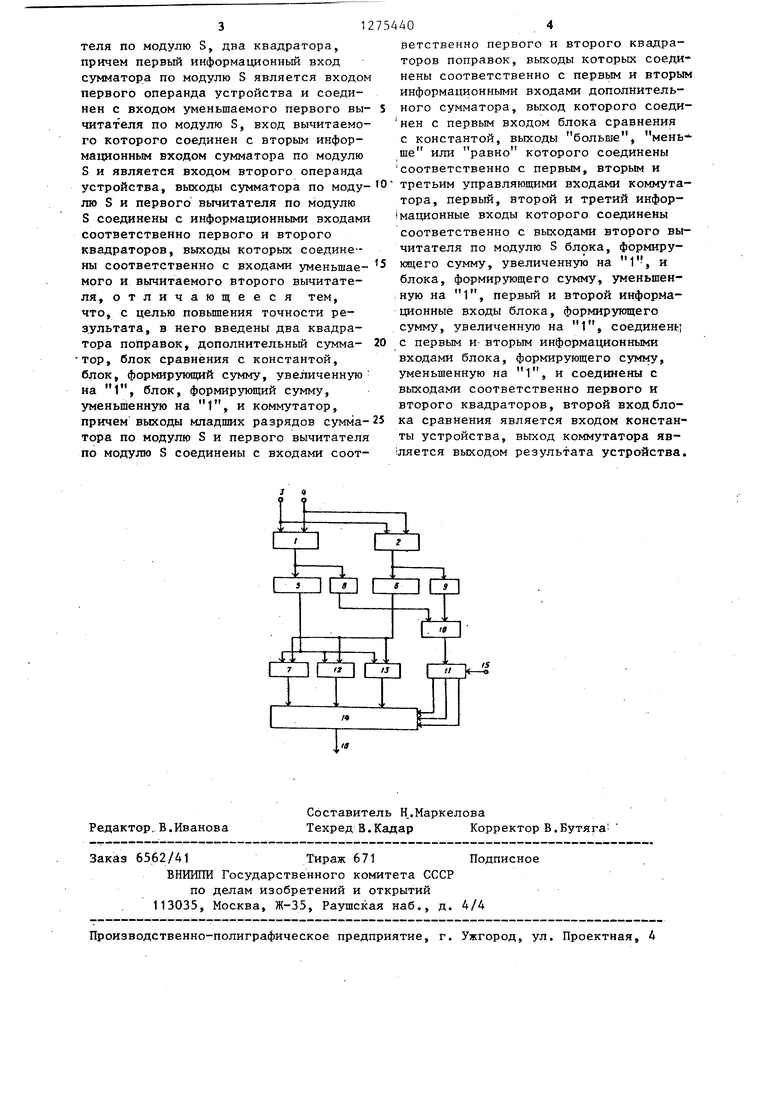

Изобретение относится к вычислительной технике и может быть использовано в качестве байтового умножителя для ЭВМ, работающих в позиционноостаточной системе счисления (ПОС). Цель изобретения - повышение точности результата. На чертеже представлена структурная с}сема устройства для зт ножения. Устройство содержит сумматор 1 по модулю S, первый вычитатель 2 по модулю S, входы 3 и 4 первого и второго операндов устройства, первьй и второй квадраторы 5 и 6, второй вычитатель 7 по модулю S, первый и второй квадраторы поправок 8 и 9, дополнительный сумматор 10, блок 11 сравнения с константой, блок 12, формирзтощий сумму, увеличенную на единицу, блок 13, формирующий сумму, .уменьшенную на единицу, коммутатор 14, вход 15 константы устройства, выход 16 результата устройства. При перемножении двух S-ичньгх сомножителей вида и ,- получается результат ,- S, где S - основание системы счисления, (п+т)-разрядное S-ичное произведение может быть округлено на любое m коли чество S-ичных разрядов. При этом ве личина отбрасьгааемой части равна лХ,,, (1-8 ); , . Величина погрешности округления в среднем уменьшится, если воспользоваться информацией о величине отбрасываемой (прибавляемой) части. В устройстве используется алгорит перемножения S-ичных цифр а.) (а-Ь) При этом погрешность определяется отбрасываемым членом л Хотвр и равна а-Ь(С,S+Cj-S)-(d,. S+dj.s (С,-d,- S +CCj-dj)- S х„,р (c,-dj-s- . Эту погрешность в среднем можно уменьшить за счет введения анализато ра величин С и d . Разделим интервал изменения величин С и dj на К частей, тогда блок 11 на своих входах формирует три сиг нала , О, если Ifl К/2 -И, если -1, если |fU-K/2, которые с его первого, второго и тре тьего выходов соответственно поступа ют на управляющие входы коммутаторй 14j с помощью которого на выход 16 устройства передается величина либо C,-d, , либо C,-d,-1, либо ,-1. Устройство работает следующим образом. Первый а и второй b операнды поступают на входы сумматора 1 по модулю S и первого 2 вычитателя по модулю S. С первого и второго квадраторов поправок величины С- и d- поступают на входы сумматора 10 поправок, который формирует величину поправки f. В блоке 11 величина f сравнивается с константой К/2, в результате чего на выходах его формируется один из сигналов , и , Эти сигналы блока 11 сравнения с константой управляют работой коммутатора 14. Устройство может быть реализовано на ППЗУ. Обозначим: Х- адресная часть ШТЗУ; Y информационная часть ППЗУ, тогда алгоритмы прошивки ППЗУ для блока 1: Yp. -(хр. +хр )р. , xpj. (О,р. -1), где Хр; - двоичный код остатка операнда по основанию СОК Р Хр; - ДВОИЧНЫЙ КОД оствткв операнда по основанию СОК Р для блока 2: у„. (xpj ), Хр xpj е (о,р. -1); для блока 5: где ,11 Xpj 11... 11 Хр„ , где - ближайшее целое, не превосходящее Q; 11 - операция сцепления, ,, Х2,...Х„) ,2sl; для блока 6: Yp-(S-ff-- /S)pj, т.е. образование дополнения до S. Блоки 8 и 9 должны вьщавать номер интервала, который кодируется малоразрядным двоичным кодом; для блоков 8 и 9: v(-lH-lБлоки 12 и 13 могут быть выполнены как матричные сумматоры. Фо.рмула изобретения Устройство для умножения, содержащее сумматор по МОДУЛЮ S, два вычитателя по модулю S, два квадратора, причем первый информационный вход сумматора по модулю S является входом первого операнда устройства и соедннен с входом уменьшаемого первого вычитателя по модулю S, вход вычитаемого которого соединен с вторым информационным входом сумматора по модулю S и является входом второго операнда ь и является входом ь.ир. и V. устройства, вькоды сумматора по модулю S и первого вычитателя по модулю S соединены с информационными входами соответственно первого и второго квадраторов, выходы которых соединеквадраторов, выходы которых соедине , ,4 ны соответственно с входами уменьшаемого и вычитаемого второго вычитателя, отличающееся тем, что, с целью повьшения точности результата, в него введены два квадратора поправок, дополнительньм сумматор, блок сравнения с константой, блок, формирующий сумму, увеличенную на 1, блок, формирующий сумму, уменьшенную на 1, и коммутатор, причем выходы младщих разрядов сумматора по модулю S и первого вычитателя по модулю S соединены с входами соот12О. 4 ветственно первого и второго квадраторов поправок, выходы которых соединены соответственно с первым и вторым информационными входами дополнительного сумматора, выход которого соединен с первым входом блока сравнения с константой, выходы больше, меньше или равно которого соединены соответственно с первым, вторым и третьим управляющими входами коммутатреть м у р тора, первый, второй и третий информационные входы которого соединены соответственно с выходами второго вычитателя по модулю S блока, формиру-,.-- - --. . - „ „ «1 II кжего СУММУ, увеличенную на i , клцего сумму, увс „1,., vw Hbtne блока, формирующего сумму, уменьщен«T T fa 4innvtMnvinmprn СУММУ, уменьше ную на 1, первый и второй информационные входы блока, формирующего сумму, увеличенную на 1, соединен с первым и вторым информационными входами блока, формирующего сумму, уменьшенную на 1, и соединены с выходами соответственно первого и второго квадраторов, второй вход блока сравнения является входом константы устройства, выход коммутатора яв ляется выходом результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Преобразователь форматов чисел | 1987 |

|

SU1543550A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве байтового умножителя для ЭВМ, работаюпщх в позиционноостаточной система счисления (ПОС) Цель изобретения - расширение функци-; ональных возможностей за счет формирования устройством округленного произведения. Устройство содержит сумматор по модулю S, два вычитателя по модулю S, два квадратора, два квадр.З тора поправок, дополнительный сумматор, блок сравнения с константой, сумматор, формирующий сумму, увеличенную на единицу, сумматор, формирующий , уменьшенную на единицу, и коммутатор. В устройстве результат перемножения S-ичных чисел а и Ь вычисляется по формуле ab(a+b)2/4-(a-b)2/4. 1 ил.

LHJULJ ZD

| Устройство умножения в системе остаточных классов | 1982 |

|

SU1111160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ТИИЭР, т | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Способ выделения порошкообразной тонкодисперсной фракции из сыпучей смеси | 1956 |

|

SU114116A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-07—Публикация

1985-05-20—Подача