Изобретение относится к цифровой вычислительной технике, в частности к вычислительным устройствам, содержащим некоторые вспомогательные элементы для обнаружения и определения местоположения неисправных элементов путем выполнения вычислительной операции с заранее известным результатом, и может быть использовано для проектирования вьюоконадежных дискретных устройств, а именно быстродей- СТВУЮНЦ1Х устройств управления, которые могут быть использованы в любых областях народного хозяйства.

Целью изобретения является повьше- ние быстродействия.

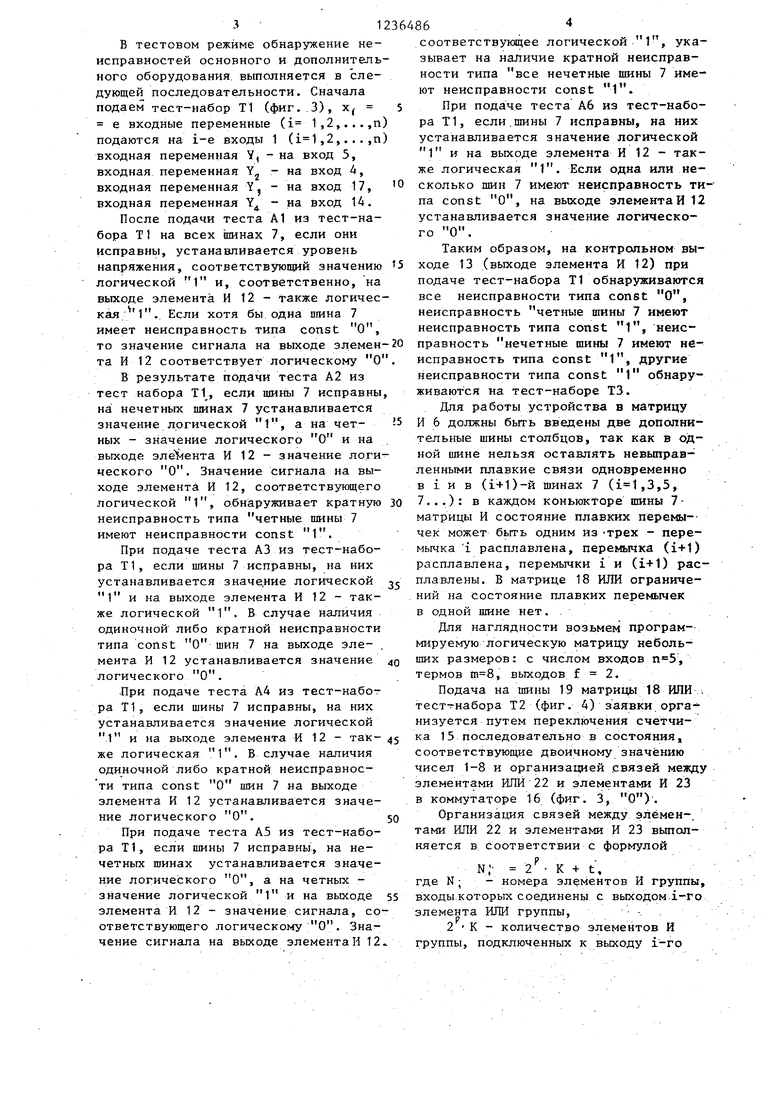

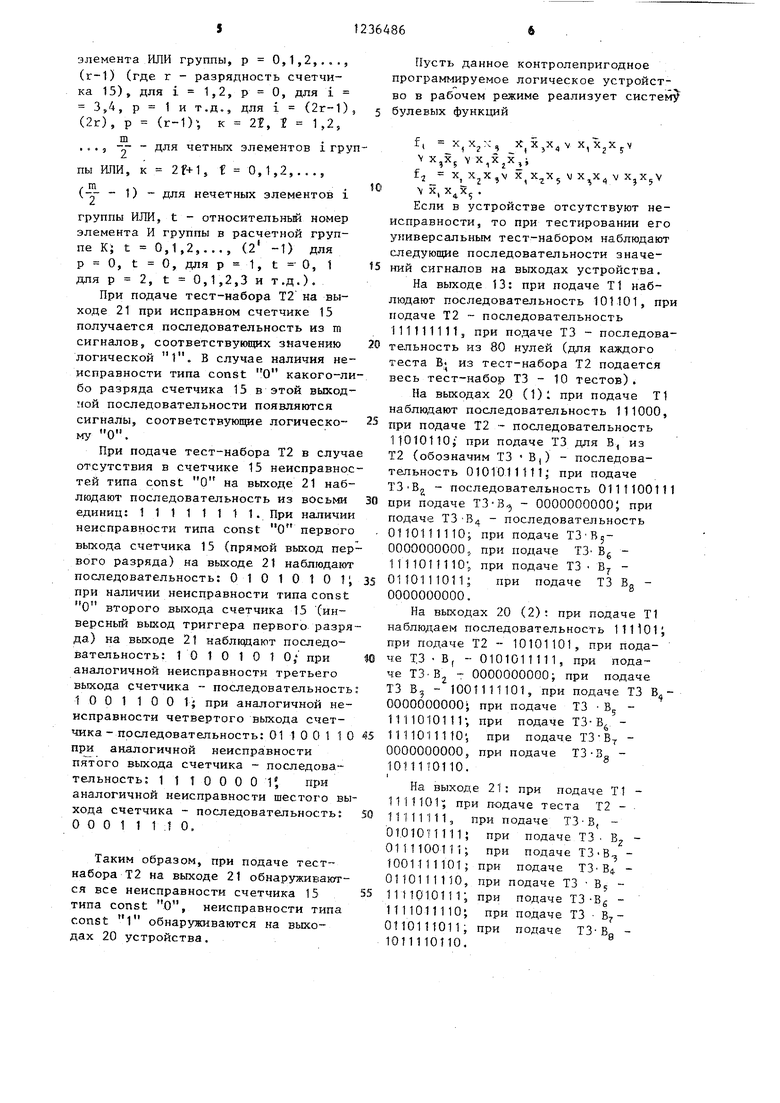

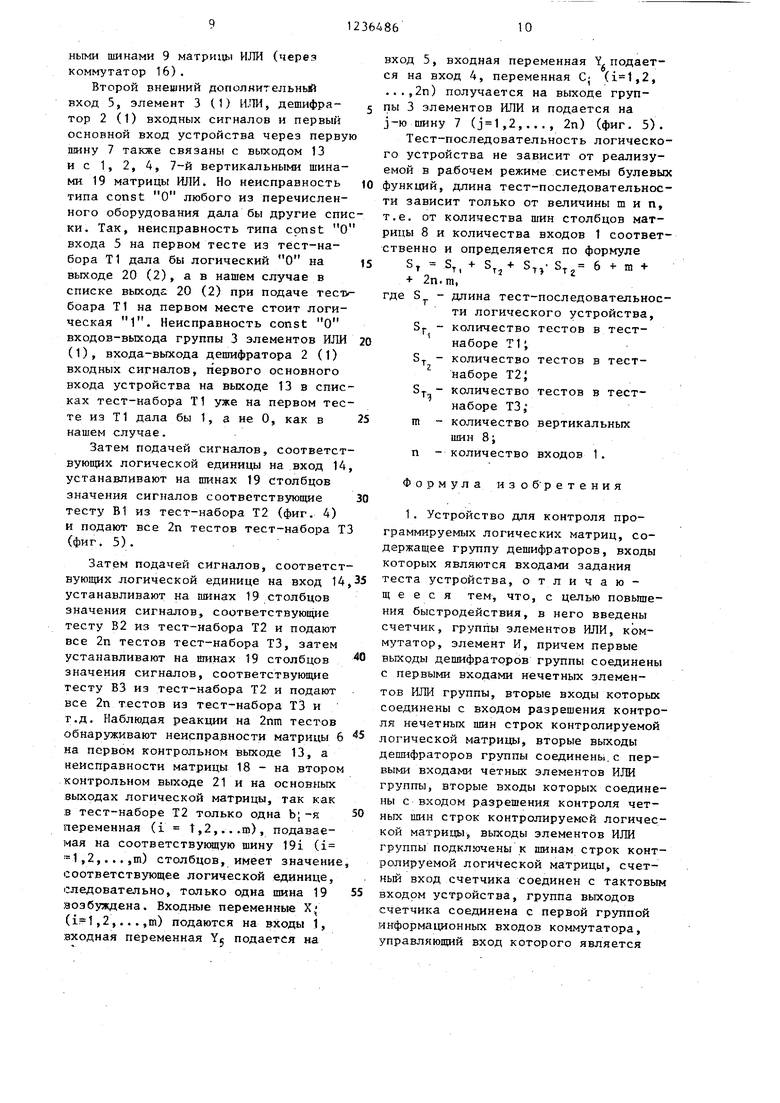

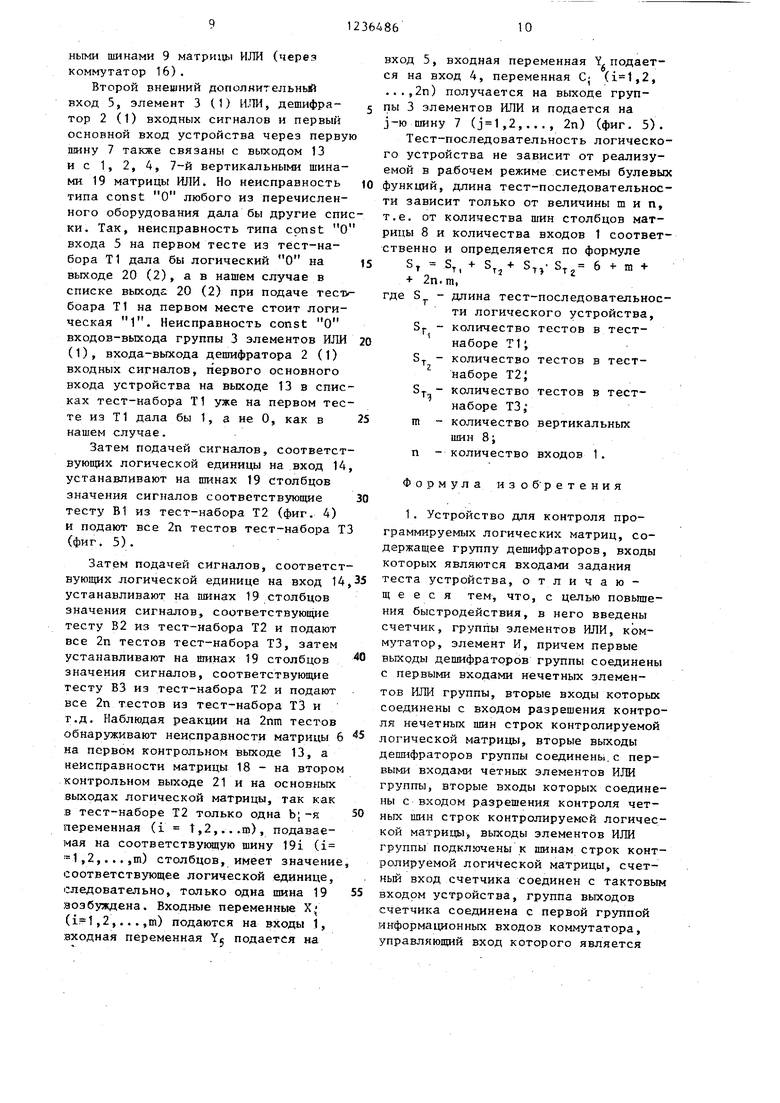

На фиг. 1 приведена функциональная схема устройстваi на фиг. 2 - схема коммутатора , на фиг. 3-5 - таблицы тест-наборов Т1, 12, ТЗ.

Устройство содержит вход 1 задания теста, группу 2 депшфраторов, группу 3 элементов ИЛИ, вход 4 разрешения контроля четных шин строк, вход 5 разрешения контроля нечетных 1№Н строк, матрица 6 элементов И, омны 7 строк матриц элементов И, шины 8 столбцов матрицы элементов И, первая дополнительная вгана 9, место 10 соединения шин строк и шин столбцов невыплавленными плавкими связями, вто рая дополнительная шина 11, элемент И 12, контрольный выход 13, тактовый вход 14 устройства, счетчик 15, коммутатор 16, управляющий вход 17, матрица 18 элемента ИЛИ, шины 19 столбцов матрицы элементов ИЛИ, шины 20 строк матрицы элементов ИЛИ, выход 21 дополнительной шины матрицы элементов ШМ, элементы ИЛИ 22, эле- менты И 23.

Устройство работает следующим образом.

В рабочем режиме на вход 17 подается сигнал, соответствующий значе- нию логической единицы, который переключает коммутатор 1б в режим прямой передачи информации с входа на ВЬЕХОД. На вход 4 и на вход 5 подаются сигна- ЛЫ(, соответствующие значению логичес- кого нуля, за счет чего сигналы на выходах блока 3 повторяют значения сигналов на его входах. Устройство работает в следующей последовательности. На вход 1 подаются значения вход- ных переменных х, дешифраторы входных сигналов 2 (1)-2(п) формируют прямые и инверсные значения сигналов входньгх

переменных (х и х соответственно). Прямые и инверсные значения сигналов входньк переменных х поступают на 2п входов блока 3. Так как на входы разрешения контроля поданы сигналы, соответствующие логическому нулю, то прямые и инверсные значения сигналов входных переменных х без изменения поступают на выходы блока 3 и далее на шины 7, матрица 6 формирует га коньюктивных термов от прямых и инверсных значений входных переменных х, соответствующие шины 7 которых имеют невьтлавленные плавкие связи 10 в точках пересечения с шинами столбцов матрицы 6. Значения полученных термов с шин 8 поступают на j-e входы коммутатора 16, Так как на вход 17 подано значение сигнала, соответствующего логи геской единице, то значение термов, полученные в матрице 6, без изменений проходят на выходы коммутатора 16 и поступают на шины матрицы 18, которая формирует на выходах 20 функции, представляющие собой дизьюнк- ции тех коньюктивных термов, шины 19 которых имеют невьтлавленные плавкие связи 10 в точках пересечения с выходными шинами 20, т.е. устройство реализует систему булевьгх функций, состоящую из f функций, каждая из которых вычисляется в соответствии с формулой

F; v(x,)

j.:X ХМ 1

где FJ - i-я выходная функция из системы булевых функций, реализуемой предлагаемым устройством

.L - номер функции в системе булевых функций, реализуемой предлагаемым устройством, ( ,2,...,f) , f - число функций в системе булевых функций, равное числу выходов матри- ць 18;

X - парафазное значениек-й входной переменной,

к - номер переменной х в коньюктивном терме, к 1,

,п;

п - число входных переменных х, равное количеству входов 1 устройства;

j - номер коньюктивного терма, .входящего в FJ функцию;

га - максимальное число коньюктивных термов, дизъюнкция которых составляет функцию F; , m равно количеству вертикальных шин 8 матрицы 6.

В тестовом режиме обнаружение неисправностей основного и дополнительного оборудования, выполняется в следующей последовательности. Сначала подаем тест-набор Т1 (фиг. 3), х е входные переменные (i 1,2,...,п подаются на i-e входы 1 (,2,.,. ,п входная переменная Y, - на вход 5, входная переменная Y - на вход 4, входная переменная Y, - на вход 17, входная переменная Y - на вход 14.

После подачи теста А1 из тест-набора Т1 на всех шинах 7, если они исправны, устанавливается уровень напряжения, соответствующий значению логической 1 и, соответственно, на выходе элемента И 12 - также логическая 1. Если хотя бы одна пина 7 имеет неисправность типа const О, то значение сигнала на выходе элемен та И 12 соответствует логическому О

В результате подачи теста А2 из тест набора Т1, если шины 7 исправны на нечетных шинах 7 устанавливается значение логической 1, а на чет- ных - значение логического О и на выходе элемента И 12 - значение логического О. Значение сигнала на выходе элемента И 12, соответствующего логической 1, обнаруживает кратную Неисправность типа четные шины 7 имеют неисправности const 1.

При подаче теста A3 из тест-набора Т1, если шины 7 исправны, на них устанавливается значение логической 1 и на выходе элемента И 12 - также логической 1. В случае наличия одиночной либо кратной неисправности типа const О шин 7 на выходе эле- мента И 12 устанавливается значение логического О.

При подаче теста А4 из тест-набот ра Т1, если шины 7 исправны, на них устанавливается значение логической 1 и на выходе элемента И 12 - так- же логическая 1, В случае наличия одиночной либо кратной неисправности типа const О шин 7 на выходе элемента И 12 устанавливается значение логического О.

При подаче теста А5 из тест-набо - ра Т1, если шины 7 исправны, на нечетных шинах устанавливается значение логического О, а на четных - значение логической 1 и на выходе элемента И 12 - значение сигнала, соответствующего логическому . Значение сигнала на выходе элемента И 12

соответствующее логической 1, указывает на наличие кратной неисправности типа все нечетные шины 7 имеют неисправности const 1.

При подаче теста А6 из тест-набора Т1, если.шины 7 исправны, на них устанавливается значение логической 1 и на выходе элемента И 12 - также логическая 1. Если одна или несколько шин 7 имеют неисправность типа const О, на выходе элемента И 12 устанавливается значение логического О.

Таким образом, на контрольном выходе 13 (выходе элемента И 12) при подаче тест-набора Т1 обнаруживаются все неисправности типа const О, неисправность четные шины 7 имеют неисправность типа const 1, неисправность нечетные шины 7 имеют неисправность типа const 1, другие неисправности типа const 1 обнаруживаются на тест-наборе ТЗ.

Для работы устройства в матрицу И 6 должны быть введены две дополнительные шины столбцов, так как в одной шине нельзя оставлять невыправ- ленными плавкие связи одновременно в i и в (1+1)-и шинах 7 (,3,5, 7...): в каждом коньюкторе шины 7- матрицы И состояние плавких перемы-- чек может быть одним из -трех - перемычка i расплавлена, перемычка (1+1) расплавлена, перемычки 1 и (1+1) расплавлены. В матрице 18 ИЛИ ограничений на состояние плавких перемычек в одной шине нет. .

Для наглядности возьмем програм-- мируемую логическую матрицу небольших размеров: с числом входов , термов , выходов f 2.

Подача на шины 19 матрицы 18 ИЛИ тест-набора Т2 (фиг. 4) заявки организуется путем переключения счетчика 15 последовательно в состояния, соответствующие двоичному значению чисел 1-8 и организацией .связей между элементами ИЛИ 22 и элементами И 23 в коммутаторе 16 (фиг. 3, О).

Организация связей между элёмен-. тами ИЛИ 22 и элементами И 23 выполняется в соответствии с формулой

N; 2 К + t, где N ; - номера элементов И группы,

входы которых соединены с выходом 1-го элемента ИЛИ группы, -. .

2 К - количество элементов И группы, подключенных к выходу 1-го

элемента ИЛИ группы, р 0,1,2,,,., (г-1) (где г - разрядность счетчика 15), для i 1,2, р О, для i 3,4, р 1 и т.д., для i (2г-1), (2г), р (г-1), к 21, I 1,2,

m

... 5 -«- для четных элементов i группы ИЛИ, к 2f+1, f 0,1,2,..., ( - 1) - для нечетных элементов i

группы ИЛИ, t - относительный номер элемента И группы в расчетной группе К; t 0,1,2,..., (2 -1) для р О, t О, для р 1, t - О, 1 дпя р 2, t 0,1,2,3ит.д.).

При подаче тест-набора Т2 на выходе 21 при исправном счетчике 15 получается последовательность из га сигналов, соответствующих значению логической 1, В случае наличия неисправности типа const О какого-либо разряда счетчика 15 в этой выходной последовательности появляются сигналы, соответствуюпре логическо- му О.

При подаче тест-набора Т2 в случа отсутствия в счетчике 15 неисправностей типа const О на выходе 21 наблюдают последовательность из восьми единиц: 11111111. При наличии неисправности типа const О первого выхода счетчика 15 (прямой выход первого разряда) на выходе 21 наблюдают последовательность: О 1 О 1 О 1 О 1i при наличии неисправности типа const О второго выхода счетчика 15 (ин- версньш выход триггера первого разряда) на выходе 21 наблюдают последовательность: 10101010, при аналогичной неисправности третьего выхода счетчика - последовательность 1001 1001; при аналогичной неисправности четвертого выхода счетчика-последовательность: 01 1 О О 1 1 О при анялогичной неисправности пятого вьпсода счетчика - последовательность; 1 1 Т О О О О 1 при аналогичной неисправности шестого выхода счетчика - последовательность: 0001 1 1 ;| 0.

Таким образом, при подаче тест- набора Т2 на выходе 21 обнаруживаются все неисправности счетчика 15 типа const О, неисправности типа const 1 обнаруживаются на выходах 20 устройства.

Пусть данное контролепригодное программируемое логическое устройство в рабочем режиме реализует систем булевых функций

f, X,XjX, V X,XjXjV

V V f,; X, J V XjXjV

X, .

Если в устройстве отсутствуют неисправности, то при тестировании его универсальным тест-набором наблюдают (следующие последовательности значений сигналов на выходах устройства.

На выходе 13: при подаче Т1 наблюдают последовательность 101101, пр подаче Т2 - последовательность 111111111, при подаче ТЗ - последовательность из 80 нулей (для каждого теста В- из тест-набора Т2 подается весь тест-набор ТЗ - 10 тестов).

На выходах 20 (1)1 при подаче Т1 наблюдают последовательность 111000, при подаче Т2 - последовательность 11010110; при подаче ТЗ для В, из Т2 (обозначим ТЗ В)) - последовательность 0101011111; при подаче T3 Bg - последовательность 011110011 при подаче ТЗ-В - ОООООООООО; при подаче ТЗ В, - последовательность 0110111110 при подаче ТЗ В5- 0000000000,. при подаче 1 11 lot 1110; при подаче ТЗ 0110111011; при подаче ОООООООООО.

На выходах 20 (2): при подаче Т1 наблюдаем последовательность 111101 при подаче Т2 - 10101101, при подаче ТЗ В, - 0101011111, при подаче ТЗ-В - ОООООООООО; при подаче ТЗ В, - 1001111101, при подаче ТЗ В, ОООООООООО при подаче ТЗ В - 11110101 11-, при подаче ТЗ-В, - 1111011110; при подаче ТЗ В, - ОООООООООО, при подаче T3-Bg - 1011110110.

На выходе 21: при подаче 11 - 1111101 при п-одаче теста Т2 - 111 1 Г111, при подаче ТЗ В, - 01.010П ГЦ; при подаче ТЗ . В - 0111100111; при подаче ТЗ-В - 1001111101; при подаче ТЗ В - 0110111110, при подаче ТЗ BS - 1111010111; при подаче ТЗ-Bg - 1111011110; при подаче ТЗ 0110111011, при подаче ТЗ-Вп - 1011110110.

ТЗ. Bg - BT

Списки нулей и единиц дают следующую информацию: на тест-наборе Т2 - таблицу связей матрицы 18 ИЛИ (единица в списке указывает на наличие невыплавленной плавкой связи 10)j на тест-наборе ТЗ - таблицы связей матриц И 6 и ИЛИ 18 (если при подаче в списке все нули, то связь в матрице 18 ИЛИ в точке пересечения i-й вертикальной пины 19 матрицы ИЛИ с рассматриваемой выходной шиной 20 (J) отсутствует, если список состоит из нулей и единиц, то такая связь имеется, а в матрице 6 и на i-й вер- тикальной шине 8 матрицы И невьшлав- ленные плавкие связи 10 имеются в то точках пересечения с промежуточным горизонтальными шинами 7, номера которых соответствуют номерам нулей в списке.

Рассмотрим списки на вькоде 20(1) На наборе Т2 единицы указывают на наличие невыплавленных плавких связей 10 в матрице 18 ИЛИ в точках пересечения выходной горизонтальной шины 20 (1) с первой, второй, четвертой, шестой и седьмой вертикальными шинами 19 матрицы ИЛИ. При подаче ТЗ-В, T3.Bg - в списках на вьпсоде 20 (1) все нули, следовательно, в матрице 18 ИЛИ невыплавленных плавких связей 10 нет в точках пересечения первой шиной 20 (1) с третьей, пятой и восьмой вертикальны ми шинами 19 матрицы ИЛИ, т.е. есть такие связи в точках пересечения первой шиной 20 (1) с первой, второй, четвертой, шестой и седьмой вертикальными шинами 19 матрицы (термы функции f, системы булевых функций (1) реализованы на первой, второй, четвертой, шестой и седьмой вертикалных шинах 8 матрицы И) - информация совпадает с полученной на тест-набо- ре Т2 и описанному выше. Наличие нулей в списках при подаче ТЗ В,,ТЗ В ТЗ-В, ТЗ-В, ТЗ В указывает на наличие невыплавленных плавких связей 10 в матрице 6 И соответственно первой, второй, четвертой, шестой и седьмой вертикальных шинах 8 матрицы И. Например, при подаче , список -на выходе 20 (1) имеет вид 0101011111. Это означает, что на первой вертикальной шине 8 матрицы И невьшлавленные плавкие связи,10 имеются в точках пересечения с первой.

5

j 0 5 0

0

третьей и пятой шинами 7, при подаче .ТЗ В список имеет вид: 0111100111. Это означает, что на второй вертикальной шине 8 матрицы И имеются невыплавленные плавкие связи 10 в точках пересечения с первой, шестой и седьмой шинами 7.

Рассмотрим как меняются списки при наличии неисправностей в устройстве. Допустим в результате тестирования получены следующие списки на выходах устройства..

На первом дополнительном выходе 13: при Т1 - 000000, при Т2 - 00000000, при ТЗ - 80 нулей.

На выходе 20 (1): при Т1 - t11000, при 12 - 00000100, ТЗ- В, -0000000000, при ТЗ-Bj, - 000000000, при ТЗ В - 000000000, при ТЗ-В4 - 0000000000, - при la-Bg - 0000000000, при T3 Bg- 11 нот 10, при ТЗ-В -0000000000, при ТЗ-Вд - 0000000000.

На выходе 20 (2): при Т1 - 111101, при Т2 - 00101101, при ТЗ-В, - 0000000000, при ТЗ Вг - 0000000000, при ТЗ-В,.- 1001111101, при ТЗ-В4 - 0000000000, при ТЗ Ву - 1111010111, при ТЗ«В - 1111011110, при ТЗ-BT - 0000000000, при ТЗ-Ве -1011110110.

На выходе 21: 111101 - при подаче Т1, при Т2 - 00101101, при ТЗ-В, 0000000000, при ТЗ В-1 - 0000000000, при ТЗ В - 1001111101, при ТЗ В - 0000000000, при ТЗ В - 1111010111, при ТЗ Вб - 1111011110, при T3-Bj - 0000000000, при ТЗ-В - 1011110110.

Сравнение списков на выходах исправного и неисправного устройств позволяет сделать следующие выводы.

Одновременное изменение 1 и О Е списках выхода 13 на тест-наборах 11 и Т2, в списках выхода 20 (1) на тест-наборах 12, ТЗ В,, ТЗ-В, ТЗ В, ТЗ-В, в списках выхода 20 2) на тест-наборах Т2, ТЗ«В, в списках выхода 21 на тест-наборах Т2, ТЗ-В, ТЗ Вз, ТЗ-В, ТЗ-BV свидетельствует о наличии в устройстве неисправности типа const О, связанной с первой, второй, четвертой, седьмой вертикальными шинами 19 матрицы .ИЛИ и одновременно влияющей на выход 13. Такой не- исправностью может быть только неисправность типа const О первой шины 7, так как только первая шина 7 связана и с выходом 13, и с первой, ВТОРОЙ, четвертой, седьмой вертикальными шинами 9 матрицы ИЛИ (через коммутатор 16).

Второй внешний дополнительный вход 5, элемент 3 (1) И.ТИ, дешифра- тор 2 (1) входных сигналов и первый основной вход устройства через первую шину 7 также связаны с выходом 13 и с 1, 2, 4, 7-й вертикальными шинами 19 матрицы ИЛИ, Но неисправность типа const О любого из перечисленного оборудования дала бы другие списки. Так, неисправность типа const О входа 5 на первом тесте из тест-набора Т1 дала бы логический О на выходе 20 (2), а в нашем случае в списке выхода 20 (2) при подаче тесту- боара Т1 на первом месте стоит логическая 1. Неисправность const О входов-выхода группы 3 элементов ИЛИ (1), входа-выхода дешифратора 2 (1) входных сигналов, первого основного входа устройства на выходе 13 в списках тест-набора Т1 уже на первом тесте из Т1 дала бы 1, а не О, как в нашем случае.

Затем подачей сигналов, соответствующих логической единицы на вход 14 устанавливают на шинах 19 столбцов значения сигналов соответствующие тесту В1 из тест-набора Т2 (фиг. 4) и подают все 2п тестов тест-набора ТЗ (фиг. 5).

Затем подачей сигналов, соответствующих логической единице на вход 14 устанавливают на шинах 19 столбцов значения сигналов, соответствующие тесту В2 из тест-набора Т2 и подают все 2п тестов тест-набора ТЗ, затем устанавливают на шинах 19 столбцов значения сигнашов, соответствующие тесту ВЗ из тест-набора Т2 и подают все 2п тестов из тест-набора ТЗ и т.д. Наблюдая реакции на 2пт тестов обнаруживают неисправности матрицы 6 на первом контрольном выходе 13, а неисправности матрицы 18 - на втором контрольном выходе 21 и на основных выходах логической матрицы, так как в тест-наборе Т2 только одна Ь; -я переменная (i Т,2,,..m), подаваемая на соответствующую шину 191 (i

1,2m) столбцов, имеет значение

соответствующее логической единице, следовательно, только одна шина 19 возбуждена. Входные переменные X, (,2,.. . ,т) подаются на входы 1, входная переменная YC подается на

.

вход 5, входная переменная Y, подается на вход 4, переменная Cj (,2, ..,2п) получается на выходе группы 3 элементов ИЛИ и подается на j-ю шину 7 (,2,..,, 2п) (фиг. 5).

Тест-последовательность логического устройства не зависит от реализуемой в рабочем режиме системы булевых функций, длина тест-последовательности зависит только от величины шип, т.е. от количества шин столбцов матрицы 8 и количества входов 1 соответственно и определяется по формуле ST S,, + S S,. 5,,, 6 + m + + 2n. m,

где S - длина тест-последовательности логического устройства, Sj- - количество тестов в тест- наборе Т1; S - количество тестов в тест - наборе Т2;

S, - количество тестов в тест- наборе ТЗ; m - количество вертикальных

шин 8f п - количество входов 1.

Формула изоб ретения

1. Устройство для контроля программируемых логических матриц, содержащее группу дешифраторов, входы которых являются входами задания теста устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены счетчик, группы элементов ИЛИ, коммутатор, элемент И, причем первые выходы дешифраторов группы соединены с первыми входами нечетных элементов ИЛИ группы, вторые входы которых соединены с входом разрешения контроля нечетных шин строк контролируемой логической матрицы, вторые выходы дешифраторов группы соединены.с первыми входами четных элементов ИЛИ группы, вторые входы которых соединены с входом разрешения контроля четных шин строк контролируемой логической матрицы, выходы элементов ИЛИ группы подключены к шинам строк контролируемой логической матрицы, счетный вход счетчика соединен с тактовы входом устройства, группа выходов счетчика соединена с первой группой информационных входов коммутатора, управляющий вход которого является

входом разрешения устройства, вторая группа информационных входов коммутатора соединена с первого по п выходами шин столбцов контролируемой логи- ческой матрицы (п+1) и (п+2) выходы . пшн столбцов контролируемой логической матрицы соединены с входами элемента И, выход которого является контрольным выходом устройства, выхо- ды коммутатора подключены к шинам столбцов контролируемой логической матрицы.

2. Устройство по п. 1, о т л и- чающееся тем, что для m 8, где m - число вертикальных шин матрицы , коммутатор содержит группу элементов И и группу элементов ШЖ, причем управляющий вход коммутатора соединен с первыми входами элементов ИЛИ группы, вторые входы которых соединены с соответствукицими входами первой группы информационных входов коммутатора, выход первого элемента ИЛИ группы соединен с первыми входами первого второго, третьего и четвертого элементов И группы, выход второго элемента ИЛИ группы соединен с первыми входами пятого, шестого, седьмого и восьмого элементов И группы, выход третьего элемента ИЛИ группы соединен с вторыми входами второго, четвертого, пятого и седьмого элементов И группы, выход четвертого элемента ИЛИ группы соединен с вторыми входами первого, третьего, шестого и восьмого элементов И группы, выход пятого элемента ИЛИ группы соединен с третьими входами третьего, четвертого, шестого и восьмого элементов И группы, выход шестого элемента ИЛИ группы соединен с третьими входами первого, второго, пятого и восьмого элементов И группы, четвертые входы элементов И группы соединены с соответствующими входами второй группы информационных входов коммутатора, выходы элементов И группы являются выходами коммутатора.

8

фиг. }

19

фиг. г

Tecm-HoSOpTj

{mmimms)

Tec т-набор

Редактор Г.Волкова

Заказ 3092/52

.Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

тг

Фиг. 4 Тест-набор rj

Фиг. 5

Составитель C.CTpeNOiH

Техред М.Ходанич Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1980 |

|

SU1096657A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Контроллер прямого доступа к памяти | 1991 |

|

SU1789987A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ЭЛЕМЕНТОВ КОНТУРНОГО ИЗОБРАЖЕНИЯ | 1991 |

|

RU2015560C1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| СИСТЕМА ДИАГНОСТИКИ ЗАБОЛЕВАНИЙ | 1991 |

|

RU2007755C1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для проектирования вьгср- конадежных дискретных устройств.Цель изобретения - повьппение быстродействия устройства; Цель достигается тем, что в устройство, содержащее группу дешифраторов, введены группа элементов ИЛИ, коммутатор, элемент И. 1 з.п. ф-лы, 5 ил. IND со О) 00 о

| Основы технической диагностики | |||

| /Под ред | |||

| П.П.Пархоменко, М.: Энергия, 1976, с | |||

| Телефонная трансляция | 1922 |

|

SU464A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

Авторы

Даты

1986-06-07—Публикация

1983-10-11—Подача