Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля объектов, и может быть использовано для проверки интегральных схем, а также узлов и блоков ЭВМ и других средств цифровой автоматики как при производстве, так и при эксплуатации этих узлов и блоков.

Целью изобретения является расширение области применения и увеличение быстродействия устройства.

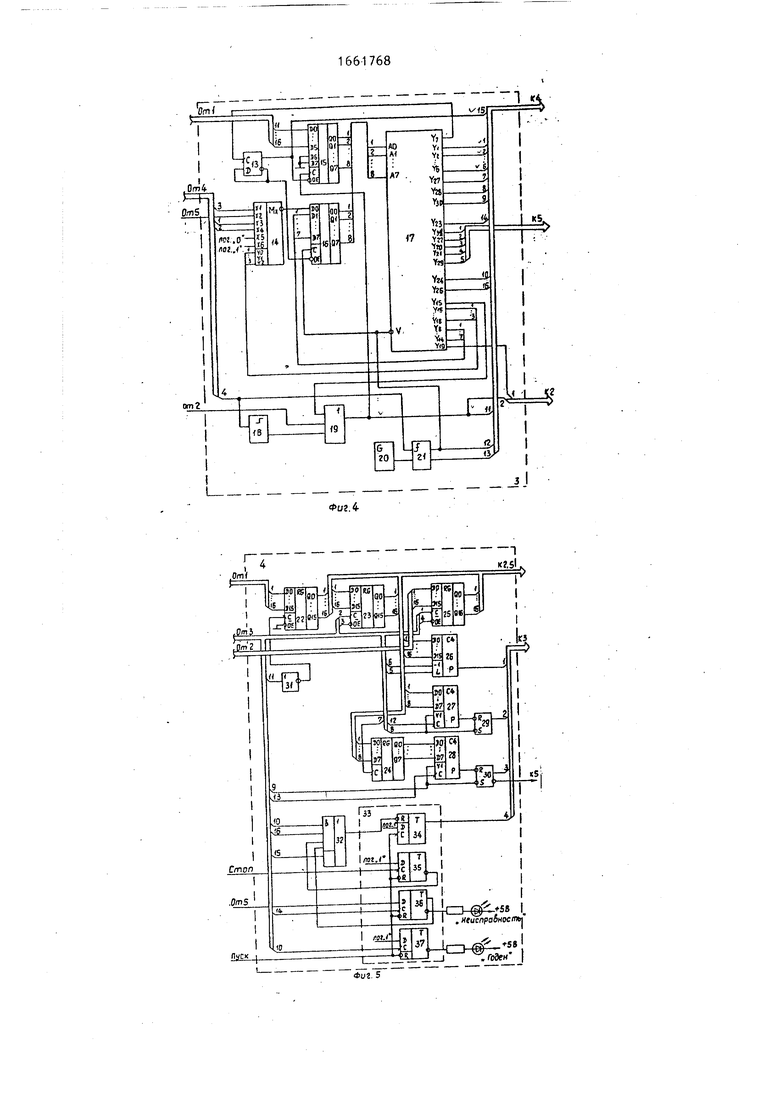

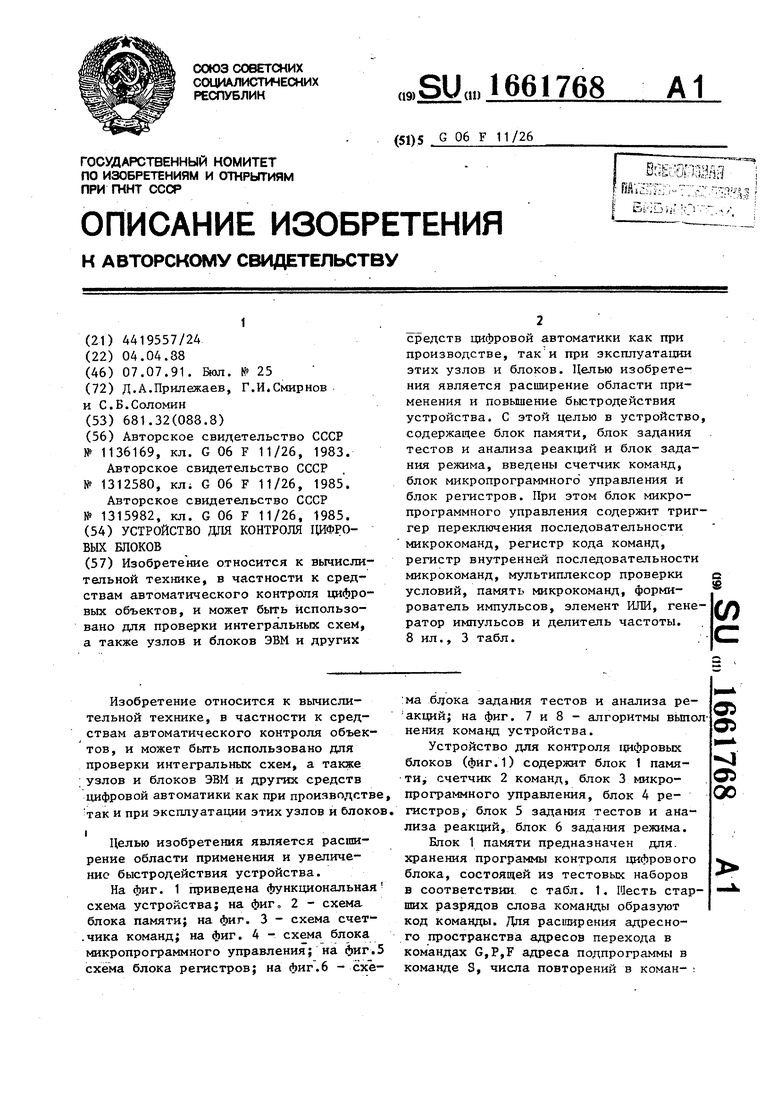

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 - схема блока памяти; на фиг. 3 - схема счет- .чика команд; на фиг. 4 - схема блока микропрограммного управления; на фиг.5 схема блока регистров; на фиг.6 - схема блока задания тестов и анализа реакций; на фиг. 7 и 8 - алгоритмы выпол нения команд устройства.

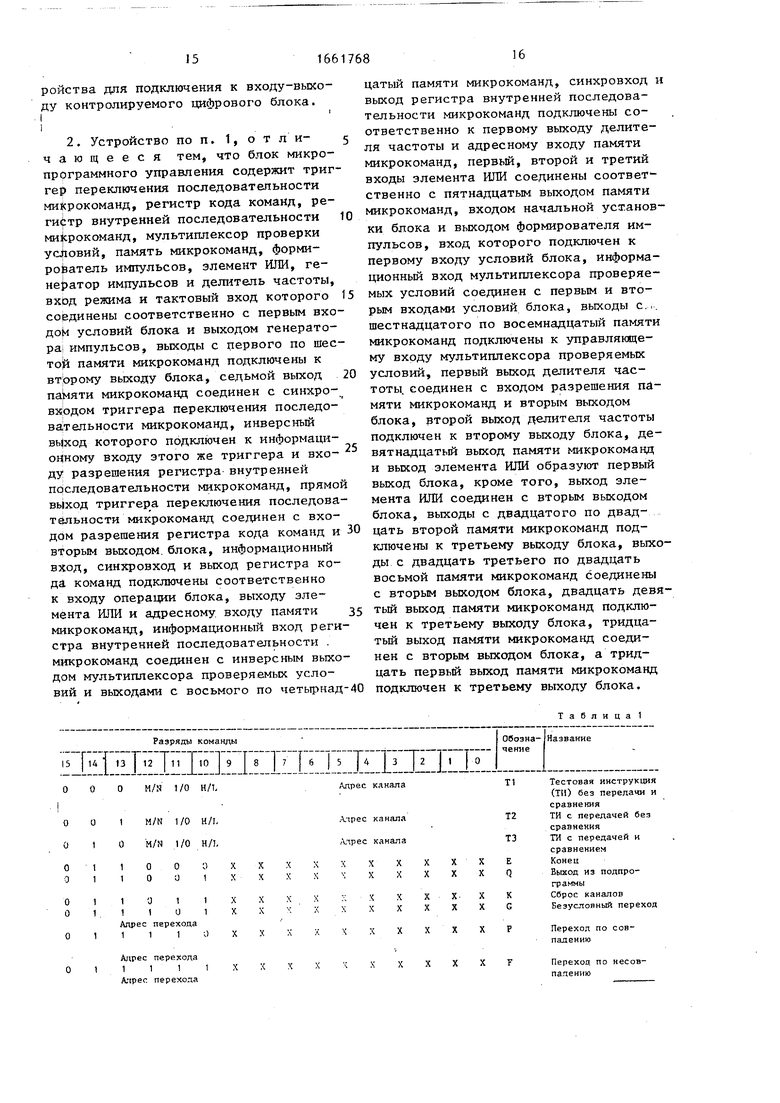

Устройство для контроля цифровых блоков (фиг.1) содержит блок 1 памяти, счетчик 2 команд, блок 3 микропрограммного управления, блок 4 регистров, блок 5 задания тестов и анализа реакций, блок 6 задания режима.

Блок 1 памяти предназначен для хранения программы контроля цифрового блока, состоящей из тестовых наборов в соответствии с табл. 1, Шесть старших разрядов слова команды образуют код команды. Для расширения адресного пространства адресов перехода в командах G,P,F адреса подпрограммы в команде S, числа повторений в коман-

о

05

1

05 00

дй С эти команды состоят из двух слов, последовательно идущих друг -ча другом. Шесть старших разрядов первого слова образуют код команды, а второе слово - соответственно адрес перехода, адрес подпрограммы, значение числа повторений.

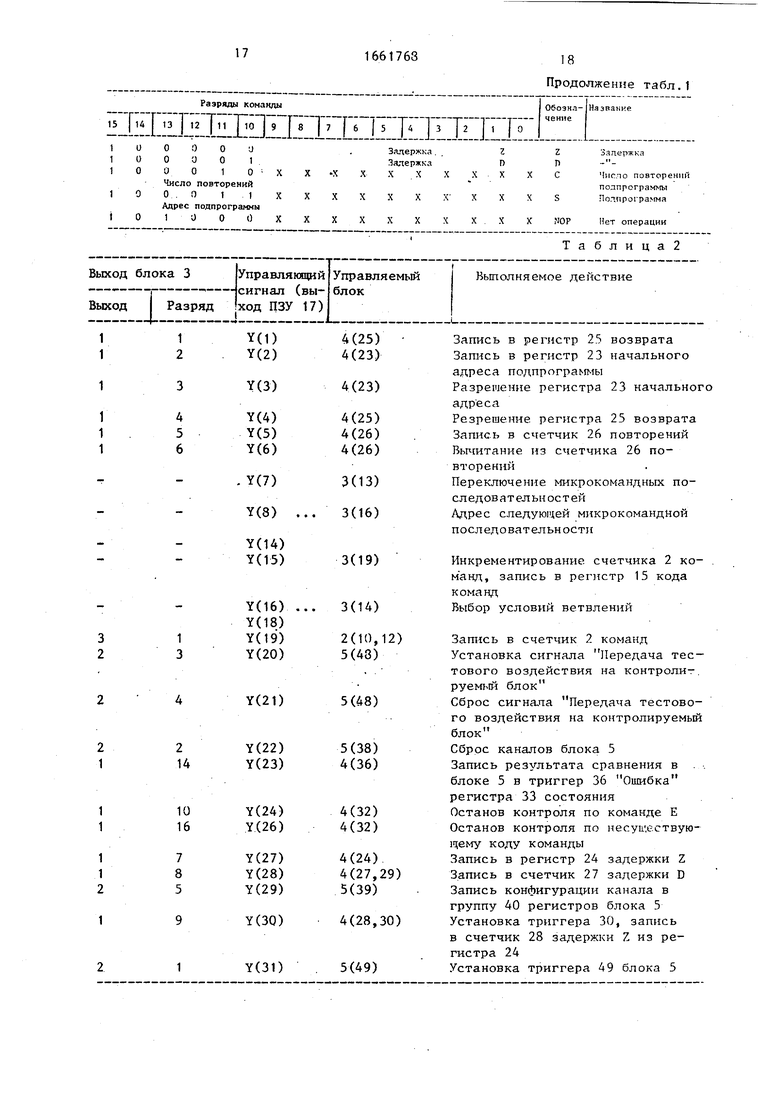

I Елок 1 памяти (фиг. 2) состоит из шинного формирователя 7, дешифратора . 8 блока 9 микросхем памяти (ПЗУ)„ Шинный формирователь 7 служит для бу- фбрирования шины адреса блока 9 микросхем ПЗУ, дешифратор 8 служит для выборки микросхем в блоке 9 микросхем j ПЗУ. Счетчик 2 команд служит для адресации блока 1 памяти, записи в него адреса перехода при выполнении команд G, Р, F адреса подпрограммы при выполнении команды S и адреса возвра- J та из подпрограммы при выполнении команды Q.

Система команд устройства для контроля цифровых блоков.

В табл. 1 приняты следующие обозначения: M/N, 1/0, H/L - разряды, определяющие конфигурацию канала; M/N - разряд маскирования; - канал сравнивается в бяоке 5 при сравнении; - канал не сравнивается в блоке 5 , при сравнении; 1/0 - разряд вход/выход; - канал работает на выдачу воздействия; - канал работает на прием воздействия; H/L - разряд логического уровня на контролируемом ка- Кале; - высокий логический уровень; - низкий логический уровень; X - безразличное состояние.

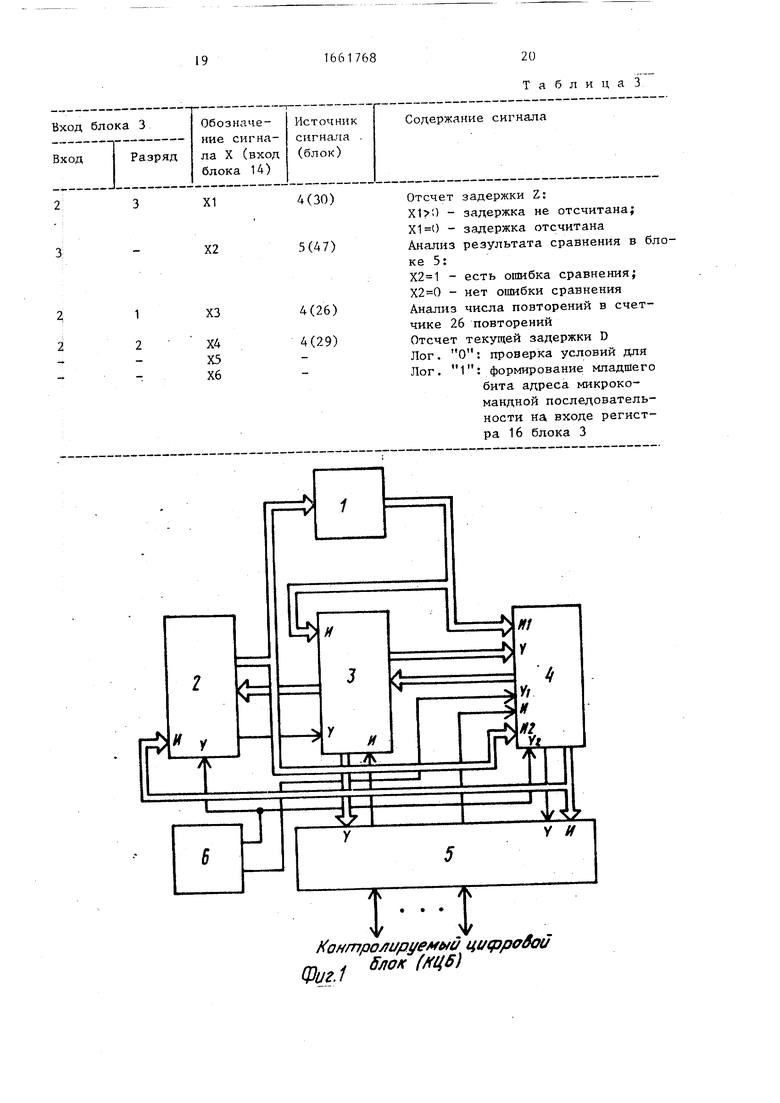

Счетчик 2 команд (фиг. 3) состоит Из группы счетчиков 10 и формировате-4 лей- 11 и 12 импульсов. Формирователь 12 импульсов служит для формирования Импульса по отрицательному фронту сигнала на его входе, что обеспечивает синхронизацию загрузки в группу счет- Чиков 10. Формирователь 11 импульсов служит для формирования отрицательного импульса по отрицательному фронту сигнала Пуск с выхода блока 6. Сформированный импульс сбрасывает по вхо- дам Сброс группу счетчиков 10 перед началом процесса контроля.

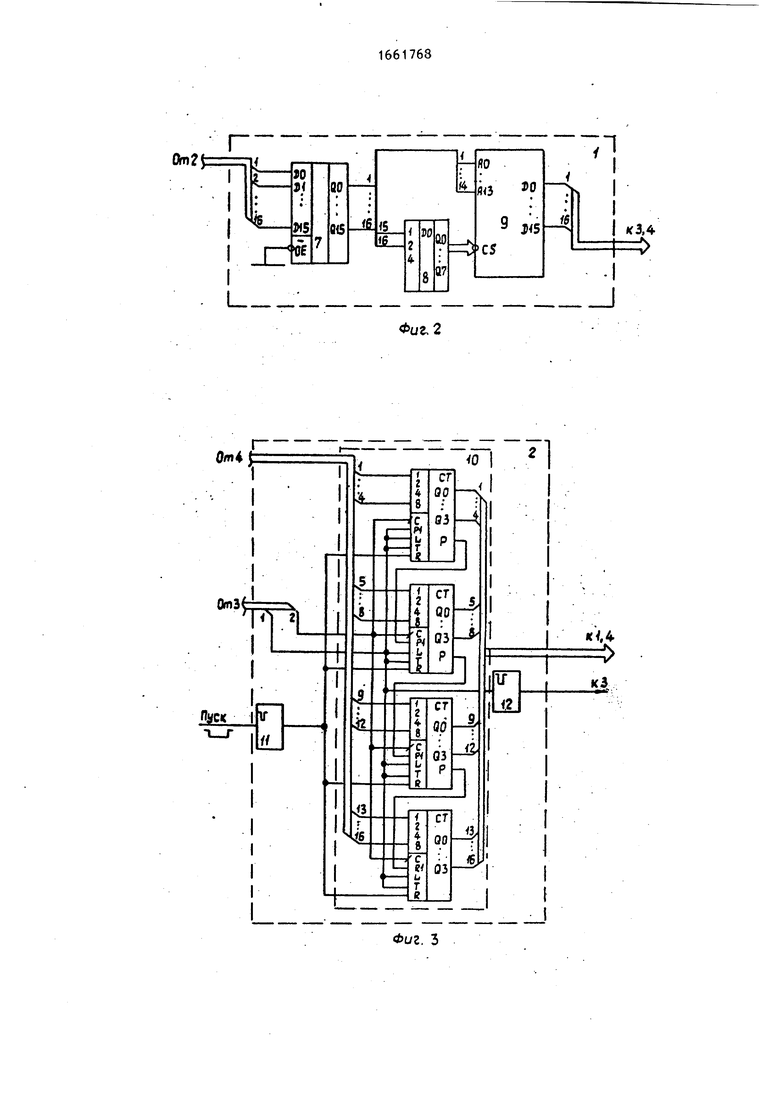

Блок 3 микропрограммного управления (ЕМУ) служит для синхронизации работы всех блоков устройства, для управления обменом данных между блоками, между устройством и контролируемым блоком. Блок 3 (БМУ) состоит из триггера 13 переключения последо3

c

5 ,.

0 г Q

,

5

вательности микрокоманд, мультиплексора 14 проверки условий, регистра 15 кода команд, регистра 16 внутренней последовательности микрокоманд, шины 17 памяти микрокоманд, формирователя 18 импульсов, элемента ИЛИ 19, генератора 20 импульсов, делителя 21 частоты. Триггер 13 переключения последовательности микрокоманд служит для подключения к адресным входам 17 памяти либо адреса, определяемого кодом команд, считанным из блока 1 памяти, либо адреса перехода с выходов шины 17 памяти (ПЗУ) при выполнении команд устройства, состоящих из нескольких микрокомандных последовательностей (фиг. 7 и 8). Регистр 15 кода команд служит для записи кода команды устройства, который является адресом первой микрокомандной последовательности при выполнении соответствующей команды. Регистр 16 внутренней последовательности микрЪкоманд служит для записи адреса следующей микрокомандной последовательности с выхода шины 17 памяти при выполнении команд устройства, состоящих из нескольких микрокомандных последовательностей.

Соответствующие выходы регистра 15 и регистра 16 объединены и образуют адресную шину 17 памяти. Но поскольку эти регистры выполнены на элементах с третьим состоянием,-которое управляется от прямого и инверсного выходов триггера 13, то в любой момент времени с адресной шиной 17 памяти связан один из этих регистров, а другой находится в отключенном состоянии. Мультиплексор 14 проверки условий служит для проверки условий ветвления в мик- рокомандных последовательностях. Ыина 17 микроманд- содержит микрокоманды Y(1), (табл. 2), распределенные в соответствии с системой команд (табл. 1) и алгоритмами их выполнения (фиг. 7,8). Формирователь 13 импульсов служит для формирования импульса по положительному фронту сигнала на его входе.

Клок 3 обеспечивает взаимодействие всех блоков устройства путем выработки соответствующих управляющих сигналов в соответствии с значениями осведомительных сигналов, поступающих на входы логических условий блока. Алгоритмы работы блока 3 приведены в виде блок-схем на фиг. 7,8. Управляющие сигналы Y(1), заданные в операторных

вершинах алгоритмов и представляющие микрокоманды, описаны в табл. 2, где каждому сигналу сопоставлен номер и разряд выхода блока 3, являющегося источником этого сигнала, номер блока, которым этот разряд управляет , а также выполняемое под управлением этого сигнала действие. Микрокомандные последовательности на фиг. 7,8 имеют следующие обоззначения: Т1 - обозначение команды в соответствии с табл.1; 1 - номер микрокомандной последовательности в данной команде.

ми, входы разрешения которых управОсведомительные сигналы Х(1) в ус- 5 ляются микрокомандами в соответствии ловных вершинах алгоритмов описаны с алгоритмами (фиг.7,8), то в любой в табл. 3, где каждому сигналу Х(1) сопоставлены номер и разряд входа блока 3, номер блока, являющегося источ20

ником этого сигнала, и характеристика логического условия, представленного этим сигналом.

Блок 4 регистров (фиг. 5) предназначен для осуществления функциональных возможностей устройства в соответ-25 писи в него из буферного регистра 22 ствии с системой команд (табл. 1), значения задержки П при выполнении Блок 4 регистров состоит из буферного регистра 22, регистра 23 начального адреса, регистра 24 задержки Z, регимомент времени шина нагружается на один из указанных регистров, а ос тальные находятся в отключенном состоянии. Счетчик 26 повторений служит для записи значения числа повторений подпрограммы из буферного регистра 2 при выполнении команды с устройства. Счетчик 27 задержки D служит для закоманды D и формирования на выходе триггера 29 импульса длительностью, соответствующей задержке П. Счетчик

стра 25 возврата, счетчика 26 повторе-зо 28 задержки Z служит для записи из ний подпрограммы, счетчика 27 задержки D, счетчика 28 задержки Z, триггеров 29,30, элемента НЕ 31, элемента И-ИЛИ 32, регистра 33 состояния. Прирегистра 24 значения задержки Z пр выполнении команды ТЗ и формировани на выходе триггера 30 импульса длительностью, соответствующей задержке Z. Триггер 34 устанавливается пр пуске процесса контроля по входу Пуск устройства, сбрасывается по ошибке контроля, по концу контроля и по несуществующему коду команды.

чем, регистр 33 состояния состоит из триггера 34 Работа, триггера 35 Стоп, триггера 36 Ошибка, триггера 37 Годен. Буферный регистр 22 служит для записи из блока 1 памяти

регистра 24 значения задержки Z при выполнении команды ТЗ и формирования на выходе триггера 30 импульса длительностью, соответствующей задержке Z. Триггер 34 устанавливается при пуске процесса контроля по входу Пуск устройства, сбрасывается по ошибке контроля, по концу контроля и по несуществующему коду команды.

аргумента команды (для команд, состоя- 4Q Триггер 35 устанавливается по входу щих из двух шестнадцатиразрядных слов Стоп устройства, сбрасывается авто- (табл. 1) с последующей записью его матически в момент пуска контроля. в регистр 23 начального адреса, в Триггер 36 Ошибка устанавливается

при возникновении несовпадения в бло- 45 ке 5 эталонных сигналов и реальных

откликов контролируемого блока и сбрасчетчик 26 повторений, счетчик 27 задержки I), регистра 24 задержки Z, счетчик 2 команд в соответствии с алгоритмами работы. Регистр 33 состояния отражает состояние устройства и индикацию состояния Годен/брак просывается автоматически в момент пуска. Триггер 37 устанавливается по окончанию процесса контроля и сбрасывается

веряемого цифрового блока. Регистр 23 50 в момент пуска,

6617686

ки Z при выполнении команды ТЗ. Регистр 25 возврата служит для записи адреса выхода из подпрограммы при выполнении команды S устройства с последующей записью в счетчик 2 команд при выполнении команды О устройства. Соответствующие выходы буферного регистра 22, регистра 23 начального адреса, регистра 25 возврата объединены и образуют шину команды устройства. Поскольку эти регистры выполнены на элементах с третьими состояния10

ми, входы разрешения которых управляются микрокомандами в соответствии с алгоритмами (фиг.7,8), то в любой

писи в него из буферного регистра 22 значения задержки П при выполнении

момент времени шина нагружается на один из указанных регистров, а остальные находятся в отключенном состоянии. Счетчик 26 повторений служит для записи значения числа повторений подпрограммы из буферного регистра 22 при выполнении команды с устройства. Счетчик 27 задержки D служит для записи в него из буферного регистра 22 значения задержки П при выполнении

команды D и формирования на выходе триггера 29 импульса длительностью, соответствующей задержке П. Счетчик

28 задержки Z служит для записи из

регистра 24 значения задержки Z при выполнении команды ТЗ и формирования на выходе триггера 30 импульса длительностью, соответствующей задержке Z. Триггер 34 устанавливается при пуске процесса контроля по входу Пуск устройства, сбрасывается по ошибке контроля, по концу контроля и по несуществующему коду команды.

Триггер 35 устанавливается по входу Стоп устройства, сбрасывается авто- матически в момент пуска контроля. Триггер 36 Ошибка устанавливается

сывается автоматически в момент пуска. Триггер 37 устанавливается по окончанию процесса контроля и сбрасывается

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

Изобретение относится к вычислительной технике, а точнее - к средствам автоматического контроля цифровых объектов, и может быть использовано для проверки интегральных схем, а также узлов и блоков ЭВМ и других средств цифровой автоматики как при производстве, так и при эксплуатации этих узлов и блоков. Целью изобретения является расширение области применения и повышение быстродействия устройства. С этой целью в устройство, содержащее блок памяти, блок задания тестов и анализа реакций и блок задания режима, введены счетчик команд, блок микропрограммного управления и блок регистров. При этом блок микропрограммного управления содержит триггер переключения последовательности микрокоманд, регистр кода команд, регистр внутренней последовательности микрокоманд, мультиплексор проверки условий, память микрокоманд, формирователь импульсов, элемент ИЛИ, генератор импульсов и делитель частоты. 3 табл., 8 ил.

начального адреса служит для записи адреса подпрограммы при выполнении команды S с последующей записью его в счетчик 2 команд в соответствии с алгоритмами работы Регистр 24 задержки Z служит для записи значения . задержки Z из буферного регистра 22 при выполнении команды Z с последующей записью в счетчик 28 задерж-

Блок 5 задания тестов и анализа реакций (фиг. 6) служит для выдачи тестовых воздействий на контролируемый цифровой блок, сравнения реальных от- кликов с контролируемого блока с эталонными и выдачи результатов сравнения в блок 4 регистров и блок 3 микропрограммного управления. Блок 5 состоит из группы элементов ИЛИ 38, дешифратора 39, группы регистров 40, группы элементов 41 сравнения, группы регистров 42, группы элементов И 43, группы элементов И 44, группы двунаправленных приемо-передатчиков 45, регистра 46 результатов сравнения, элемента ИЛИ 47, триггеров 48, 49. Значение N равно числу контролируемых каналов.

Дешифратор 39 служит для записи в группу регистров 40 значений конфигурации каналов M/N, 1/0, H/L (см. табл. 1). Группа элементов 41 сравнения служит для сравнения реальных от- кликов с контролируемого цифрового блока с эталонными из группы регистров 40. Результат сравнения появляется на выходах группы элементов И 43. Группа регистров 42 служит для записи параметров канала (1/0, H/L) для выдачи тестовых воздействий через группу элементов И 44 и приемопередатчики 45 на контролируемый цифровой блок

Блок задания режима служит для пус ка и останова процесса контроля и состоит из двух кнопок типа ПКВ 9-1, при нажатии на которые на их выходах формируются импульсы отрицательной полярности (сигналы Пуск, Стоп) .

Устройство работает следующим образом.

После включения питания устройства происходит начальный сброс триггеров регистра 33 состояния и триггера 13 БМУ (цепи сброса на схемах не показаны) . После начального сброса триггера 13 блока 3 адрес памяти определяется через регистр 15 кодом команды, считываемой из блока 1 памяти. Таким образом, память готова для отработки команды из блока 1 памяти. После начального сброса триггера 34 Работа регистра 33 блокируется на делителе 21 частоты блока 3 выдачи синхроимпульсов на вход памяти до момента пуска программы контроля по входу Пуск устройства.

Программа проверки контролируемого цифрового блока находится в блоке 1 памяти. Пуск осуществляется следукмтим образом. При нажатии кнопки Пуск блока 6 приходит отрицательный импульс на формирователь 11 импульсов

счетчика 2, который по отрицательному 55 передачи воздействия на контролируефронту входного сигнала формирует импульс, поступающий на входы Сброс группы счетчиков 10 счетчика 2, который при этом сбрасывается. В соответмый блок и без сравнения содержит од ну микрокомандную последовательность Т1/1. При выполнении Т1/1 происходит запись конфигурации канала с выхода

ствии с нулевым значением счетчика l команд, являющимся адресом качала программы контроля, из блока 1 памяти выбирается первая команда, код кото- рой поступает на входы регистра 15 блока 3.

Положительным фронтом сигнала Пуск устанавливается триггер 34 Работа регистра 33 состояния. С вы- хода триггера 34 сигнал поступает на первый вход делителя 21 частоты блока 3, разрешая синхронизацию памяти 17, а также на вход формирователя 18 импульсов, который формирует импульс по положительному перепаду входного сигнала. Сформированный импульс через элемент 19 поступает на синхро- вход регистра 15, записывая в.него код команды, выбранный из блока 1, а также на счетный вход счетчика 2, увеличивая его значение на 1. По этому новому адресу из блока 1 памяти выбирается следующая команда или аргумент предыдущей команды, если она состоит из двух слов. Одновременно с этим выполняется команда, код которой записан в регистр 15 кода команд блока 3 в соответствии с алгоритмами работы устройства.

Таким образом, регистр 15 является конвейерным регистром и обеспечивает совмещение по времени процессов выборки из блока 1 памяти следующей команды и выполнения предыдущей. Если текущая команда состоит из одной микрокомандной последовательности (фиг.7 8), то адрес следующей команды определяется регистром 15 кода команд. Если текущая команда состоит из нескольких микрокомандных последовательностей (команды ТЗ, G,P,F,S,Q,C,I,D), то адрес следующей команды определяется выходами Y(8) - Y(14) памяти 17 блока 3 и выходом мультиплексора 14 (проверки условий ветвления) при переключении триггера 13 блока 3 микрокомандой Y(7). Одновременно с записью кода команды в регистр 15 происходит запись всего слова в буферный регистр 22 блока 4.

Выполнение команд устройства происходит следующим образом.

Команда Т1 Тестовая инструкция без

передачи воздействия на контролируемый блок и без сравнения содержит одну микрокомандную последовательность Т1/1. При выполнении Т1/1 происходит запись конфигурации канала с выхода

буферного регистра 2 блока 4 в определенный регистр группы регистров 40 бпока 5. Выбор этого регистра определяется разрядами 00,...,09 регистра 22 (в формате слова команды адрес канала), поступающими на информационные входы дешифратора 39 блока 5. На его управляющий вход приходит микрокоманда Y(29), по которой на выходе деши- фратора 39, соответствующем адресу канала, появляется импульс, проходящий через второй вход элемента 38 соответствующего канала на синхровход регистра 40, и конфигурация канала (разряды 10,...,12 команды) записываются в регистр 40. По микрокоманде Y(21), поступающей на вход установки в О триггера 48 блока 5, на выходе его устанавливается нулевое значение и информация 1/0, H/L с первого и второго входов регистра 42 типа защелки не проходит через регистра 42, элемент 44, двунаправленный приемопередатчик 45 на контролируемый блок. По микрокоманде Y(15) через элемент 19 блока 3 происходит приращение на 1 счетчика 2, запись в регистр 15 кода следующей команды, запись в буферный регистр 22 блока 4 всего ко- мандного слова или аргумента команды. Последние действия по Y(15) аналогичны для всех команд.

В первой микрокомандной последовательности всех команд микрокоманда Y(31) необходима для установки выхода триггера 49 блока 5 и соответственно синхровхода регистра 46 типа защелки в состояние логической 1, чтобы результаты сравнения во всех значимых каналах () проходили на выход регистра 46 и результирующий сигнал сравнения был на выходе элемента 47. Это условие необходимо для работы команд Р, F.

Команда Т2 Тестовая инструкция с передачей воздействия на контролируемый блок и без сравнения выполняется аналогично команде Т1 за исключением того, что по микрокоманде Y(20), поступающей на вход установки в 1 триггера 48 блока 5, на выходе триггера 48 появляется логическая 1 и значения Т/О, H/L с выхода регистра 40 запишутся в регистр 42 и через элемент 44, двунаправленный приемопередатчик 45 на контролируемый блок бу-. дет выдано значение H/L канала.

0

5 О 5

0

5

Команда Тестовая инструкция с передачей воздействия на контролируемый блок и со сравнением имеет несколько микрокомандных последовательностей. Микрокоманды Y(29), Y(20) работают аналогично описанному. По микрокоманде Y(7), поступающей на синхровход триггера 13 блока 3, триггер 13 переключается и адрес следующей микрокомандной последовательности будет определяться микрокомандами Y(8)-Y(14) и выходом мультиплексора 14 до тех пор, пока в ТЗ/5 по Y(7) триггер 13 снова не переключится. В ТЗ/1 после выдачи тестового воздействия на цифровой блок по микрокоманде Y(30), которая поступает на вход Установка в 1 триггера 30 блока 4 и вход загрузки V1 счетчика 23 задержки, триггер 30 устанавливается в 1, загружается значение задержки Z из регистра 24 (.запись в регистр происходит по команде Z) и синхроимпульсами на входе счетчика 28, поступающими с выхода делителя 21 частоты блока 3, начинается режим вычитания счетчика. После его обнуления с выхода переноса сигнал поступает на вход установки в О триггера 30 блока 4, который переключается. Таким образом, на выходе триггера 30 формируется положительный импульс длительностью, соответствующей значению, записанному в регистр 24 по команде Z. Задержка Z - это задержка между выдачей тестового воздействия в команде ТЗ и сравнением отклика с эталонным значением в блоке 5. Выход триггера 30 блока 4 соединен с информационным входом мультиплексора 14 блока 3 и после разрешения отсчета задержки Z no Y(30) в ТЗ/2 проверяется условие XI до момента окончания отсчета задержки Z. Последовательности типа ТЗ/4 - промежуточные, в них осуществляется безусловный переход на соответствующие последовательности выполняемого алгоритма. Они появляю- ся вследствие принятой проверки условий ветвления, когда переходы по условиям Х(1) осуществляются инвертированием младшего разряда адреса следующей микрокомандной последовательности на входе регистра 16 блока 3.

В ТЗ/1 по микрокоманде Y(31) устанавливается триггер 49 блока 5 и регистр 46 типа защелки блока 5 устанавливается в режим передачи резуль

татов сравнения через группу япгмен- тов И 43 на входы элемента 47. Отклики с контролируемого цифрового блока проходят через двунаправленные приемопередатчики 45 на первые входы схем 41 сравнения. Таким образом, к моменту сравнения на входах регистра 46 и элемента 47 будет информация об ошибках на всех значимых каналах. Если вход имеет высокий уровень, то ре- отклик не совпал с ожидаемым, если низкий уровень, то реальный отклик совпал с ожидаемым. Для незначимых каналов третьи выходы регистров 40 находятся в низком состоянии и по- эТому на выходах групп элементов И 43 находятся низкие уровни, т.е. каналы не сравниваются с ожидаемыми откликами.

На выходе элемента 47 блока 5 формируется результирующий сигнал ошибку, который поступает на вход мультиплексора 14 блока 3. После отсчета задержки Z сигнал с инверсного выхода триггера 30 блока 4 приходит на син- }сровход триггера 49 блока 5, триггер 49 сбрасывается и результаты Сравнения всех каналов защелкиваются Ј регистре 46. Одновременно с этим р ТЗ/3 после отсчета задержки Z проверяется условие Х2 наличия сравнения в блоке 5 на мультиплексоре 14 блока 3. Если ошибки нет, по микрокоманде Y(7) в ТЗ/3 переключается триггер 13 блока 3 и процесс выполнения команд, считываемых из блока 1 памяти, продолжается. Если есть ошибка сравнения, то в ТЗ/6 по микроко-. манде Y(23), поступающей на синхро- вход триггера 36 ошибки регистра 33, триггер 36 устанавливается и индицирует состояние неисправности проверяемого цифрового блока. Поскольку результаты сравнения всех каналов защелкнуты в регистре 46 блока 5, выходы этого регистра могут быть использованы для индикации несовпавших каналов.

В команде G безусловного перехода в программе контроля при выполнении G/3 микрокоманда Y(19) поступает на вход загрузки счетчика 2 и через формирователь 12 блока 2 и элемент 19 блока 3 - на синхровход счетчика 2, что обеспечивает синхронизацию режима нагрузки. Адрес перехода на вход счетчика 2 поступает после выполнения G/2 с выхода буферного регистра 22 бло

5

0

5

ка 4. После записи этого адреса в счетчик 2 команд из блока 1 памяти выбирается команда по адресу перехода. После выполнения G/4 код новой команды записан в регистр 15 блока 3 и после выполнения G/5 начинается выборка команд от адреса перехода.

Команда Р перехода в программе контроля по совпадению выполняется аналогично команде G за исключением того, что переход по адресу перехода осуществляется в случае, если нет ошибки сравнения в блоке 5.

Команда F перехода в программе контроля по несовпадению выполняется аналогично команде Р, только переход по адресу перехода осуществляется по ошибке сравнения в блоке 5.

В команде Z задержки Z значение задержки Z с выхода буферного регистра 22 блока 4 записывается в регистр 24 задержки Z по микрокоманде Y(27), поступающей на синхровход регистра 24.

В команде S подпрограммы при выполнении микрокоманды Y(1), поступающей на синхровход регистра 25 блока 4, осуществляется запись адреса возврата с выхода счетчика 2 в регистр 25, при выполнении микрокоманды Y(19) - запись адреса подпрограммы с выхода буферного регистра 22 блока 4 в счетчик 2, а по Y(2) - запись адреса перехода в регистр 23 начального адреса.

В команде С числа повторений подпрограммы по микрокоманде Y(5), поступающей на вход загрузки счетчика 26 повторений, осуществляется запись значения числа повторений с выхода буферного регистра 22 в счетчик 26. Команда С работает в сочетании с командой 0.

Если при выполнении команды 0 выхода из подпрограммы содержимое счет- 5 чика 26 повторений не равно О, то далее снова выполняется подпрограмма, адрес которой записан в регистре 23 начального адреса следующим образом.

Микрокомандой Y(3) разрешается считывание регистра 23 начального адреса, т.е. снимается его третье.состояние и его выходы подключаются к входам счетчика 2 команд. Микрокомандой Y(19) в счетчик 2 команд записывается значение адреса подпрограммы из регистра 23 начального адреса. Микрокомандой Y(6) производится вычитание из счетчика 26 повторений. По адресу, записанному в счетчик 2 команд,

0

5

0

0

5

выполняется подпрограмма, в конце которой ставится команда 0 выхода из подпрограммы. Если при выполнении команды 0 содержимое счетчика 26 повторений не равно О, то описанный ал- горитм повторяется до обнуления счетчика 26 повторений. Если содержимое счетчика 26 равно О, выполняется возврат из подпрограммы следующим образом.

Микрокомандой Y(4) разрешается считывание регистра 25 возврата, т.е. снимается его третье состояние и его выходы подключаются к входам счетчика 2 команд. Микрокомандой Y(19) в счетчик 2 команд записывается значение адреса возврата из регистра 25 возврата. Далее по адресу возврата выполняется команда, следующая за командой S.

Аргумент команды D задержки D - это текущая задержка в ходе выполнения программы контроля именно в том месте, где она встретилась. Команда D работает аналогично команде Z, только запись значения задержки D в счетчик 27 задержки D блока 4 осуществляется по микрокоманде Y(28) с выхода буферного регистра 22. Тактирование вычи- тания из счетчика 27 осуществляется с выхода делителя 21 частоты блока 3.

Останов синхронизации памяти 17 микрокоманд блока 3 происходит следующим образом. При возникновении ошибки устанавливается триггер 36 ошибки ре- гистра 33, сигнал с выхода которого поступает на четвертый вход элемента 32 блока 4. С выхода элемента 32 низкий уровень сигнала сбрасывает тригг гер 34 работы регистра 33. На выходе элемента 32 низкий уровень появляется только после полной отработки текущей команды устройства, о чем свидетельствует высокий уровень на выходе триггера 13 блока 3 и соответственно на пятом входе элемента 32 блока 4. Низкий уровень сигнала с выхода триггера 34 регистра 33 блокирует на делителе 21 частоты блока 3 синхрониза- цию памяти 17 и процесс контроля останавливается, а выход триггера 36 индицирует состояние неисправности.

Процесс контроля также останавливается при нажатии кнопки Стоп бло- ка 6. В этом случае отрицательный импульс устанавливает триггер 35, инверсный выход которого через элемент 32 сбрасывает триггер 34 и процесс

0

5

0

5

о 45 д

5

контроля останавливается аналогично описанному выше.

Если программа контроля отработала до конца (контролируемый модуль исправен), то при выполнении команды Е Конец (ставится в конце программы контроля) вырабатывается микрокоманда Y(24), которая устанавливает триггер 37 Годен регистра 33. Выход триггера 37 индицирует состояние Го- , ден контролируемого цифрового блока.

Формула изобретения

I

i

,2

3

M/N 1/0 Н/Т,

Адрес канала

5 0 5 0

5

0

цатый памяти микрокоманд, синхровход и выход регистра внутренней последовательности микрокоманд подключены соответственно к первому выходу делителя частоты и адресному входу памяти микрокоманд, первый, второй и третий входы элемента ИЛИ соединены соответ ственно с пятнадцатым выходом памяти микрокоманд, входом начальной установки блока и выходом формирователя импульсов, вход которого подключен к первому входу условий блока, информационный вход мультиплексора проверяемых условий соединен с первым и вторым входами условий блока, выходы с , шестнадцатого по восемнадцатый памяти микрокоманд подключены к управляющему входу мультиплексора проверяемых условий, первый выход делителя частоты, соединен с входом разрешения памяти микрокоманд и вторым выходом блока, второй выход делителя частоты подключен к второму выходу блока, девятнадцатый выход памяти микрокоманд и выход элемента ИЛИ образуют первый выход блока, кроме того, выход элемента ИЛИ соединен с вторым выходом блока, выходы с двадцатого по двадцать второй памяти микрокоманд подключены к третьему выходу блока, выходы с двадцать третьего по двадцать восьмой памяти микрокоманд соединены с вторым выходом блока, двадцать девятый выход памяти микрокоманд подключен к третьему выходу блока, тридцатый выход памяти микрокоманд соединен с вторым выходом блока, а тридцать первый выход памяти микрокоманд подключен к третьему выходу блока.

Таблица 1

1

Тестовая инструкция (ТИ) без передачи и сравнения

ТИ с передачей без сравнения ТИ с передачей и сравнением Конец

Выход из подпрограммы

Сброс каналов Безусловный переход

Переход по совпадению

Переход по несовпадению

17

1661763

18 Продолжение табл.1

Х1

Х2

ХЗ

Х4 Х5 Х6

4(30) 5(47)

4(26) 4(29)

Г77

Контролируемый цифровой Фиг.1 5ло(Ц5}

Отсчет задержки Z: - задержка не отсчитана; - задержка отсчитана Анализ результата сравнения в бке 5:

- есть ошибка сравнения; - нет ошибки сравнения Анализ числа повторений в счетчике 26 повторений Отсчет текущей задержки D Лог. проверка условий для Лог. формирование младшего бита адреса микрокомандной последовательности на входе регистра 16 блока 3

Г77

олируемый ци 5ло(Ц5}

On

Г

I

Фиг, 2

иг. 3

оо

ЧО

г

чО чО

I

«1

4

1LC-

-ЧЦ,

ЕЕ:I

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1988-04-04—Подача