Изобретение относится к вычислительной технике и может быть использовано в микроЭВМ, миниЭВМ и специализированных системах обработки информации, в частности локальных вычислительных сетях с высокой скоростью обработки информации,

Известно устройство адресации для канала прямого доступа к памяти, содержащее счетчик старших разрядов адреса, счетчик младших разрядов адреса, триггер, регистр начального адреса, блок синхронизации, блок памяти свободных страниц, мультиплексор, регистр номера страницы и сумматор по модулю два. Каждому адресу блока памяти устройства соответствует адрес страницы внешней памяти, адресуемой устройством. В процессе ввода данных в режиме прямого доступа к памяти (ПДП) при заполнении текущей страницы адресуемой

памяти они помечается в блоке памяти устройства 1 по соответствующему адресу. Затем путем перебора адресов в блоке памяти устройства осуществляется поиск О по очередному адресу и формируется адрес страницы внешней памяти, куда будет продолжен ввод данных в режиме ПДП. При освобождении страницы внешней памяти устройства она помечается в блоке памяти устройства О по соответствующему адресу. Если внешняя память содержит одновременно пакеты данных для приема и для передачи, а также если пакеты данных имеют различные приоритеты обработки, то последовательность освобождения страниц не будет соответствовать последовательности их заполнения. При этом ввиду циклического характера заполнения страниц внешней памяти у внешнего устройства обV|00 Ч Ю 00 VI

работки возникают.проблемы в определении пос Шд о в 8тёТ1ь НЬЪти заполнения страниц данными Другим недостатком предложенного алгоритма работы устройства является то, что время поиска очередной 5 страни-цы внешней памяти в блоке памяти устройстрй не является фиксированной ве- личиурй, а. зависит от физической удаленно- сти ад$е фз следующей свободной страницы по бтноЙе нию.к текущей.Ю

Наиболее близким по алгоритму работы к предлагаемому изобретению является алгоритм работы контроллера ПДП БИС-ин- терфейса пакетных сетей 2511. Данный контроллер перед передачей пакета дан- 15 ных считывает управляющую информацию (атрибут) пакета данных из таблицы (списка), находящейся во внешней памяти, в свои внутренние регистры. После передачи пакета данных контроллер модифицирует 20 атрибут пакета данных в списке, помечая, что обработка данного атрибута списка завершена. После обработки последнего атрибута списка контроллетр завершает работу, когда процессор вновь разрешит 25 ему работу с новым или данным списком атрибутов пакетов данных. Снижение про- изводительности системы, связанное с необходимостью перепрограммирования контроллера ПДП после окончания обработ- 30 ки им текущего списка атрибутов пакетов Данных, является недостатком алгоритма работы данного контроллера.

Наиболее близким по структурному по- 35 строению является контроллер ПЛП 580ЕТ57, содержащий схему приема запросов, устройстве управления, запоминающее устройство, схему выработки сигналов запись-чтение, буферы данных и адреса, реги- 40 стры режима и состояния (Микросхема 580ВТ57. Техническое описание И13.480.028 ТО). Перед передачей каждого пакета данных в ЗУ контроллера ПДП процессором записывается атрибут (начальный 45 адрес памяти и длина) пакета. Окончание ь передачи данных сопровождается форми- рованием специального сигнала контроллера, после чего он ожидает обслуживания со стороны процессора. Отсутствие у контрол- 50 лера функцШ а в1чзм этического считывания атрибутов передаваемых пакетов данных из списка, находящегося в системной памяти, функции коррекции содержимого атрибутов в списке и функции перехода к обработке 55 следующего списка атрибутов по окончании тёк щегЙ ШЬ а сущбственно снижают производительность системы обработки информации, в которой используется данный контроллер.

Целью изобретения является повышение производительности системы передачи данных за счет дополнения набора функций, выполняемых контроллером ПДП, функцией автоматического считывания атрибутов передаваемых пакетов данных из списка, находящегося в системной памяти, функцией коррекции содержимого атрибутов в списке и функцией перехода к обработке следующего списка атрибутов по окончании текущего списка.

Поставленная цель достигается тем, что в контроллере ПДП, содержащем узел фиксации запросов, узел управления, узел доступа, двухпортовое ЗУ атрибутов, регистр текущего атрибута, причем первые группы входов-выходов узла фиксации запросов и узла управления, первая группа входов узла доступа подключены к шине управления устройства, первая группа выходов регистра текущего атрибута подключена к шине адреса устройства, первая группа выходов узла доступа соединена с входами адреса и управления первого порта ЗУ атрибутов, выходы узла фиксации запросов соединены с группой входов узла управления, первая группа выходов узла управления соединена с группой входов адреса и управления второго порта ЗУ атрибутов, с вторыми группами входов узла фиксации запросов и узла доступа, буфер данных, регистр установки режимов и регистр состояния заменяются компаратором и инкрементором, причем группа входов-выходов данных первого порта ЗУ атрибутов подключена к шине данных устройства, первые группы входов компаратора и инкрементора, а также третья группа входов узла доступа подключены к шине адреса устройства, второй выход узла управления, группа выходов инкрементора, первая группа входов регистра текущего атрибута соединены с группой входов-выходов данных второго порта ЗУ атрибутов, вторые группы входов регистра текущего атрибута и инкрементора соединены с первой групп-выходов узла управления, третий вход регистра текущего атрибута соединен с шиной управления устройства, вторая группа выходов регистра текущего атрибута соединена с второй группой входов компаратора, выход которого соединен с третьим входом узла фиксации запросов, третья гругтпа выходов регистра текущего атрибута соединена с четвертой группой входов узла фиксации запросов, пятая группа входов которого соединена с вторым выходом узла доступа.

Узел фиксации запросов содержит пять триггеров, четыре элемента И, элемент ИЛИ, причем выходы триггеров являются

выходами группы выходов узла, выход первого элемента И является выходом, а S-вход первого триггера и первый вход элемента ИЛИ являются входами первой группы входов-выходов узла, первые входы первого и второго элементов И являются входами четвертой группы входов узла, первый вход третьего элемента И соединен с R-входом первого триггера и является первым входом, а первые R-входы второго и третьего триггеров и первый вход четвертого элемента И являются вторыми, третьим и четвертым входами второй группы входов узла, первый R-вход и S-вход четвертого триггера, R-вход и S-вход пятого триггера являют- ся четырьмя входами пятой группы входов узла, вторые входы элемента ИЛИ и первого и четвёртого элементов И соединены между собой и являются третьим входом узла, выход элемента ИЛИ соединен с вторым вхо- дом третьего элемента И, выход которого соединен с S-входом третьего триггера и вторым входом второго элемента И, выход которого соединен с S-входом второго триггера, выход четвертого элемента И соеди- нен с вторыми R-входами второго, третьего и четвертого триггеров,

Узел управления содержит регистр и программируемую логическую матрицу (ПЛМ), причем первая группа входов и вход синхронизации регистра являются первой группой входов узла, вторая группа входов регистра является второй группой входов узла, первая, вторая и третья группы выходов регистра являются соответственно пер- вой, второй и третьей группами выходов узла, четвертая группа выходор регистра соединена с группой входов ПЛМ, выходы которой соединены с третьей группой входов регистра.

Узел доступа содержит дешифратор и мультиплексор, причем первая группа информационных входов мультиплексора является первой группой входов узла, вторая группа информационных входов мульти- плексора и группа входов адреса дешифратора являются второй группой входов узла, группа входов выбора дешифратора, третья группа информационных входов и вход адреса мультиплексора являются третьей группой входов узла, первый выход дешифратора соединен с четвертым информационным входом мультиплексора, выходы которого образуют первую группу выходов узла, вторая группа выходов дешифратора является второй группой выходов узла.

ЗУ атрибутов содержит двухпортовое регистровое ЗУ, причем первая и вторая группы входов адреса и управления портов ЗУ являются первой и второй группами входов узла, первая и вторая группы входов-выходов данных портов ЗУ являются первой и второй группами входов-выходов узла.

Компаратор содержит элемент поразрядного сравнения, причем первая и вторая группы входов элемента являются группами входов узла, и выход элемента является выходом узла.

Регистр текущего атрибута содержит регистр с выходами на три состояния, причем группа информационных входов регистра является первой группой входов узла, вход синхронизации и вход управления третьим состоянием регистра является второй группой входов узла, а три группы выходов регистра являются группами выходов узла.

Инкрементор содержит преобразователь кодов (ПЗУ), причем первая группа информационных входов ПЗУ является первой группой входов узла, вторая группа информационных входов и вход выбора ПЗУ являются второй группой входов узла, а выходы ПЗУ являются группой выходов узла.

Сущность изобретения состоит в том, что оно позволяет повысить производительность системы передачи данных за счет дополнения набора функций, выполняемых контроллером ПДП, функцией автоматического считывания атрибутов блоков пакетов данных из списка, находящегося в системной памяти, функцией коррекции содержимого атрибутов в списке и функцией перехода к обработке следующего списка атрибутов после окончания текущего списка. Передаваемый или принимаемый пакет данных в общем случае может быть разбит на части и занимать в памяти несколько блоков. Для каждого блока памяти формируется атрибут, содержащий поля НАБ (начальный адрес блока), КАБ (конечный адрес блока) и МД (модификатор), МД содержит бит ПДП (последний блок пакета) и бит ПБС (последний блок списка). Список атрибутов блоков, создаваемый процессором в системной памяти, за атрибутом последнего блока данных может содержить атрибут списка, куда необходимо осуществить переход контроллеру ПДП после завершения обработки им данного списка. Структура атрибута списка аналогична структуре атрибута блока. Сначала процессор вводит в ЗУ атрибутов устройства атрибуты списка и первого блока в-списке, а затем разрешает передачу данных. В процессе выполнения цикла передачи данных узел управления осуществляет считывание из ЗУ атрибутов атрибута блока, запись его в регистр текущего атрибута, формирование сигналов адреса и управления в соответствующие шины

устройства, преобразование полей НАБ и МД атрибута в ЗУ атрибутов с помощью инкрементора, сравнение полей НАБ и КАБ с помоа1ью компаратора. При сравнении полей НАБ и КАБ компаратором или при поступлении сигнала ПЦ (последний цикл) в процессе приема пакета данных узел фиксаций запросов формирует запрос на замену атрибута блока в ЗУ атрибутов, при этом, если поле МД содержит установленный бит ПБС, то узел фиксации запросов дополнительно формирует запрос на замену атрибута списка в ЗУ атрибутов, В процессе замены атрибутов в ЗУ атрибутов устройство осуществляет запись модифицированного атрибута блока из ЗУ атрибутов обратно в текущий список, вводит в ЗУ атрибутов из текущего списка атрибут нового списка (если установлен запрос на ввод списка), вводит из списка атрибут блока. Если бит ПЕС пиля МД не установлен, то после обработки последнего атрибута блока списка устройство осуществляет запись модифицированного атрибута блока из ЗУ атрибутов в текущий список и прекращает работу, ожидая программирования со стороны процессора,

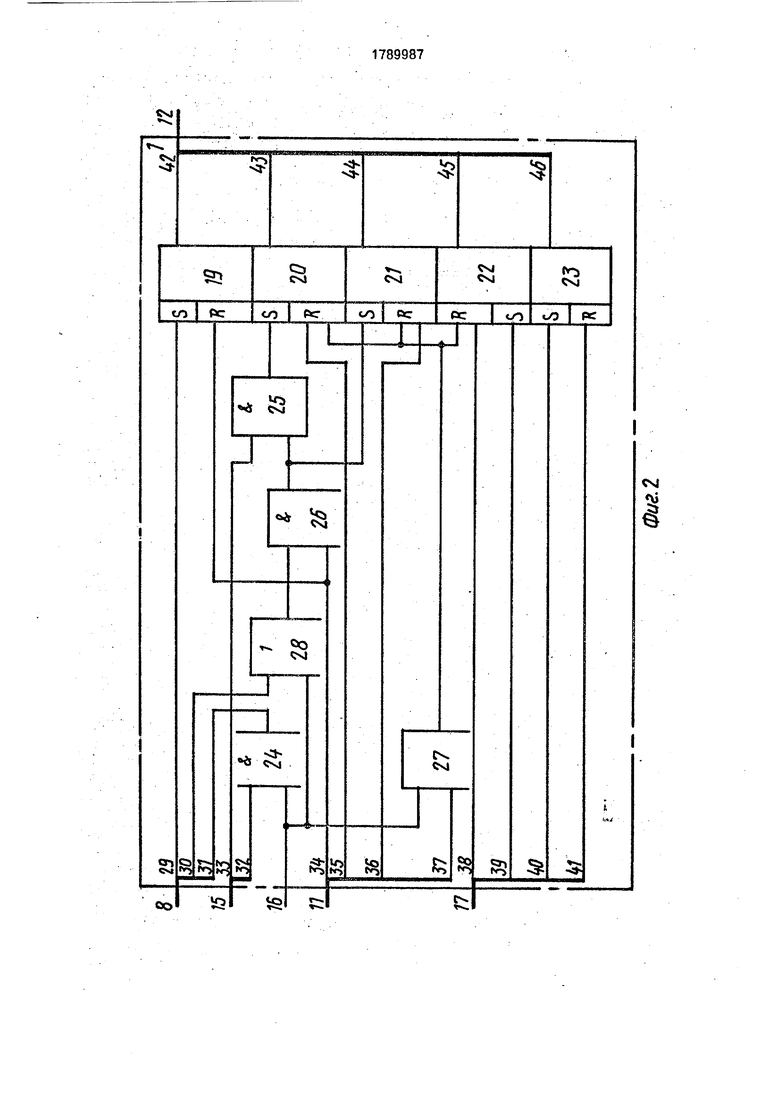

На- фиг. 1 представлена структурная схема контроллера ПДП; на фиг. 2 -функциональная схема узла фиксации запросов; на фиг. 3 - функциональная схема узла управления; на фиг. 4 - функциональная схема узла доступа; на фиг. 5 - временная диаграмма выполнения цикла передачи данных; на фиг. 6 - временная диаграмма замены атрибута блока; на фиг. 7 - временная диаграмма1 замены атрибутов списка и блока; на фиг, 8 - временная диаграмма окончания работы контроллера ПДП при завершении списка. : .

Контроллер ПДП содержит (см. фиг. 1) узел.1 фиксации запросов, узел 2 управления, узел 3 доступа, запоминающее устройство 4 атрибутов, компаратор 5, регистр 6 текущего атрибута, йнкрвенатор 7, шину 8 управления, шину 9 адреса, шину 10 данных, группу выходов 11 управления, группу выходов 12 запроса, группу выходов 13 адреса и управления, группу выходов 14 конечного адреса, группу выходов 15 модификатора, выход;Тб сравнения, группу выходов Т7 установки режима, внутреннюю шину 18 данных.

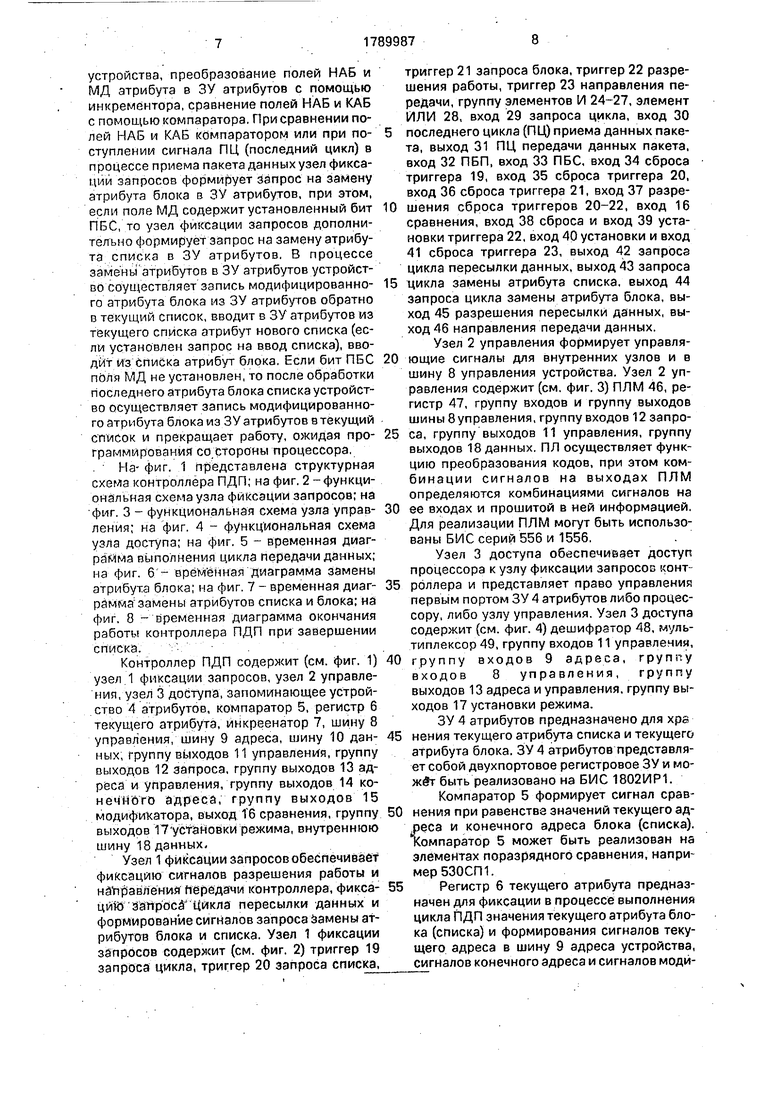

Узел 1 фиксации запросов обеспечивает фиксацию сигналов разрешения работы и направления передачи контроллера, фикса- цйго Sari роса Цикла пересылки данных и формирование сигналов запроса замены атрибутов блока и списка. Узел 1 фиксации запросов содержит (см. фиг. 2) триггер 19 запроса цикла, триггер 20 запроса списка,

триггер 21 запроса блока, триггер 22 разрешения работы, триггер 23 направления передачи, группу элементов И 24-27, элемент ИЛИ 28, вход 29 запроса цикла, вход 30

последнего цикла (ПЦ) приема данных пакета, выход 31 ПЦ передачи данных пакета, вход 32 ПБП, вход 33 ПБС, вход 34 сброса триггера 19, вход 35 сброса триггера 20, вход 36 сброса триггера 21, вход 37 разре0 шения сброса триггеров 20-22, вход 16 сравнения, вход 38 сброса и вход 39 установки триггера 22, вход 40 установки и вход 41 сброса триггера 23, выход 42 запроса цикла пересылки данных, выход 43 запроса

5 цикла замены атрибута списка, выход 44 запроса цикла замены атрибута блока, выход 45 разрешения пересылки данных, выход 46 направления передачи данных.

Узел 2 управления формирует управля0 ющие сигналы для внутренних узлов и в шину 8 управления устройства. Узел 2 управления содержит (см. фиг. 3) ПЛМ 46, регистр 47, группу входов и труппу выходов шины 8 управления, группу входов 12 запро5 са, группу выходов 11 управления, группу выходов 18 данных. ПЛ осуществляет функцию преобразования кодов, при этом комбинации сигналов на выходах ПЛМ определяются комбинациями сигналов на

0 ее входах и прошитой в ней информацией. Для реализации ПЛМ могут быть использованы БИС серий 556 и 1556.

Узел 3 доступа обеспечивает доступ процессора к узлу фиксации запросов конт5 роллера и представляет право управления первым портом ЗУ 4 атрибутов либо процессору, либо узлу управления. Узел 3 доступа содержит (см. фиг. 4) дешифратор 48, мультиплексор 49, группу входов 11 управления,

0 группу входов 9 адреса, группу входов 8 управления, группу выходов 13 адреса и управления, группу выходов 17 установки режима.

ЗУ 4 атрибутов предназначено для хра

5 нения текущего атрибута списка и текущего атрибута блока. ЗУ 4 атрибутов представляет собой двухпортовое регистровое ЗУ и мо- жбт быть реализовано на БИС 1802ИР1. Компаратор 5 формирует сигнал срав0 нения при равенстве значений текущего адреса и конечного адреса блока (списка). Компаратор 5 может быть реализован на элементах поразрядного сравнения, например 530СП1.

5 Регистр 6 текущего атрибута предназначен для фиксации в процессе выполнения цикла ПДП значения текущего атрибута блока (списка) и формирования сигналов текущего адреса в шину 9 адреса устройства, сигналов конечного адреса и сигналов модйфикатора. Регистр б текущего атрибута может быть реализован на регистрах, имеющих выходы на три состояния, например 580ИР82.

Инкрементор 7 формирует модифици- рованное значение текущего адреса блока (списка) в зависимости от комбинации сигналов шины 9 адреса и сигналов на входах управления узла. Инкременатор 9 представляет собой преобразователь кодов и может быть реализован на БИС 556РТ18. Устройство работает следующим образом.

Системная память, адресуемая устройству, логически разбита на блоки, предназначенные для хранения данных и списков атрибутов блоков передаваемых или принимаемых пакетов данных, причем пакет данных может размещаться в нескольких произвольных блоках памяти. Для каждого блока памяти формируется атрибут, содер- жащий поля НАБ (начальный адрес блока), КАБ (конечный адрес блока) и МД (модификатор), МД содержит бит ПБП (последний блок списка). Списки приема (передачи) содержит последовательность атрибутов бло- ков для принимаемых (передаваемых) пакетов данных и могут размещаться в произвольных блоках памяти. Последний блок пакета данных имеет в МД атрибута блока установленный бит ПБП, Для каждого спи- ска формируется атрибут, содержащий поля НАС (начальный адрес списка) и КАС (конеч- ный адрес списка). Для связывания списков между собой в текущем списке за последним атрибутом блока данных записывается атрибут очередного списка, причем МД последнего атрибута блока данных должен иметь установленный бит ПБС.

Сигналом СБРОС шины 8 устройство переводится в пассивное состояние, при этом узел 2 прекращает формировать активные уровни сигналов в шину 8 управления и сигналами группы выходов 11 устанавливает триггеры 19-22 узла 1 в состояние О.

В процессе инициализации устройства процессор, используя шины 8-10, узел 3 и шину 13 записывает в ЗУ 4 атрибуты списка и первого блока данных в этом списке, а затем через узел 3 и группу выходов 17 определяет направление передачи и разреша- ет работу устройству, устанавливая триггеры 22, 23 узла 1.

В процессе работы устройство формирует 4 типа циклов ПДП: цикл пересылки слова данных, цикл замены атрибута блока, цикл замены атрибута списка, цикл конца списка. Между циклами ПДП устройство находится в пассивном состоянии. Каждый цикл ПДП инициируется сигналом запроса шины 8 (вход 29), при этом триггер 19 узла 1

устанавливается в состояние 1, транслируя сигнал запроса через выход 42 группы выхода 12 в узел 2.

Процесс выполнения цикла пересылки слова данных состоит (см. фиг, 5) из двух, тактов. В такте Т1 узел 2, формируя в шину 8 сигнал запроса захвата шин (ЗЗХВ), ожидает поступление по шине 8 сигнала подтверждение захвата (ПЗХВ) и одновременно, формируя сигналы группы выходов 11, считывает атрибут блока из ЗУ 4 и, используя второй порт ЗУ 4 и шину 18, записывает его в регистр 6. Активный уровень сигнала ПЗХВ шины 4J осуществляет включение выходов регистра 6 в активное состояние, при этом в шину 9 формируется текущий адрес (ТА) блока данных. Получив сигнал ПЗХВ. узел 2 в такте Т2 одновременно осуществляет: формирование в зависимости от направления передачи данных пар сигналов управления СЧТ ЗУ, ЗПС ВУ или СЧТ ВУ, ЗПС ЗУ в шину 8, запись в поле НАБ атрибута блока значений ТА очередного цикла пересылки данных, полученного путем преобразования ТА шины 9 инкремен- тором 7, установку в состояние О триггера 19 узла 1, формируя сигнал 34 группы выходов 11. Одновременно компаратор 5 осуществляет сравнение значения ТА шины 9 со значением КАБ регистра Нив случае их равенства формирует в узел 1 сигнал сравнения 16. После окончания такта Т2 узел 2 прекращает формирование сигналов ЗЗХВ, СЧТ ЗУ, ЗПС ВУ, СЧТ ВУ, ЗПС ЗУ шины 8. Окончание сигнала ПЗХВ шины 8 переводит выходы регистра 6 в пассивное состояние. Такты Т1 и Т2 цикла ПДП могут содержать более одного периода синхронизации (СИ), если имеются задержки в формировании сигнала ПЗХВ (такт Т1) или требуется удлинить фазу пересылки данных (такт Т2) согласования скоростей работы ЗУл ВУ системы.

Процесс выполнения цикла замены атрибута блока состоит (см. фиг. 6) из 6 тактов, В тактах Т1, Т2 осуществляется пересылка слова данных блока, в тактах ТЗ, Т4 - запись модифицированного атрибута текущего блока из ЗУ 4 в список, в тактах Т5, Т6 - считывание атрибута очередного блока из списка в ЗУ 4 устройства. Отличие выполнения тактов Т1, Т2 от соответствующих тактов цикла пересылки слова данных состоит в том, что в такте Т2 устанавливается в состояние 1 триггер 21 узла 1, формируя на выходе 44 группы выходов 12 в узел 2 сигнал запроса на замену текущего атрибута блока в ЗУ 4. Триггер 21 устанавливается в состояние 1 в следующих случаях: либо достигнут конец текущего блока (на входе 16 узла

1 присутствует сигнал сравнения); либо достигнут конец принимаемого пакета данных (на входе 30 узла 1 присутствует сигнал ПЦ приема), при этом узел 2 устанавливает бит П БП поля МД при коррекции текущего атрибута блока в ЗУ 4; либо достигнут конец передаваемого пакета, при этом на выходе элемента И 24 узла 1 формируется сигнал ПЦ передачи (в поле МД установлен бит ПБП, поступающий на вход 32 узла). Процесс выполнения тактов ТЗ, Т4 и Т5, Тб аналогичен процессу выполнения тактов Т1.Т2. В тактах ТЗ, Т5 узел 2 осуществляет пересылку из ЗУ 4 в регистр 6 атрибута текущего списка, В такте Т4 узел 2 одновременно осуществляет: модификацию поля НАС атрибута списка в ЗУ атрибутов 4 (используется йнкрементор 7, шина 18 и второй порт ЗУ 4); запись атрибута блока из ЗУ 4 в список (используются первый порт ЗУ 4, шина 10 и узел 3, при этом узел 3 осуществляет коммутацию сигналов группы входов 11 в группу выходов 13); формирование сигнала ЗПС ЗУ в шину 8; формирование сигнала разрешения сброса триггеров 20-22 узла 1 (вход 37). В такте Тб узел 2 одновременно осуществляет: формирование сигнала СЧТ ЗУ в шину 8; считывание атрибута блока из списка в ЗУ 4; формирование сигнала сброса триггера 21 узла 1 (вход 36). После окончания такта Тб устройство переходит в пассивное состояние. .. . ..-.. .

Процесс выполнения цикла замены атрибута списка состоит (см. фиг. 7) из 8 тактов, В тактах.Т1, Т2 осуществляется пересылка слова данных блока, в тактах ТЗ, Т4 - запись модифицированного атрибута теку щего блока из ЗУ 4 в список, в тактах Т5, Тб - считывание атрибута очередного списка из текущего списка в ЗУ 4, а тактах Т7, Т8 - считывание первого атрибута блока нового списка в ЗУ 4, Отличие выполнения тактов Т1, Т2 от соответствующих тактов цикла замены атрибута блока, описанного

выше, состоит в том, что в такте Т2 устанавливается в состояние 1 триггер 20 узла 1, формируя на выходе 43 группы выходов 12 в узел 2 сигнал запроса на замену текущего

атрибута списка в ЗУ 4. Триггер 20 устанавливается в состояние 1 одновременно с триггером 21 в том случае, если МД текущего блока содержит установленный бит ПБС, поступающий на вход 33 узла 1. Такты ТЗ, Т4

данного цикла соответствуют тактам ТЗ, Т4 цикла замены атрибута блока. Такты Т5, Тб данного цикла аналогичны тактам Т5, Тб цикла замены атрибута блока за исключением того, что в такте Тб узел 2 считывает из

текущего списка в ЗУ 4 атрибут очередного списка и формирует сигнал сброса триггера 20 узла 1 (вход 35). Такты Т7, Т8 данного цикла соответствуют тактам Т5, Тб цикла замены атрибута блока.

Цикл конца списка выполняется устройством в том случае, если текущий список не содержит атрибут очередного списка. Процесс выполнения цикла замены атрибута

блока состоит (см. фиг. 8) из 4 тактов. В тактах Т1, Т2 осуществляется пересылка слова данных блока, в тактах ТЗ, Т4 - запись модифицированного атрибута текущего блока из ЗУ 4 в список. Такты Т1, Т2 данного

цикла соответствуют тактам 71, Т2 цикла замены атрибута блока. Такты ТЗ, Т4 данного цикла аналогичны тактам ТЗ, Т4 цикла замены атрибута блока за исключением того, что в такте Т4 значение ТА на шине 9

совпадает со значением поля КАС группы выходов 14 регистра 6, при этом компаратор 5 формирует сигнал сравнения на выходе 16. При совпадении сигнала сравнений (вход 16) и сигнала разрешения сброса триггеров 20-22 (вход 37) узла 1 сигналом с выхода элемента И 26 устанавливаются а состояние О триггеры 20-22, при этом после окончания такта Т4 устройство переходит в пассивное состояние.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство сопряжения с памятью | 1985 |

|

SU1262515A1 |

| Устройство для ввода информации | 1987 |

|

SU1531082A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

Изобретение относится к вычислительной технике и обеспечивает управление передачей данных между внешним устройством и системой памятью, логически разбитой на блоки, в соответствии со списком или сцепленными списками атрибутов блоков, подготавливаемыми процессором в системной памяти. Целью изобретения является повышение производительности системы передачи данных за счет дополнения набора функций, выполняемых контроллером ПДП, функциями автоматического считывания, атрибутов передаваемых пакетов данных из списка, находящегося в системной памяти, и коррекции содержимого атрибутов по окончании текущего списка. Контроллер ПДП содержит узел фиксации запросов, узел управления, узел Доступа, ЗУ атрибутов, компаратор, регистр текущего атрибута, инкрементор. 8 ил. у Ё

Формула изобретения Контроллер прямого доступа к памяти; содержащий узел фиксации запросов, узел управления, узел доступа, двухпортовое запоминающее устройствр атрибутов, регистр текущего атрибута, причем первые группы входов-выходов узла фиксации запросов и узла управления, первая группа входов узла доступа подключены к шине управления контроллера, первая группа выходов регистра текущего атрибута подключена к шине

адреса контроллера, первая группа выходов узла доступа соединена с входами адреса и управления первого порта запоминающего устройства атрибутов, выходы узла фиксации запросов соединены с группой входов узла управления, первая группа выходов узла управления соединена с группой входов адреса и управления второго порта запоминающего устройства атрибутов, с вторыми группами входов узла фиксации запросов и узла доступа, отличающийся тем, что,

с целью повышения производительности, в него введены компаратор и инкрементор, причем группа входов-выходов данных первого порта запоминающего устройства атрибутов подключена к шине данных контроллера, первые группы входов компаратора и инкрементора, а также третья группа входов узла доступа подключены к шине адреса контроллера, второй выход узла управления, группа выходов инкрементора, первая группа входов регистра текущего атрибута соединены с группой входов-выходов данных второго порта запоминающего устройства атрибутов, вторые группы входов регистра текущего атрибута и инкрементора соединены с первой группой выходов узла управления, третий вход регистра текущего атрибута соединен с шиной управления контроллера, вторая группа вых одов регистра текущего атрибута соединена с второй группой входов компаратора, выход которого соединен с третьим входом узла фиксации запросов, третья группа выходов регистра текущего атрибута соединена с четвертой группой входов узла фиксации запросов, пятая группа входов которого соединена с вторым выходом узла доступа.

CM

I

Фие.3

ФигЛ

Оь

4s VJ:

j

J

и

§ § S Ш Ь{ s {$ &

S

S

И66Ш

S

a

3

2

Ч

a

s VJ

| Устройство адресации для канала прямого доступа к памяти | 1985 |

|

SU1283763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Контроллер ПДП | |||

| Дисковая паровая турбина | 1922 |

|

SU580A1 |

Авторы

Даты

1993-01-23—Публикация

1991-01-03—Подача