11363260

Изобретение относится к вычислительной технике и может быть использовано как автономно, так и в кас прямыми и инверсными выходами, входы 52-54.

Блок 6 итераций содержит элемент честве спецпроцессора для универсаль- с 55 задержки, первый умножитель 56j

ной ЦВМ.

Целью изобретения является увеличение точности и быстродействия.

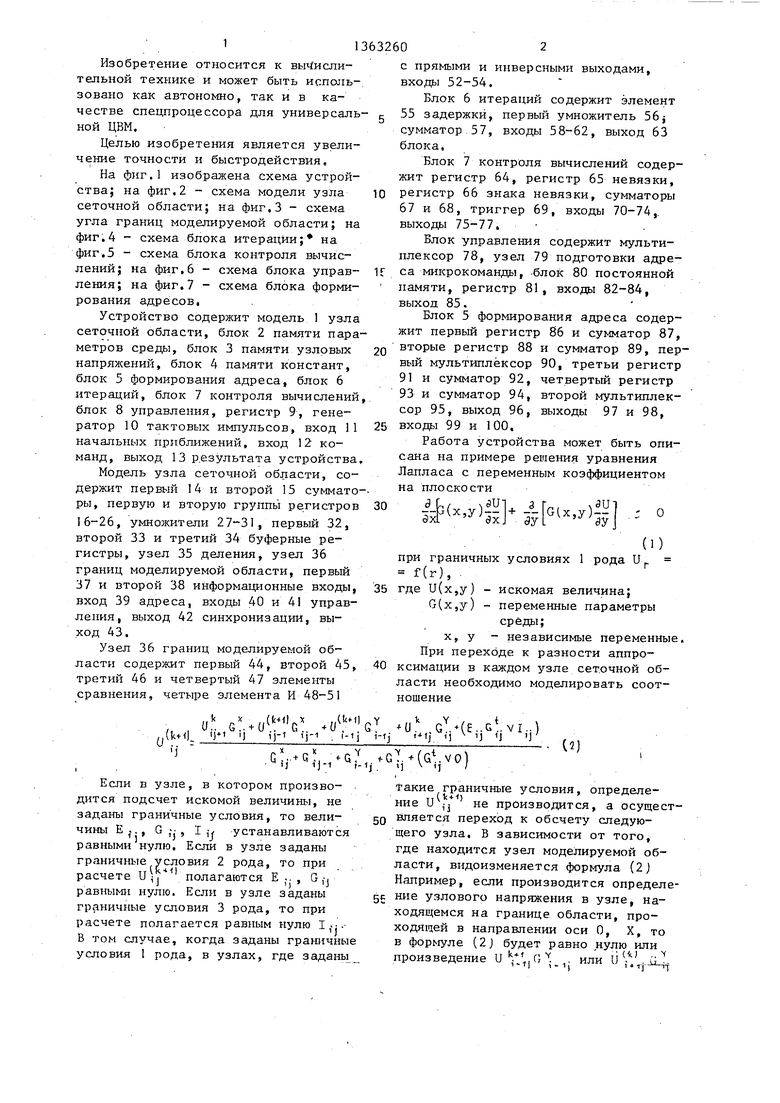

На фнг.1 изображена схема устройства; на фиг,2 - схема модели узЛа сеточной области; на фиг.З - схема угла границ моделируемой области; на фиг.4 - схема блока итерации; на фиг.З - схема блока контроля вычиссумматор 57, входы 58-62, выход 63 блока.

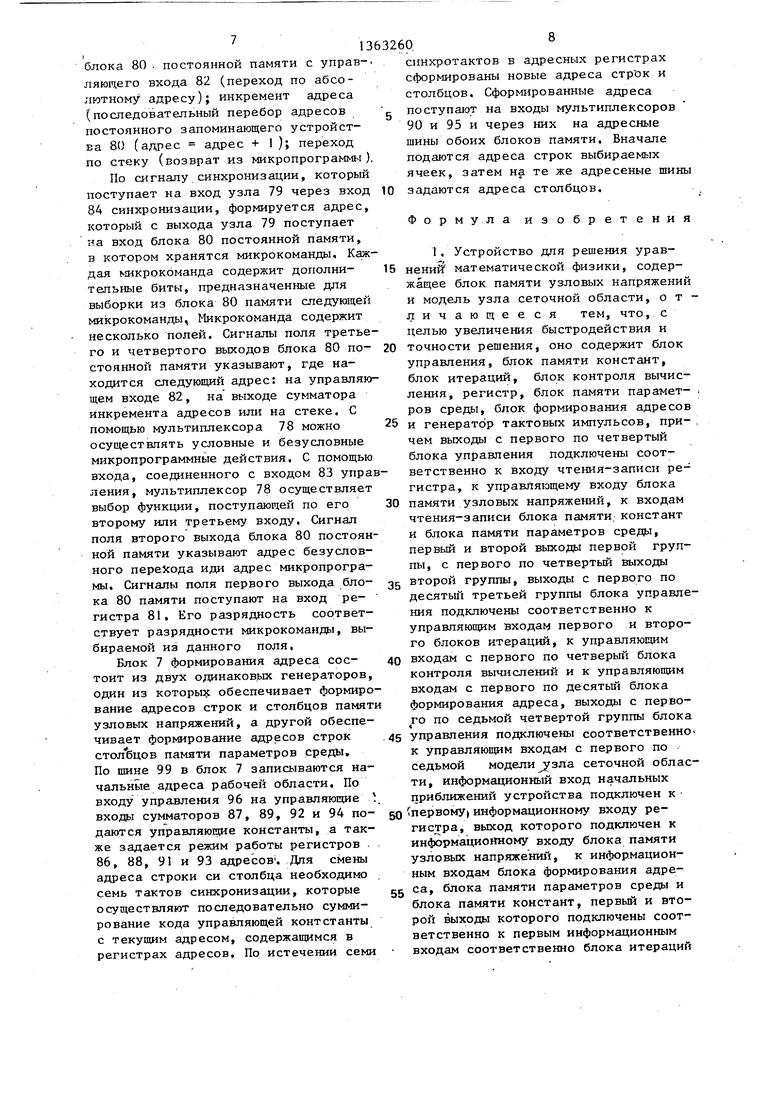

Блок 7 контроля вычислений содержит регистр 64, регистр 65 невязки, 10 регистр 66 знака невязки, сумматоры 67 и 68, триггер 69, входы 70-74,. выходы 75-77,

Блок управления содержит мультиплексор 78, узел 79 подготовки адрелений; на фиг,6 - схема блока управ- 1Г са микрокоманды, .блок 80 постоянной ления; на фиг,7 - схема блока форми- памяти, регистр 8, входы 82-84,

рования адресов.

Устройство содержит модель узла сеточной области, блок 2 памяти параметров среды, блок 3 памяти узловых 20 напряжений, блок А памяти констант, блок 5 формирования адреса, блок 6 итераций, блок 7 контроля вычислений, блок 8 управления, регистр 9, геневыход 85.

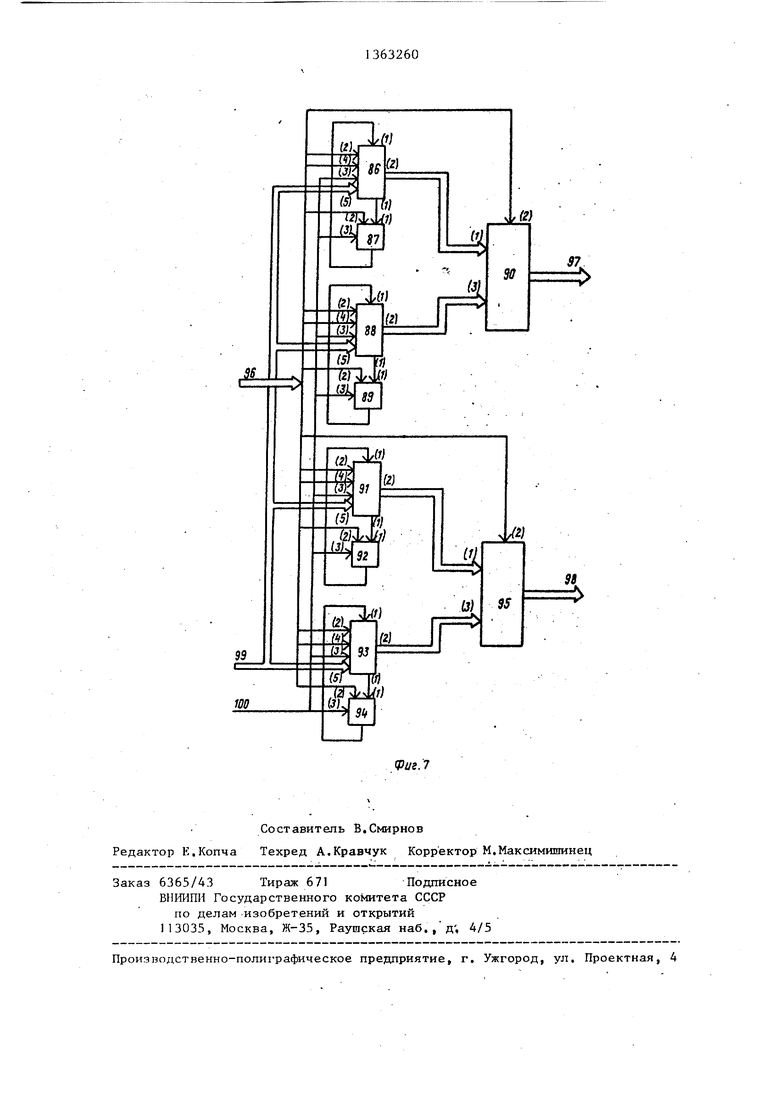

Блок 5 формирования адреса содержит первый регистр 86 и сумматор 87, вторые регистр 88 и сумматор 89, первый мультиплексор 90, третьи регистр 91 и сумматор 92, четвертый регистр 93 и сумматор 94, второй мультиплексор 95, выход 96, выходы 97 и 98,

ратор 10 тактовых импульсов, вход 11 25 входы 99 и 100, начальных приближений, вход 12 ко- Работа устройства может быть опи- манд, выход 13 р.езультата устройства. Модель узла сеточной области, содержит первый 14 и второй 15 суммато-- ры, первую и вторую группы регистров 30 16-26, умножители 27-31, первый 32, второй 33 и третий 34 буферные регистры, узел 35 деления, узел 36 границ моделируемой области, первый

37 и второй 38 информационные входы, 35 где U(x,y) - искомая величина; вход 39 адреса, входы 40 и 41 управ- G(x,y) - переменные параметры ления, выход 42 синхронизации, выход 43.

сана на примере решения уравнения Лапласа с переменным коэффициентом на плоскости

)a 5lh--)f -- °

(1)

при граничных условиях 1 рода U,. f(r).

X,

среды; - независимые переменные,

Узел 36 границ моделируемой области содержит первый 44, второй 45, 40 ксимации в каждом узле сеточной об- третий 46 и четвертый 47 элементы сравнения, четыре элемента И 48-51

ласти необходимо моделировать соотношение

G.. . G и .G(E,a;.vi,)

1 1)-1 ij-l : l-lj 1-tj . Ч Ч Ч J

G.-+G, Q tcT.f()

M 1)-1 1-1 . Ч Л Ч

Если в узле, в котором произво- дится подсчет искомой величины, не заданы граничные условия, то величины Е .., G , I ,-у устанавливаются равными нулю. Если в узле заданы граничные условия 2 рода, то при расчете U,-j полагаются Е ;. , G ,-j равными нулю. Если в узле заданы граничные условия 3 рода, то при расчете полагается равным нулю ,( В том случае, когда заданы граничные условия 1 рода, в узлах, где задань1

сумматор 57, входы 58-62, выход 63 блока.

Блок 7 контроля вычислений содержит регистр 64, регистр 65 невязки, регистр 66 знака невязки, сумматоры 67 и 68, триггер 69, входы 70-74,. выходы 75-77,

Блок управления содержит мультиплексор 78, узел 79 подготовки адревыход 85.

Блок 5 формирования адреса содержит первый регистр 86 и сумматор 87, вторые регистр 88 и сумматор 89, первый мультиплексор 90, третьи регистр 91 и сумматор 92, четвертый регистр 93 и сумматор 94, второй мультиплексор 95, выход 96, выходы 97 и 98,

входы 99 и 100, Работа устройства может быть опи-

сана на примере решения уравнения Лапласа с переменным коэффициентом на плоскости

)a 5lh--)f -- °

(1)

при граничных условиях 1 рода U,. f(r).

x,y) - искомая величина; x,y) - переменные параметры

X,

среды; - независимые переменные,

При переходе к разности аппроксимации в каждом узле сеточной об-

ласти необходимо моделировать соотношение

(2)

Такие граничные условия, определение не производится, а осуществляется переход к обсчету следующего узла, В зависимости от того, где находится узел моделируемой области, видоизменяется формула (2J Например, если производится определение узлового напряжения в узле, находящемся на границе области, проходящей в направлении оси О, X, то в формуле (2) будет равно нулю или

; (1

произведение UVijC ;.ij -

и т.д. Вычисление по формуле (2) выполняется в модели 1 узла сеточной области, причем изменение конфигурации границ моделируемой области в зависимости от вида граничных условий и местонахождения узла в моде- Л1 руемой сеточной области выполняется блоком фиксации границ моделируемой области. Информация об узлах (узловое напряжение и параметры среды ) находится в блоке 3 памяти узловых напряжений и в блоке 2 памяти параметров среды. Информация о форме моделируемой сеточной облатси и огра ничных условиях находится в блок 2 памяти параметров среды. Управление моделью узла сеточной области осущесвляется с помощью блока 8 управления .и блока фиксации границ моделируемой области модели 1 узла сеточной области, которые устанавливают требуемую конфигурацию модели 1 узла сеточной области. После получения величины узлового напряжения по формуле (2) она по- падает на вход блока контроля вычислений, а из него в блок 6 организации метода итераций и через регистр 9 о6щ;егр назначения записывается в блок 3 памяти узловых напряжений,

Модель узла сеточной области работает следующим образом,

С помощью модели узла сеточной области аппаратно реализуется формула (2) с учетом рода граничных уело- ВИЙ и местонахождения узла в моделируемой сеточной области. Информация о величинах параметров среды Glf. f GV-.,|G i l-Ti также о величинах , E ,. , I .- , задающих род граничных условий, поступает по. информационному входу 37 на регистры 16-19,24-26 соответственно. Информация о вепичи-j н ах узловых напряжений U,-j+, , U ,4. и . . 9 т- Т- поступает по информа- ционному входу 38 на регистры 20-23 соответственно. Информация с выходов регистров 16-19 и 24 поступает на входы сумматора 15 и на первые входь. умножителей 27-31 соответственно, С выходов регистров 20-23 информация поступает на входы умножителей 27-30 соответственно, С выхода регистра 25 информация поступает на вход умножителя 31,

С выходов умножителей 27-30 парные произведения поступают на входы . сумматора 14, При задании граничных условий 2 рода прямо на вход сумматора 14 поступает информация с выхода регистра 26 о величине 1.. , При задании граничных условий 3 рода на вход сумматора 14 с выхода умножителя 31 подается парное произведение G , Е .. . С выхода сумматора 14 информация поступает в регистр 32, С выхода сумматора 15 сумма параметров среды поступает на входе регистра 33, С выходов регистров 32 и 33 информация поступает на входы . узла 35 деления, в котором формируется значения искомой величины узлового напряжения U. С выхода зла 35 искомая величина U tj поступает в регистр 34 и далее на информационный выход 43,

Упра вление моделью узла сеточной области осуществляется узлом 36 границ моделируемой области, который работает следующим образом. На одни, входы элементов 44-47 сравнения фиксируются в виде констант адреса верхней граничной строки моделируемой области, нижней граничной строки моделируемой области, левого граничног столбца моделируемой области и правого граничного столбца моделируемой области соответственно, С блока 5 формирования адреса через вход 52 текущего адреса на другие входы зле- ментов 44-47 сравнения поступает адрес обсчитываемого искомого узла. При совпадении, например, текущего адреса строки искомого узла с зафик сированным адресом верхней граничной строки элемент 44 сравнения выставляет сигнал блокировки на вход элемента И 48, на первый вход которой поступает сигнал с блока 8 управления, которьй; управляет записью информации ..,- :, U.f-ij в регистры 19 и 23, В результате блокировки сигнала управления новая информация в регистры 19 и 23 не поступает, а старая обнуляется, С выхода умножителя 30 на вход сумматора 14 поступает нулевое значение. Таким образом парное произведение Ui-ijGX . равно нулю, В том случае, когда с фиксированными адресами граничной строки и граничного столбца совпадает текущий адрес и строки, и столбца искомого узла (узел находится в углу моделируемой области), блокируется запись в виде пары регистров, и тогда два парных|произведения равны нулю, В том случае, когда текущий

адрес не совпадает с фиксированными адресами, осуществляется полный обсчет узла. Регистры 24-26 рода граничных условий управляются непосредственно блоком 8 управления. При наличии в памяти граничных условий 1, 2 или 3 рода блок управления выдает сигнал разрешения записи в соответствующий регистр.

Блоки 6 и 7 итераций и контроля вычислений работают следующим образ-ом.

Вид итеративного процесса,,в соответствии с которым решается задача (,1), задается в блоке организации метода итераций, В зависимости от того, принимается ли метод итерации по Зейделю или релаксационный метод блок организации метода итераций

работает по-разному. Опишем функционирование блока организации метода итераций на примере осуществления итерации по методу верхней релаксации. С информационного выхода 43 модели узла сеточной области каждое полученное по формуле (2) значение узлового напряжения U , поступает на информационный вход 72 блока конроля вычислений. На информационный вход 71 поступает значение узлового напряжения U ,.V, полученное на предыдущей итерации. В регистре 64 параллельная информация пр.еобразуется в

последовательную и с его выхода по- лизуется итерационный метод по Зейступает на первый вход сумматора 67, на второй вход которого поступает информация с входа 72. Б сумматоре 67 вычисляется величина текущей невязки

Г -

k-n) (k) fj - и ij

40

С выхода сумматора 67 величина текущей невязки поступает в регистр 65 невязки, а с него - на первьй вход сумматора 68, на второй вход которого с входа 73 поступает значение заданной невязки Ej- сумматоре. 68 производится оценка величины невязки текущей JV по сравнению с заданной невязкой 3. Режимом работы сумматора 68 (сложения или вычитания )управляет знак текущей невязки . который к моменту анализа находится в регистре 66 знака невязки. Когда достигнута требуемая точность получения величины узловых напряжений во всех узлах моделируемой области, сигнал с выхода сумматора 68 взводит триггер 69. Триггер 69 выделю.

Блок 8 управления выполняет функцию микропрограммного управления вы полнением операций в устройстве в за висимости от задаваемой команды. В блоке 80 постоянной памяти записываются подпрограммы работы устройства. Эти подпрограммы ввода узловых напряжений U, параметров сред G, 45 констант, заданной невязки f и релаксационного параметра ч конфигура ции моделируемой области, а ,также подпрограммы итераций и вывода просчитанных узловых напряжений U. Функцию генерации очередных адресов микрокоманд в блоке 80 постоянной памяти выполняет узел 79 подготовки адреса микрокоманды. Адрес стартовой микрокоманды нужной подпрограммы вво дится на первый вход узла 79 через управляюгдий вход 82. Узел 79 выполняет три различных способа формирования адреса микрокоманд: непосредственное задание адреса микрокоманды

50

55

дает команду в блок 8 управления на остановку вычислений. Полученное в блоке контроля вычислений значение текущей невязки передается через вход 60 на первый вход умножителя 56 блока итераций. На второй вход умножителя 56 с входа 61 поступает релаксационный параметр ц. Полученное на выходе умножителя 56 произведение

с (М1) „

t ,-j- 1 поступает на вход сумматора 57. Па вход элемента 55 задержки через информационный вход 59 поступает значение узлового напряжения U ,. ; полученное в результате предыдущей итерации. С выхода элемента задержки информация поступает на вход сумматора 57. В сумматоре 57 осуществляется коррекция величины узлового напряжения, в результате чегр получает искомую величину узлового напряжения

.г; -1.. .

с выхода сумматора 57 через инфор- мационньш выход 63 блока итерацир искомое узловое напряжение записывается в блок 3 памяти узловых напряжений. При вычислении величины напряжения в следующем узле сеточной области процесс вычисления повторяется. Если релаксационньй параметр принимает значение 1 J 2 , то реализуется итерационный метод последовательной верхней релаксации. Если релаксационный параметр О, реа0

делю.

Блок 8 управления выполняет функцию микропрограммного управления выполнением операций в устройстве в зависимости от задаваемой команды. В блоке 80 постоянной памяти записываются подпрограммы работы устройства. Эти подпрограммы ввода узловых напряжений U, параметров сред G, 5 констант, заданной невязки f и релаксационного параметра ч конфигурации моделируемой области, а ,также подпрограммы итераций и вывода просчитанных узловых напряжений U. Функцию генерации очередных адресов микрокоманд в блоке 80 постоянной памяти выполняет узел 79 подготовки адреса микрокоманды. Адрес стартовой микрокоманды нужной подпрограммы вводится на первый вход узла 79 через управляюгдий вход 82. Узел 79 выполняет три различных способа формирования адреса микрокоманд: непосредственное задание адреса микрокоманды

0

5

блока 80. постоянной памяти с управляющего входа 82 (переход по абсолютному адресу); инкремент адреса (последовательный перебор адресов постоянного запоминающего устройства 80 (адрес адрес + 1); переход по стеку (возврат из микропрограммы)

По сигналу синхронизации, который поступает на вход узла 79 через вход 84 синхронизации, формируется адрес, который с выхода узла 79 поступает на вход блока 80 постоянной памяти, в котором хранятся микрокоманды. Каждая микрокоманда содержит дополнительные биты, предназначенные для выборки из блока 80 памяти следующей микрокоманды, Микрокоманда содержит несколько полей. Сигналы поля третьего и четвертого выходов блока 80 по- стоянной памяти указывают, где находится следующий адрес: на управляющем входе 82, на выходе сумматора инкремента адресов или на стеке, С помощью мультиплексора 78 можно осуществлять условные и безусловные микропрограммные действия. С помощью входа, соединенного с входом 83 управления, мультиплексор 78 осуществляет выбор функции, поступающей по его второму или третьему входу. Сигнал поля второго выхода блока 80 постоянной памяти указывают адрес безусловного перехода иди адрес микропрогра- мы. Сигналы поля первого выхода блока 80 памяти поступают на вход ре- гистра 81, Его разрядность соответствует разрядности микрокоманда.1, выбираемой из данного поля.

Блок 7 формирования адреса состоит из двух одинаковьгх генераторов, один из которы5с обеспечивает формирование адресов строк и столбцов памяти узловых напряжений, а другой обеспечивает формирование адресов строк стол бцов памяти параметров среды. По шине 99 в блок 7 записываются начальные адреса рабочей области. По входу управления 96 на управляющие . входы сумматоров 87, 89, 92 и 94 подаются управляющие константы, а также задается режим работы регистров . 86, 88, 91 и 93 адресов , Дпя смены адреса строки си столбца необходимо : семь тактов синхронизации, которые осуществляют последовательно суммирование кода управляющей контстанты с текущим адресом, содержащимся в регистрах адресов. По истечении семи

синхротактов в адресных регистрах сформированы новые адреса стр ок и столбцов. Сформированные адреса поступают на входы мультиплексоров 90 и 95 и через них на адресные шины обоих блоков памяти. Вначале подаются адреса строк выбираемых ячеек, затем на те же адресеные шины задаются адреса столбцов.

Форм у л а изобретения

5

0

0

1, Устройство ДПЯ решения урав5 нений математической физики, содержащее блок памяти узловых напряжений и модель узла сеточной области, отличающее ся тем, что, с целью увеличения быстродействия и точности решения, оно содержит блок управления, блок памяти констант, блок итераций, блок контроля вычисления, регистр, блок памяти парамет- ров среды, блок формлрования адресов и генератор тактовых импульсов, при- чем выходы с первого по четвертый блока управления подключены соответственно к входу чтения-записи ре- гистра, к управляющему входу блока памяти узловых напряжений, к входам чтения-записи блока памяти, констант и блока памяти параметров среды, первый и второй выходь первой группы, с первого по четвертый выходы

5 второй группы, выходы с первого по десятый третьей группы блока управления подключены соответственно к управляющим входам первого и второго блоков итераций, к управляющим входам с первого по четверый блока контроля вычислений и к управляющим входам с первого по десятьй блока формирования адреса, выходь с перво- го по седьмой четвертой группы блока управления подключены соответственно- к управляющим входам с первого по седьмой модели зла сеточной области, информационный вход начальных приближений устройства подключен к

0 первому) информационному входу регистра, выход которого подключен к информационному входу блока памяти узловых напряжений, к информационным входам блока формирования адре5 са, блока памяти параметров среды и блока памяти констант, первый и второй выходы которого подключены соответственно к первым информационным входам соответственно блока итераций

0

5

и блока контроля вычислений, первый, второй, и третий выходы которого подключены; соответственно к входу режима блока управления, к второму и третьему информационным входам блока итераций, выход которого подключен к второму информационному входу регистра, выход генератора тактовых импульсов подключен к синхровхо- дам регистра, блока памяти узловых напряжений, блока формирования адреса, блока памяти параметров среды, модели узла сеточной области, блока контроля вычислений, блока памяти констант и блока управления, вход команды которого подключен к входу команды устройства, выход блока памяти узловых напряжений подключен к второму информационному входу блока констант вычислений, к первому информационному входу модели узла сеточной области и к выходу результата устройства, первый выход блока фор- . мирования адреса подключен к адресным входам блока памяти узловых , пряжений и модели узла сеточной области, второй выход - к адресному входу блока памяти параметров среды, выход которого подключен к второму информационному вхо ду модели узла сеточной области, выход которой подключен к Третьему информационному входу блока контроля вычислений, входы с первого по четвертый границ сеточной области устройства-подключены соответственно к информационным бходам с третьего по шестой модели .узла сеточной области,

2, Устройство по п.1, о т ли - чающееся тем, что модель узЛа сеточной области содержит пять умножителей, два сумматора, первую rijynny из семи регистров, вторую группу из четырех регистров, узел границ моделируемой области, с первого по третий регистры и узел деле- . ния, причем управляющие входы с первого по четвертый модели узла сеточной области подключены соответственно к входам с первого по четвертый узла границ моделируемой области управляющие входы с пятого по седьмой модели узла сеточной области подключены к входам чтения-записи регистров с первого по третий первой группы и регистров с первого по третий, адресный первый информационный и второй информационный входы модели

сеточной области подключены соответственно к пятому входу узла границ моделируемой области, к информацион- ным входам регистров первой и второй

г.

групп, выходы с первого по девятый узел границ моделируемой области подключены соответственно к входам чтения-записи соответственно регист- . ров с четвертого по седьмой первой группы и с первого по четвертый второй группы, синхровход модели узла сеточной области подключен к синх- ровходам регистров с первого по третий, первого и второго сумматоров, умножителей с первого по пятый, регистров первой и второй групп,-информационный выход первого сумматора подключен к информационному входу

первого регистра, . выход которого - подключен к первому входу узла деления, информационный выход второго сумматора подключен к информационному входу второго регистра,

выход которого подключен к второму входу узла деления, информационный выход которого подключен к информационному входу третьего регистра, выход которого подключен к выходу модели узла сеточной области, выходы первого, четвертого, пятого, шестого и седьмого регистров первой группы подключены соответственно к первым входам умножителей с первого по пятый и к входам с первого по пятый второ.го сумматора, выходы второго и третьего регистров первой группы подключены соответственно к второму входу пятого умножителя и к первому

входу первого сумматора, выходы регистров с первого по четвертый второй группы подключены к вторым входам соответственно умножителей с первого по четвертый, информационные выходы

умножителей с первого по пятый подключены соответственно к входам с второго по шестой первого сумматора, с третьего по. шестой информационные .входы модели узла сеточной области

подключены к входам с шестого по девятый узла границ сеточной области, при этом узел границ моделируемой области содержит четыре элемента И и четыре элемента сравнения, с перво55

го по четвертый входы узла границ моделируемой области подключены соответственно к первым входам элементов И с первого по четвертый, пятый вход узла грашщ моделируемой области

подключен к первым входам элементов сравнения с первого по четвертый, входы с шестого по девятый узла границ моделируемой области подключен к вторым входам соответственно элементов сравнения с первого по чет вертый, выходы которых подключены соответственно к вторым входам элементов И с первого по четвертый, инверсные выходы которых подключены соответственно к выходам с первого по четвертый узла границ моделируемой области, прямые выходы элемен-, тов И с первого по четвертый подключены соответственно к выходам с пятого по восьмой узла границ моделируемой области,

3, Устройство поп,1,отли-

тем, что блок управ-20 мационным входам второго мультиплекчаюцеесяления содержит мультиплексор, узел постоянной памяти, узел подготовки адреса микрокоманды и регистр, причем первый выход узла постоянной памяти подключен к информационному входу регистра, второй выход объединен с входом команды блока и под- к информационному входу узла подготовки адреса микрокоманды, выход которого подключен к адресному входу узла постоянной памяти, третий и четвертый выходы которого подключены соответственно к первому и второму информационным входам мультиплексора, выход которого подключен к управляющему входу узла подготовки адреса микрокоманды, вход режима . блока подключен к управляющему входу мультиплексора, синхровход - к входу синхронизации узла подготовки адреса микрокоманда и к входу чтения регистра, выходы которого подключены,соответственно к выходам блокад

4, Устройство по П.1, о т л и - ча1рщееся тем, .что блок (формирования адреса содержит четыре .регистра, четыре сумматора и два мультиплексора, причем управляющие входы с первого по десятый блока подключены соответственно к управляющим входам первого и второго мультиплексоров, к управляющим входам регистров с первого по четвертый и к входам синхронизации сумматоров с первого по четвертый, информационньй вход блока подключен к первым информационным входам регистров с первого по четвертый, вход синхронизации - к первым информационным входам сумсора, выход которого подключен втором выходу блока.

к

25

30

5. Устройство по П.1, о т л и - чающееся тем, что блок контроля вычислений содержит регистр, регистр невязки, регистр знака невязки, два сумматора и триггер, причем первый, второй и третий информа- ционньш входы блока подключены соответственно к первому информационному входу первого сумматора, к информационному входу регистра и к первому информадионному входу второго сумма25 тора, вход синхронизации блока подключен к входам синхронизации регистра, регистра невязки, регистра знака невязки, первого и второго сумматоров и триггера, управляющие вхо40 Ды с первого по четвертый блока подключены соответственно к входам записи регистра, считывания регистра, записи регистра невязки и записи регистра знака невязки, выход переноса

45 первого сумматора подключен к информационному входу триггера, выход которого подключен к первому выходу блока, выход регистра подключен к второму информационному входу второго

50 сумматора и второму выходу блока, информационный второго сумматора подключен к информационным входам: регистра невязки, регистра знака невязки и к третьему выходу

gc блока, выходы регистра невязки и регистра знака невязки подключены соответственно к второму информационному входу и к знаковому входу первого

.сумматора.

маторов с первого по четвертый и к входам синхронизации регистров с первого по четвертый, первые выходы регистров с первого по четвертый подключены соответственно к вторым информационным входам сумматоров с первого по четвертый, информационные выходы которых подключены соответственно к вторым информационным входам регистров с первого по четвертый, вторые выходы первого и второго регистров подключены соответственно к первому и второму информационным

входам первого мультиплексора, выход которого подключен к первому выходу блока, вторые выходы третьего и четвертого регистров подключены соответственно к первому и второму инфорсора, выход которого подключен втором выходу блока.

к

5. Устройство по П.1, о т л и - чающееся тем, что блок контроля вычислений содержит регистр, регистр невязки, регистр знака невязки, два сумматора и триггер, причем первый, второй и третий информа- ционньш входы блока подключены соответственно к первому информационному входу первого сумматора, к информационному входу регистра и к первому информадионному входу второго сумматора, вход синхронизации блока подключен к входам синхронизации регистра, регистра невязки, регистра знака невязки, первого и второго сумматоров и триггера, управляющие вхоДы с первого по четвертый блока подключены соответственно к входам записи регистра, считывания регистра, записи регистра невязки и записи регистра знака невязки, выход переноса

первого сумматора подключен к информационному входу триггера, выход которого подключен к первому выходу блока, выход регистра подключен к второму информационному входу второго

сумматора и второму выходу блока, информационный второго сумматора подключен к информационным входам: регистра невязки, регистра знака невязки и к третьему выходу

блока, выходы регистра невязки и регистра знака невязки подключены соответственно к второму информационному входу и к знаковому входу первого

сумматора.

6. Устройство по п,1, о тл и - чающееся тем, что,блок итераций содержит умножитель, элемент задержки и сумматор, причем первый, второй и третий информационные входы блока подключены соответственно к входу элемента задержки, к первому и второму информационным входам умно жителя, первый и второй управляющие входы блока подключены к входам раз

решения умножителя и сумматора, вход синхронизации блока подключен к входам синхронизации умножителя, сумматора и элемента задержки, выхоДы элемента задержки и умножителя подключены соответственно к первому и второму информационным входам сумматора, выход которого подключен к выходу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для расчета режимов трубопроводных сетей | 1981 |

|

SU1007111A1 |

| Устройство для решения нелинейных задач теплопроводности | 1986 |

|

SU1363269A1 |

| Устройство для задания граничных условий | 1981 |

|

SU991447A1 |

| Узловой элемент цифровой сетки для решения краевых задач теории поля | 1985 |

|

SU1283788A1 |

| Устройство для вычисления параметров сеток для решения разностных уравнений | 1986 |

|

SU1413642A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1979 |

|

SU781840A1 |

Изобретение относится к вычислительной технике и может быть использовано как автономно, так ив качестве процессора для универсальной ЦВМ. Цель изобретения - повышение быстродействия и точности решения. Поставленная цель достигается тем, что устройство содержит модель 1 узла сеточной области, блок 2 памяти параметров среды, блок 3 памяти узловых напряжений, блок 4 памяти констант, блок 5 формирования адреса, блок 6 итераций, блок 7 контроля вы- числений, блок 8 управления, регистр , 9, генератор 10 тактовых импульсов, 5 з.п. ф-лы, 7 ил. i (Л со о:) GO N3 О5

39 W

52 (D

&

53

(1) -

5

С

5

Физ.З

Фие.

{З)т

llL

6tf

Й

43)

65

Л)

(11

dl)

(21

66

(1)

/ ч

15

76

72

(31

67

7J

W

Л

М

(3)

SS

21

7f

Фиг. 5

ЖХ

(3)

78

W(2)

V

|(jj||(j llfr;

8

(21

/

(2)

(2}

. i

79

Щ

m81

8S

фиг.6

| УСТРОЙСТВО для РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИИ | 0 |

|

SU323782A1 |

| Устройство для решения уравнения теплопроводности | 1974 |

|

SU494751A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-29—Подача